Improving Design Efficiency for Large-Scale Heterogeneous Circuits

Ву

## **Anthony Gregerson**

A dissertation submitted in partial fulfillment of the requirements for the degree of

**Doctor of Philosophy**

(Electrical Engineering)

at the

UNIVERSITY OF WISCONSIN-MADISON

2015

Date of final examination: 4/10/2015

The dissertation is approved by the following members of the Final Oral Committee:

Katherine L. Morrow, Associate Professor, Electrical & Computer Engineering

Azadeh Davoodi, Associate Professor, Electrical & Computer Engineering

Nam Sung Kim, Associate Professor, Electrical & Computer Engineering

Parameswaran Ramanathan, Professor, Electrical & Computer Engineering

Eric Bach, Professor, Computer Science

# **ACKNOWLEDGEMENTS**

This work would not have been possible without the continual support, patience, and friendship of my advisor, fellow graduate students, and family. I would like to thank all those who challenged me to be a better researcher, teacher, and student during my time at the University of Wisconsin.

# **ABSTRACT**

Despite increases in logic density, many Big Data applications must still be partitioned across multiple computing devices in order to meet their strict performance requirements. Among the most demanding of these applications is high-energy physics (HEP), which uses complex computing systems consisting of thousands of FPGAs and ASICs to process the sensor data created by experiments at particles accelerators such as the Large Hadron Collider (LHC). Designing such computing systems is challenging due to the scale of the systems, the exceptionally high-throughput and low-latency performance constraints that necessitate application-specific hardware implementations, the requirement that algorithms are efficiently partitioned across many devices, and the possible need to update the implemented algorithms during the lifetime of the system.

In this work, we describe our research to develop flexible architectures for implementing such large-scale circuits on FPGAs. In particular, this work is motivated by (but not limited in scope to) high-energy physics algorithms for the Compact Muon Solenoid (CMS) experiment at the LHC. To make efficient use of logic resources in multi-FPGA systems, we introduce Multi-Personality Partitioning, a novel form of the graph partitioning problem, and present partitioning algorithms that can significantly improve resource utilization on heterogeneous devices while also reducing inter-chip connections. To reduce the high communication costs of Big Data applications, we also introduce Information-Aware Partitioning, a partitioning method that analyzes the data content of application-specific circuits, characterizes their entropy, and selects circuit partitions that enable efficient compression of data between chips. We employ our information-aware partitioning method to improve the performance of the hardware validation platform for evaluating new algorithms for the CMS experiment.

Together, these research efforts help to improve the efficiency and decrease the cost of the developing large-scale, heterogeneous circuits needed to enable large-scale application in high-energy physics and other important areas.

# TABLE OF CONTENTS

|    | Abstrac                                                                           |                                                                                                     | ii    |  |

|----|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-------|--|

| 1. | Introduc                                                                          | tion                                                                                                | 1     |  |

|    | 1.1.                                                                              | Motivation                                                                                          | 1     |  |

|    | 1.2.                                                                              | Objectives and Contributions                                                                        | 2     |  |

|    | 1.3.                                                                              | Document Organization                                                                               | 5     |  |

| 2. | Backgro                                                                           | und                                                                                                 | 7     |  |

|    | 2.1.                                                                              | Field Programmable Gate Arrays (FPGAs)                                                              | 7     |  |

|    | 2.2.                                                                              | Processing and Data Acquisition for High Energy Physics                                             | 8     |  |

|    | 2.3.                                                                              | Graph Partitioning                                                                                  | 9     |  |

|    | 2.3.1                                                                             | . Homogeneous Hypergraph Partitioning                                                               | 9     |  |

|    | 2.3.2                                                                             | . Heterogeneous Hypergraph Partitioning                                                             | 10    |  |

|    | 2.4.                                                                              | Multi-Gigabit Serial Data Transmission                                                              | 11    |  |

|    | 2.5.                                                                              | Information Content in Digital Signals                                                              | 12    |  |

|    | 2.5.1                                                                             | . Quantifying Information                                                                           | 12    |  |

|    | 2.5.2                                                                             | . Entropy in Digital Systems                                                                        | 13    |  |

|    | 2.5.3                                                                             | Other Information Measurement Metrics                                                               | 15    |  |

| 3. | Mixed-Granularity Reconfigurable Architectures for High Energy Physics Processing |                                                                                                     |       |  |

|    | 3.1.                                                                              | Motivation                                                                                          |       |  |

|    | 3.2.                                                                              | Related Work                                                                                        |       |  |

|    | 3.3.                                                                              | Characterizing Calorimetry-Based L1 Triggering Algorithms                                           |       |  |

|    | 3.3.1                                                                             |                                                                                                     |       |  |

|    | 3.3.2                                                                             |                                                                                                     | netei |  |

|    | 3.4.                                                                              | Proposed Architectures                                                                              |       |  |

|    | 3.4.1                                                                             | Direct Arithmetic Logic Implementations (LUT-Based, DSP-Based, Hybrid LUT-DSP)                      |       |  |

|    | 3.4.2                                                                             | Compressed Coarse-Grained Look-up Operations (Compressed LUT and Multi-Level Compressed BRAM Table) |       |  |

|    | 3.5.                                                                              | Base Implementation Costs                                                                           | 38    |  |

|    | 3.6.                                                                              | Cost Stability Analysis                                                                             | 40    |  |

|    | 3.7.    | Analysis of Implementations                                  | 43 |

|----|---------|--------------------------------------------------------------|----|

|    | 3.8.    | Contributions.                                               | 44 |

| 4. | Multi-P | ersonality Graph Partitioning for Heterogeneous Resources    | 45 |

|    | 4.1.    | Motivation                                                   |    |

|    | 4.2.    | Multi-Personality Partitioning Problem Definition            | 47 |

|    | 4.3.    | Manipulating Resource Utilization                            |    |

|    | 4.4.    | Related Work                                                 | 49 |

|    | 4.5.    | Benchmark Development                                        | 52 |

|    | 4.5.1   | HDL-Based Benchmark Development                              | 53 |

|    | 4.5.2   | 2. CHACO Benchmark Graphs                                    | 55 |

|    | 4.6.    | Multi-Personality Brute-Force Algorithm                      | 56 |

|    | 4.7.    | Multi-Personality Integer Programming                        | 56 |

|    | 4.7.1   | Personality and Partition Selection Constraints              | 57 |

|    | 4.7.2   | 2. Resource Constraints                                      | 58 |

|    | 4.7.3   | 3. Objective Function                                        | 58 |

|    | 4.7.4   | 4. Computational and Spatial Complexity                      | 59 |

|    | 4.8.    | KLFM-Based Partitioning Algorithm Design                     | 60 |

|    | 4.8.    | Base KLFM Algorithm                                          | 60 |

|    | 4.8.2   | 2. Multi-Personality KLFM                                    | 61 |

|    | 4.8.3   | B. Deadlock Prevention for Multi-Personality Graphs          | 63 |

|    | 4.8.4   | 1. Dynamic Gain Buckets                                      | 64 |

|    | 4.8.5   | 5. Pass-Level Implementation Remapping                       | 67 |

|    | 4.8.6   | 6. Multi-Level Partitioning                                  | 68 |

|    | 4.9.    | Implementing the Multi-Personality Partitioning Algorithms   | 70 |

|    | 4.9.1   | Partitioning Algorithms Using Static Personality Mapping     | 71 |

|    | 4.9.2   | 2. Partitioning Algorithms Using Dynamic Personality Mapping | 72 |

|    | 4.10.   | Results                                                      | 74 |

|    | 4.10    | .1. Integer-Linear Programming                               | 74 |

|    | 4.10    | .2. Evaluating KLFM Parameters                               | 76 |

|    | 4.10    | .3. Performance Validation of Base KLFM Algorithm            | 77 |

|    | 4.10    | .4. Cut Size Results for KLFM-Based Algorithms               | 78 |

|    | 4.10    | .5. RUR Deviation Results for KLFM-Based Algorithms          | 79 |

|    | 4.10    | .6. Run-Time Cost                                            | 80 |

|    | 4.10    | 0.7. Comparison of Pareto Optimality                                                             |

|----|---------|--------------------------------------------------------------------------------------------------|

|    | 4.11.   | Performance Consistency of KLFM Algorithms                                                       |

|    | 4.12.   | Contributions                                                                                    |

| 5. | Informa | ation-Aware Partitioning84                                                                       |

|    | 5.1.    | Motivation                                                                                       |

|    | 5.2.    | Related Work                                                                                     |

|    | 5.3.    | Entropy in Digital Logic Circuits                                                                |

|    | 5.3.    | 1. Low-Entropy Input Data                                                                        |

|    | 5.3.    | 2. Non-Reversible Computations                                                                   |

|    | 5.3.    | 3. Redundancy / Reduction in Boolean Complexity                                                  |

|    | 5.4.    | Entropy-Based Partitioning in the Regional Calorimeter Trigger                                   |

|    | 5.5.    | Benchmarks for Information Partitioning                                                          |

|    | 5.5.    | 1. Benchmarks and Data Sets                                                                      |

|    | 5.6.    | Entropy-Aware Partitioning Results for All Benchmarks                                            |

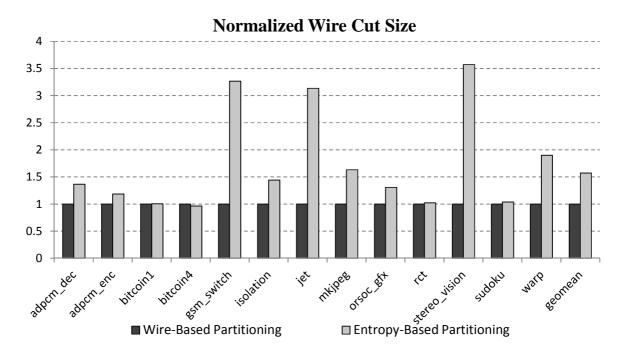

|    | 5.6.    | 1. Wire Cut Size Results                                                                         |

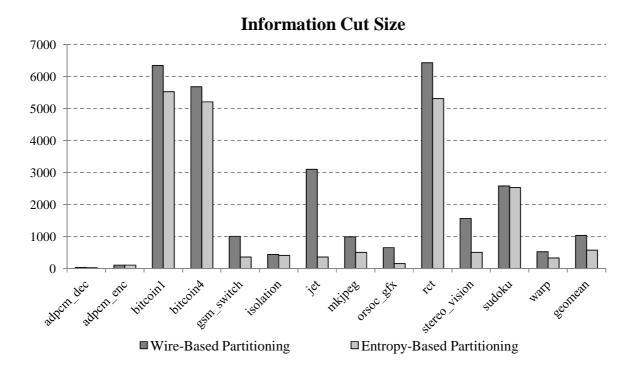

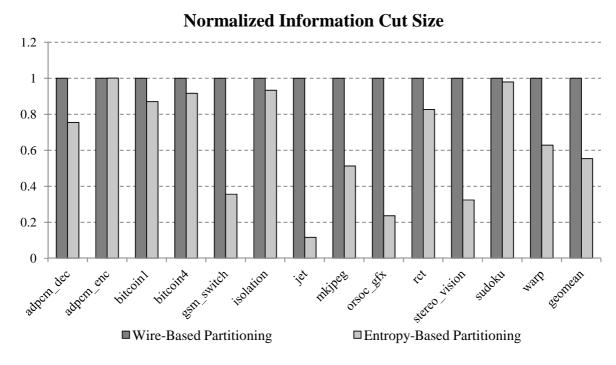

|    | 5.6.    | 2. Information Cut Size Results                                                                  |

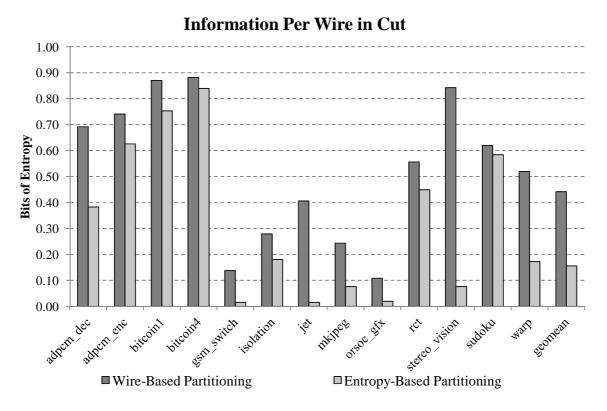

|    | 5.6.    | 3. Information Density Results                                                                   |

|    | 5.6.    | 4. Maximum Theoretical Compression Factors                                                       |

|    | 5.6.    | 5. Discussion                                                                                    |

|    | 5.7.    | Methods for Collecting Entropy Data in Circuits                                                  |

|    | 5.7.    | 1. Evaluating Entropy Estimation Methods                                                         |

|    | 5.7.    | 2. Structural Estimation 113                                                                     |

|    | 5.7.    | 3. Input-Based Estimation                                                                        |

|    | 5.7.    | 4. Functional Simulation-Based Estimation                                                        |

|    | 5.7.    | 5. State-Sampled Functional Simulation-Based Estimation                                          |

|    | 5.7.    | 6. Impact of Entropy Accuracy on Partitioning                                                    |

|    | 5.7.    | 7. Summary of Entropy Estimation Methods                                                         |

|    | 5.8.    | Application Case Study: Entropy-Based Partitioning in the CMS Level-1 Trigger Emulator Prototype |

|    | 5.8.    | 1. Prototype Architecture                                                                        |

|    | 5.8.    | 2. Implementing Compression                                                                      |

|    | 5.8.    | 3. Temporal Entropy Variation                                                                    |

|    | 5.8.    | 4. Synchronous L1TE with Bounded Transmission Time                                               |

|      | 5.8.5.      | Asynchronous L1TE with Bounded Bandwidth                                    |

|------|-------------|-----------------------------------------------------------------------------|

|      | 5.8.6.      | Inexact Synchronous Operation                                               |

|      | 5.8.7.      | Summary of L1TE Case Study                                                  |

|      | 5.9. Co     | ontributions                                                                |

| 6.   | Future Dir  | ections14                                                                   |

| 7.   | Conclusion  | 1150                                                                        |

| 8.   | Publication | ns                                                                          |

| 9.   | Appendix    | A: A Brief History of HEP Triggering Systems153                             |

|      | 9.1. Ea     | urly Trigger Systems                                                        |

|      | 9.2. Tr     | rigger Systems of the 1980s                                                 |

|      | 9.2.1.      | Axial Spectrometer Experiment at the Intersecting Storage Rings (1971 1984) |

|      | 9.2.2.      | The CDF Experiment at the Tevatron (ca. 1987)                               |

|      | 9.2.3.      | The DELPHI and L3 Experiments at the Large Electron-Positron Ring (ca 1989) |

|      | 9.3. Ti     | igger Systems of the 1990s                                                  |

|      | 9.3.1.      | The SLD Experiment at the SLAC Linear Collider (ca. 1991)                   |

|      | 9.3.2.      | The NA48, WA98, and NOMAD Experiments at the SPS (ca. 1992-1997             |

|      | 9.3.3.      | The BaBar Experiment at the PEP-II Collider (ca. 1999)                      |

|      | 9.4. Tı     | igger Systems of the 2000s                                                  |

|      | 9.4.1.      | The H1 Experiment at the upgraded-luminosity HERA Accelerator (ca 2001)     |

|      | 9.4.2.      | Upgrades to the CDF Experiment for Tevatron Run-II (ca. 2001)               |

|      | 9.4.3.      | The CDF Upgrade for Tevatron Run-IIb (ca. 2005)                             |

|      | 9.4.4.      | The ATLAS, CMS, and LHCb Experiments at the Large Hadron Collide (ca. 2009) |

|      | 9.5. Tr     | ends in Future Trigger Design                                               |

| 10   | Bibliograp  | hy18                                                                        |

| - 0. | p           |                                                                             |

# LIST OF FIGURES

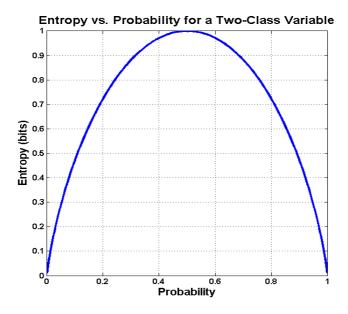

| FIGURE 1. ENTROPY (IN BITS) VERSUS PROBABILITY OF HAVING A VALUE OF '1' FOR A BINARY VARIABLE                                                                                                                                                                                                                                                  | 14    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

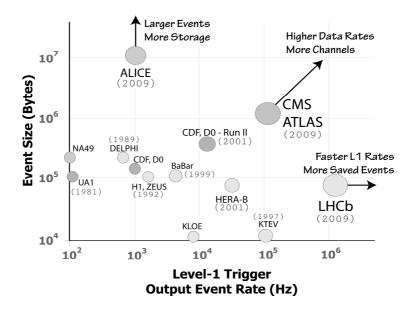

| FIGURE 2. THE REQUIRED THROUGHPUT OF TRIGGER SYSTEMS HAS BEEN INCREASING EXPONENTIALLY OVER TIME                                                                                                                                                                                                                                               | 18    |

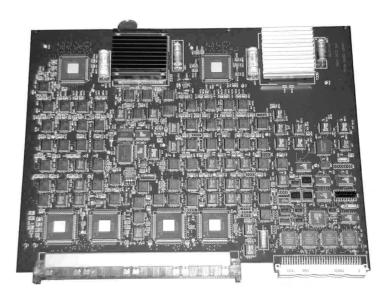

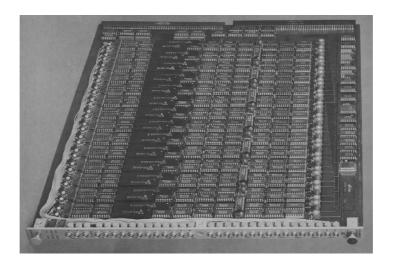

| FIGURE 3. ONE OF 126 BOARDS USED FOR PROCESSING CALORIMETER TRIGGER ALGORITHMS IN THE ORIGINAL CM. TRIGGER. THE OVERALL SYSTEM IS PARTITIONED ACROSS OVER 700 FPGAS AND ASICS AND THOUSANDS O RAM-BASED LUTS.                                                                                                                                  | F     |

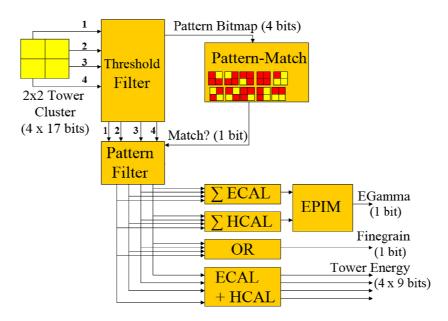

| FIGURE 4. A COMPARISON OF A SIMPLE, FULL LOOK-UP TABLE FOR THE EPIM (A) WITH A TWO-LEVEL COMPRESSED LOOK-UP TABLE (B) USING CALORIMETER ENERGY READINGS (ECAL & HCAL) AS INPUTS                                                                                                                                                                |       |

| FIGURE 5. A SECTION OF THE DATAPATH FOR PERFORMING ELECTROMAGNETIC/HADRONIC PARTICLE IDENTIFICATION THE CMS REGIONAL CALORIMETER TRIGGER.                                                                                                                                                                                                      |       |

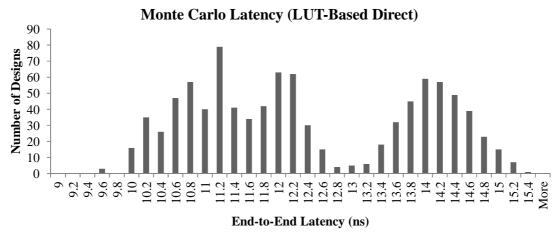

| FIGURE 6. HISTOGRAM OF END-TO-END LATENCY REQUIREMENTS FOR RANDOMLY PARAMETERIZED INSTANCES OF THE LUT-BASED DIRECT DESIGN FOR THE ELECTRON/PHOTON ID (EPIM) ALGORITHM.                                                                                                                                                                        |       |

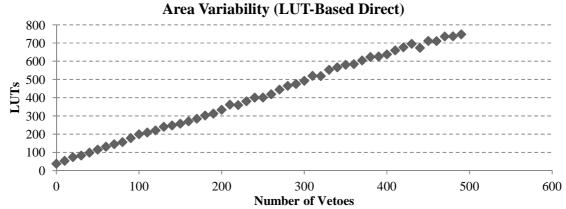

| FIGURE 7. TOTAL LUT REQUIREMENTS VERSUS NUMBER OF ENERGY VETOES BASED ON MONTE CARLO SIMULATION OF EPIM IMPLEMENTATION COSTS.                                                                                                                                                                                                                  |       |

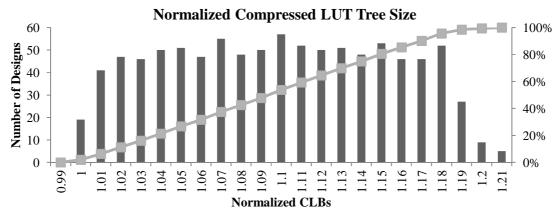

| FIGURE 8. HISTOGRAM OF THE NORMALIZED SIZE (IN CLBS) OF THE MONTE CARLO GENERATED LUT TREES FOR TEPIM AFTER TREE COMPRESSION. VALUES ARE NORMALIZED TO THE BASE IMPLEMENTATION WITHOUT VET THE LINE INDICATES THE CUMULATIVE PERCENTAGE OF MONTE CARLO SAMPLES THAT COULD FIT IN THAT NUMBER OF CLBS.                                          | OES.  |

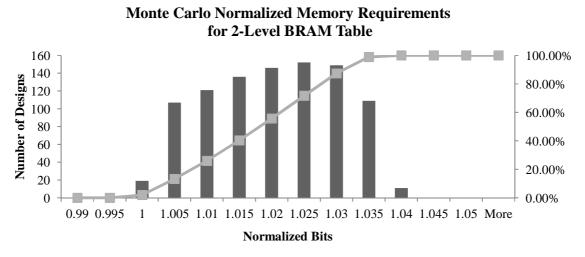

| FIGURE 9. HISTOGRAM OF THE SIZE OF THE MONTE CARLO GENERATED EPIMS CONVERTED TO MEMORY IMAGES MAPPING TO A LOOK-UP TABLE AND COMPRESSED WITH THE LZW ALGORITHM. VALUES ARE NORMALIZED THE BASE IMPLEMENTATION WITHOUT VETOES.                                                                                                                  | ГО    |

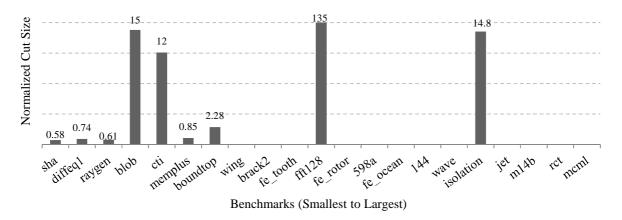

| FIGURE 10. CUT SIZES FOR ILP-BASED PARTITIONING WITH A RUN TIME OF 48 HOURS, NORMALIZED TO MF STATICALLY-MAPPED PARTITIONING. MISSING BARS INDICATE THAT ILP COULD NOT FIND A SOLUTION                                                                                                                                                         | 74    |

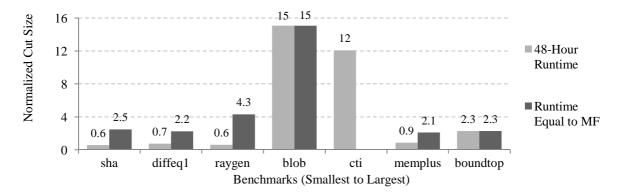

| Figure 11. ILP cut sizes (normalized to MF) for graphs with less than $30,000$ nodes for different amounts of runtime. ILP was unable to find a solution for cti when given runtime equal to M.                                                                                                                                                | F. 75 |

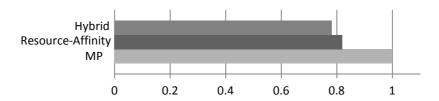

| FIGURE 12. AVERAGE OF THE CUT SIZE RESULTS FOR ALL BENCHMARK GRAPHS USING DMP AND DIFFERENT GAIN BUCKET TYPES, NORMALIZED TO THE MULTI-PERSONALITY (MP) BUCKET TYPE. LOWER VALUES ARE BETTE                                                                                                                                                    |       |

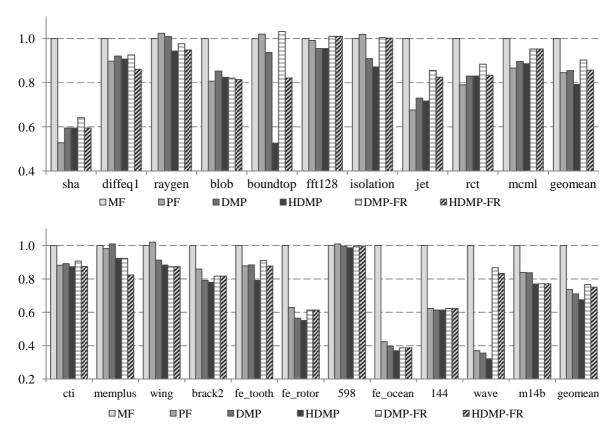

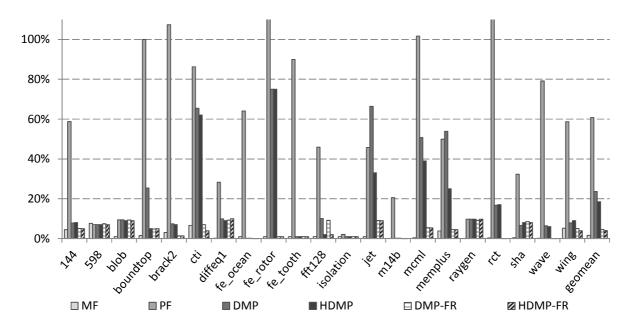

| FIGURE 13. CUT SIZE RESULTS FOR KLFM-BASED PARTITIONERS, NORMALIZED TO MAP-FIRST, AND PRESENTED SEPARATELY FOR HDL-DERIVED GRAPHS AND GRAPHS FROM PARTITIONING BENCHMARK SETS                                                                                                                                                                  | 79    |

| FIGURE 14. RUR DEVIATION RESULTS FOR ALL BENCHMARKS. LOWER VALUES ARE BETTER                                                                                                                                                                                                                                                                   | 80    |

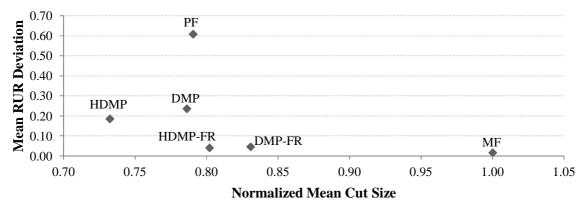

| FIGURE 15. PARETO COMPARISON OF CUT SIZE VS. RUR DEVIATION FOR ALL KLFM-BASED PARTITIONERS                                                                                                                                                                                                                                                     | 81    |

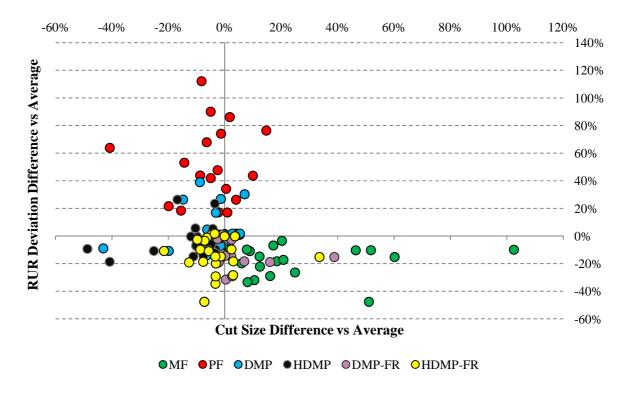

| FIGURE 16. PERFORMANCE CONSISTENCY OF THE MULTI-PERSONALITY KLFM ALGORITHMS. EACH POINT REPRESS A SINGLE BENCHMARK AND THE ALGORITHM'S RELATIVE PERFORMANCE (IN TERMS OF RUR DEVIATION AND CUT SIZE) RELATIVE TO THE AVERAGE RESULT OF ALL ALGORITHMS ON THAT BENCHMARK. FOR BOTH PERFORMANCE METRICS, LOWER (MORE NEGATIVE) VALUES ARE BETTER | )     |

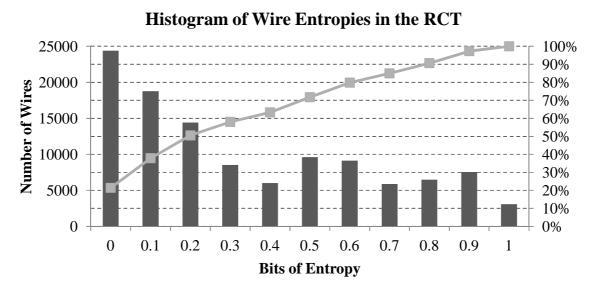

| FIGURE 17. HISTOGRAM OF THE BITS OF SHANNON ENTROPY PER WIRE IN A SUBSECTION OF THE RCT, MEASURED DURING POST-SYNTHESIS SIMULATION. THE LINE REPRESENTS THE CUMULATIVE PERCENTAGE OF WIRES (AS LABELED ON THE RIGHT AXIS) THAT HAVE AT LEAST THE AMOUNT OF ENTROPY INDICATED ON THE Y AXIS                                                     | \$    |

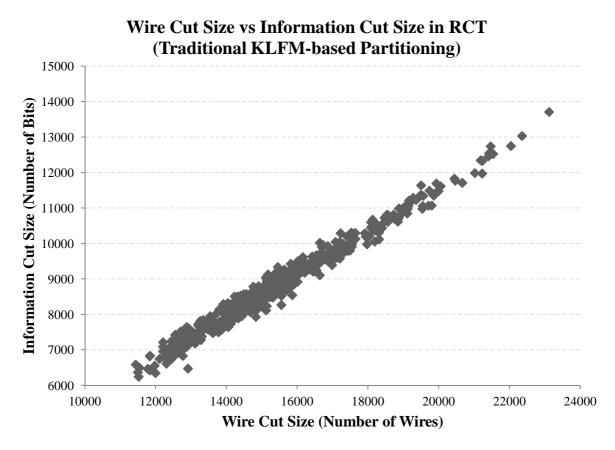

| FIGURE 18. PLOT OF WIRE CUT SIZE VERSUS INFORMATION CUT SIZE IN THE RCT FOR 500 RUNS OF A KLFM ALGORITHM USING A TRADITIONAL WIRE-MINIMIZATION OBJECTIVE FUNCTION                                                                                                                                                                              | 93    |

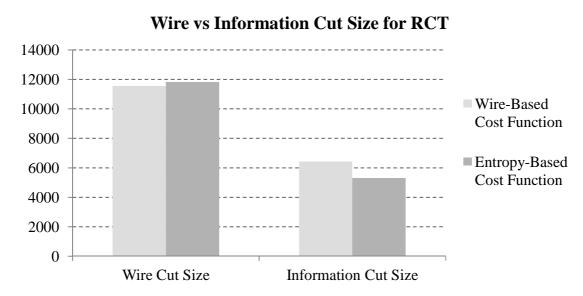

| FIGURE 19. WIRE CUT SIZE VS. INFORMATION CUT SIZE IN THE RCT WHEN USING KLFM ALGORITHMS WITH WIRE BASED AND ENTROPY-BASED COST FUNCTIONS.                                                                                                                                                                                                      |       |

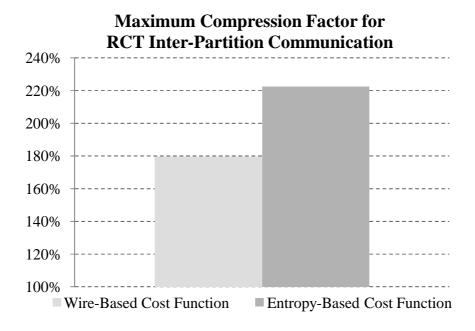

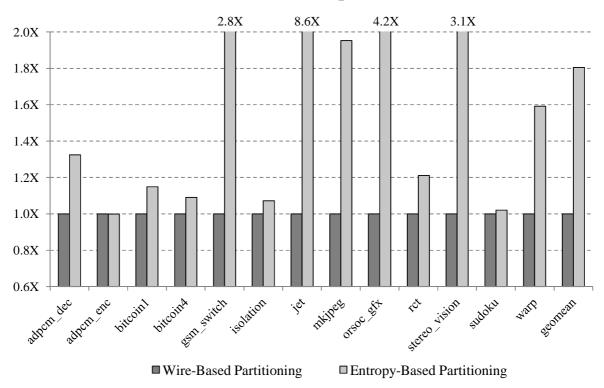

| FIGURE 20. THE MAXIMUM LOSSLESS COMPRESSION FACTOR ACHIEVABLE FOR COMPRESSION USING ENTROPY COLON INTER-PARTITION CUTS PRODUCED BY WIRE-BASED PARTITIONING AND ENTROPY-BASED PARTITIONING.                                                                                                                                                     |       |

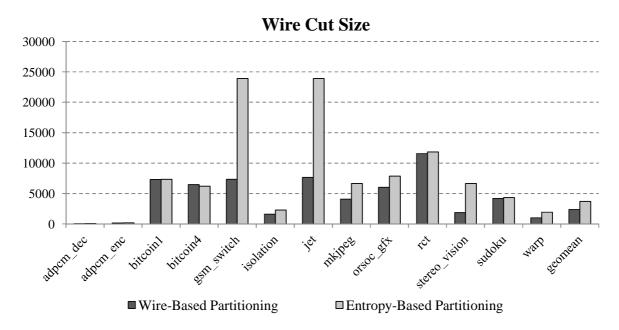

| FIGURE 21. ABSOLUTE WIRE CUT SIZES USING WIRE-BASED AND ENTROPY-BASED PARTITIONING.                                                                                                                                                                                                                                                            | 101   |

| FIGURE 22. NORMALIZED WIRE CUT SIZES USING WIRE-BASED AND ENTROPY-BASED PARTITIONING.                                                                                                                                                                                                                                                          | 102   |

| FIGURE 23. ABSOLUTE INFORMATION CUT SIZES FOR WIRE-BASED AND ENTROPY-BASED PARTITIONING                                                                                                                                                                                                                                                        | 103   |

| $FIGURE\ 24.\ NORMALIZED\ INFORMATION\ CUT\ SIZES\ FOR\ WIRE-BASED\ AND\ ENTROPY-BASED\ PARTITIONING104$                                                                                                                                                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

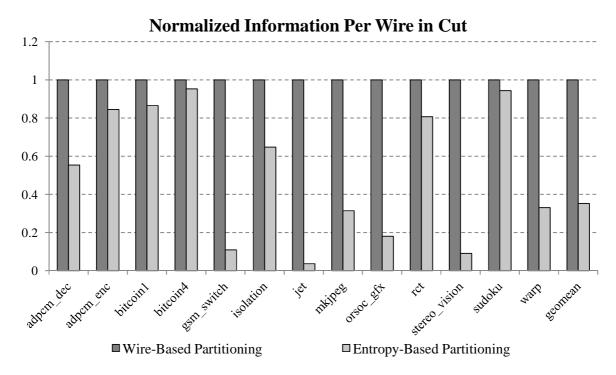

| FIGURE 25. INFORMATION, IN TERMS OF BITS OF SHANNON ENTROPY PER WIRE FOR WIRE-BASED AND ENTROPY-BASED PARTITIONING                                                                                                                                                   |

| FIGURE 26. NORMALIZED INFORMATION, IN TERMS OF BITS OF SHANNON ENTROPY PER WIRE FOR WIRE-BASED AND ENTROPY-BASED PARTITIONING                                                                                                                                        |

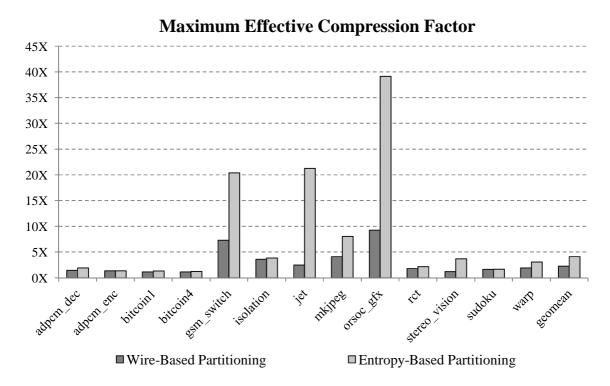

| FIGURE 27. ABSOLUTE MAXIMUM EFFECTIVE COMPRESSION FACTORS FOR WIRE-BASED AND ENTROPY-BASED PARTITIONING                                                                                                                                                              |

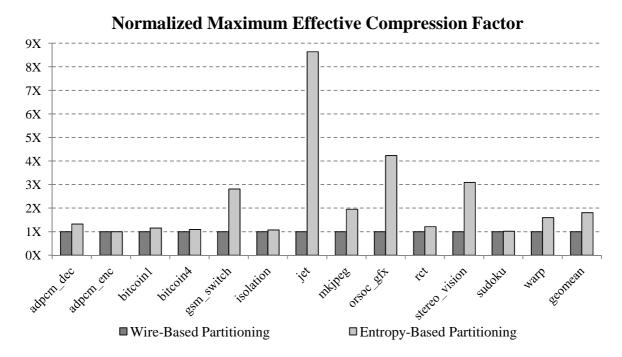

| FIGURE 28. NORMALIZED MAXIMUM EFFECTIVE COMPRESSION FACTOR FOR WIRE-BASED AND ENTROPY-BASED PARTITIONING                                                                                                                                                             |

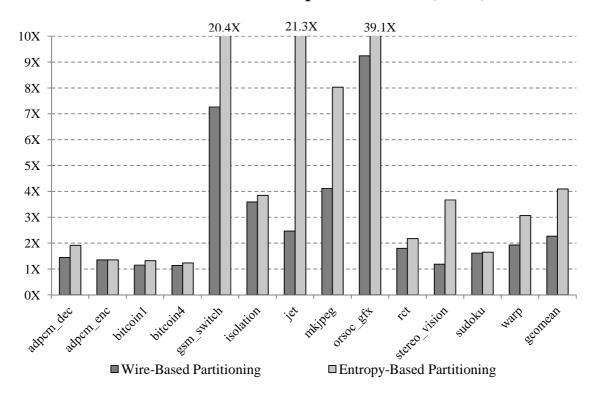

| FIGURE 29. ABSOLUTE MAXIMUM EFFECTIVE COMPRESSION FACTORS FOR WIRE-BASED AND ENTROPY-BASED PARTITIONING. THE CHART SCALE IS ZOOMED IN TO ILLUSTRATE SCALE OF SMALLER VALUES                                                                                          |

| FIGURE 30. NORMALIZED MAXIMUM EFFECTIVE COMPRESSION FACTOR FOR WIRE-BASED AND ENTROPY-BASED PARTITIONING. THE CHART SCALE IS ZOOMED IN TO ILLUSTRATE SCALE OF SMALLER VALUES                                                                                         |

| FIGURE 31. A 2-INPUT OR GATE WITH INPUTS A & B AND OUTPUT Q                                                                                                                                                                                                          |

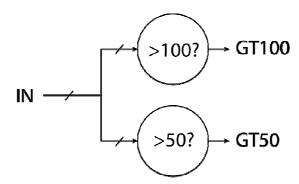

| Figure 32. An example circuit that uses two comparators to produce two single-bit outputs (GT100 and GT50) that have correlated values due to the logic of the circuit                                                                                               |

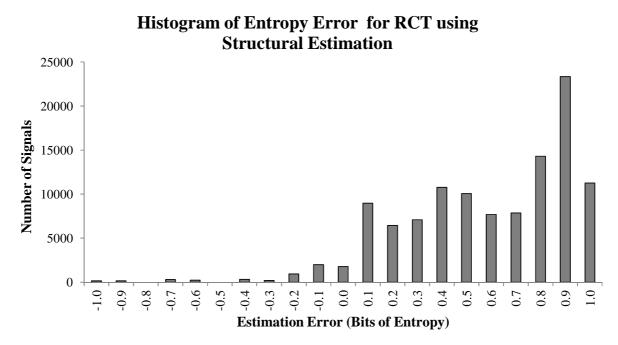

| FIGURE 33. HISTOGRAM OF THE ERROR (IN BITS OF ENTROPY) FOR ALL SIGNALS IN THE RCT CIRCUIT WHEN USING STRUCTURAL ENTROPY ESTIMATION                                                                                                                                   |

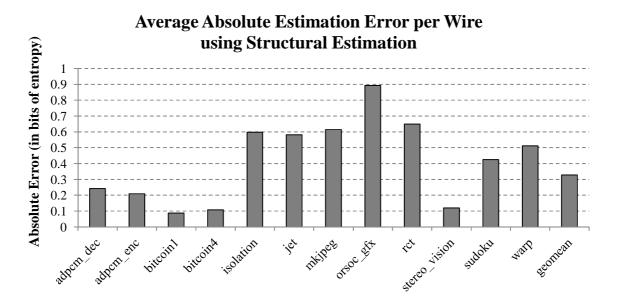

| FIGURE 34. AVERAGE ABSOLUTE ESTIMATION ERROR FOR ALL BENCHMARKS USING STRUCTURAL ESTIMATION118                                                                                                                                                                       |

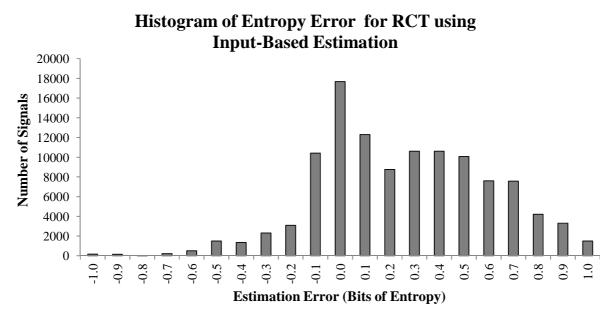

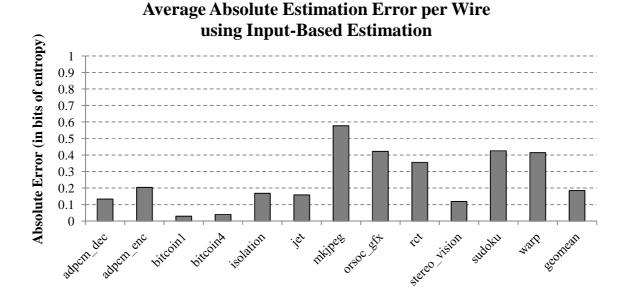

| FIGURE 35. HISTOGRAM OF THE ERROR (IN BITS OF ENTROPY) FOR ALL SIGNALS IN THE RCT CIRCUIT WHEN USING INPUT-BASED ENTROPY ESTIMATION                                                                                                                                  |

| FIGURE 36. AVERAGE ABSOLUTE ESTIMATION ERROR FOR ALL BENCHMARKS USING INPUT-BASED ESTIMATION121                                                                                                                                                                      |

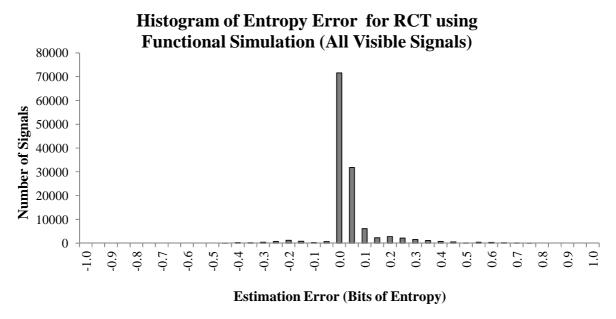

| FIGURE 37. HISTOGRAM OF THE ERROR (IN BITS OF ENTROPY) FOR ALL SIGNALS IN THE <i>RCT</i> CIRCUIT WHEN USING FUNCTIONAL SIMULATION OF THE CIRCUIT AND INCLUDING DATA FROM ALL SIGNALS VISIBLE IN FUNCTIONAL SIMULATION                                                |

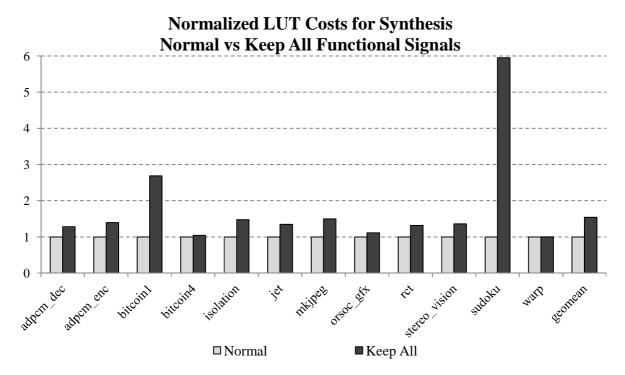

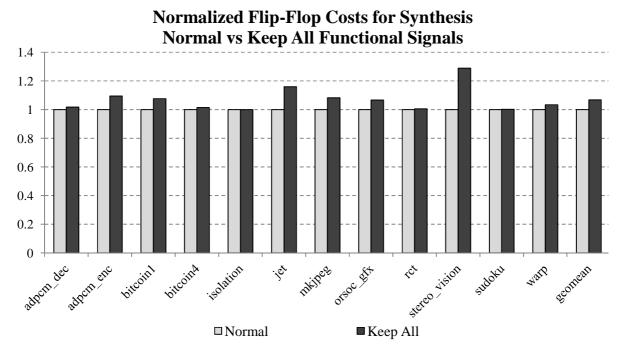

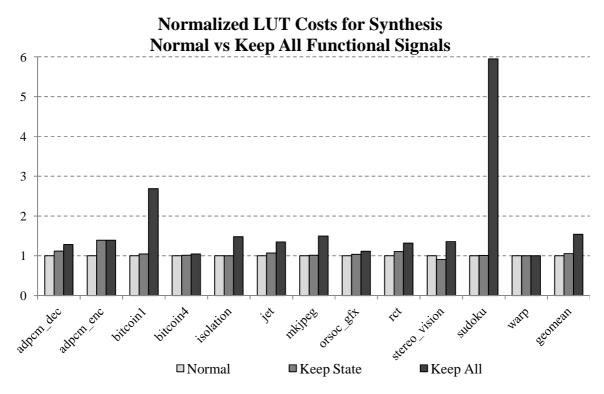

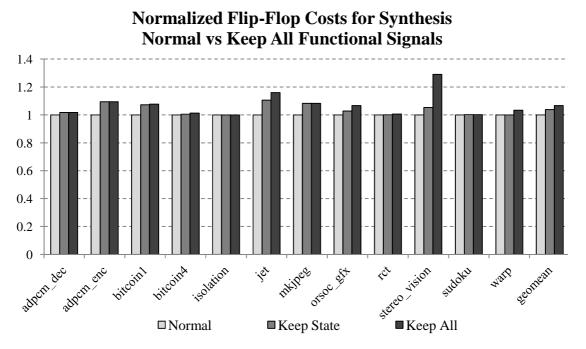

| FIGURE 39. NORMALIZED LUT SYNTHESIS COST FOR THE BENCHMARK CIRCUITS WHEN SYNTHESIZING NORMALLY AND REQUIRING THAT THE SYNTHESIS TOOL KEEP ALL FUNCTIONAL SIGNALS FOR USE WITH FUNCTIONAL-SIMULATION-BASED ENTROPY ESTIMATION.                                        |

| FIGURE 38. NORMALIZED FLIP-FLOP SYNTHESIS COST FOR THE BENCHMARK CIRCUITS WHEN SYNTHESIZING NORMALLY AND REQUIRING THAT THE SYNTHESIS TOOL KEEP ALL FUNCTIONAL SIGNALS FOR USE WITH FUNCTIONAL-SIMULATION-BASED ENTROPY ESTIMATION                                   |

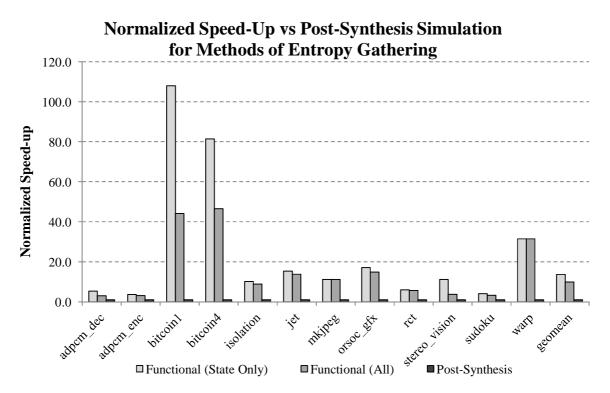

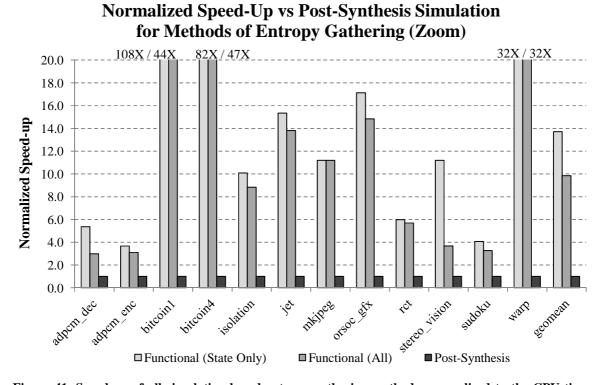

| FIGURE 40. SPEED-UP OF ALL SIMULATION-BASED ENTROPY GATHERING METHODS, NORMALIZED TO THE CPU TIME REQUIRED FOR POST-SYNTHESIS SIMULATION                                                                                                                             |

| FIGURE 41. SPEED-UP OF ALL SIMULATION-BASED ENTROPY GATHERING METHODS, NORMALIZED TO THE CPU TIME REQUIRED FOR POST-SYNTHESIS SIMULATION. THE CHART IS ZOOMED TO ILLUSTRATE THE SCALE OF SMALLER VALUES.                                                             |

| FIGURE 42. NORMALIZED LUT SYNTHESIS COST FOR THE BENCHMARK CIRCUITS WHEN SYNTHESIZING NORMALLY, KEEPING ALL FUNCTION SIGNALS, OR KEEPING ONLY STATE SIGNALS                                                                                                          |

| FIGURE 43. NORMALIZED FLIP-FLOP SYNTHESIS COST FOR THE BENCHMARK CIRCUITS WHEN SYNTHESIZING NORMALLY, KEEPING ALL FUNCTION SIGNALS, OR KEEPING ONLY STATE SIGNALS                                                                                                    |

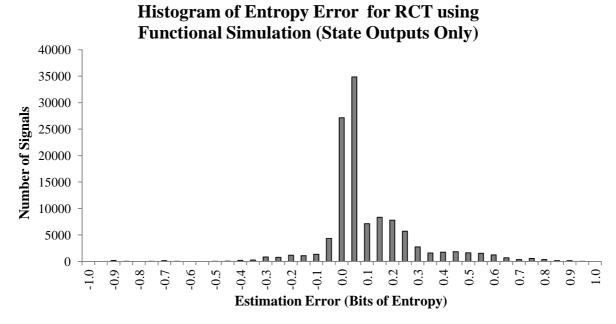

| FIGURE 44. HISTOGRAM OF THE ERROR (IN BITS OF ENTROPY) FOR ALL SIGNALS IN THE <i>RCT</i> CIRCUIT WHEN USING FUNCTIONAL SIMULATION OF THE CIRCUIT AND INCLUDING DATA FROM ONLY STATE OUTPUTS IN FUNCTIONAL SIMULATION                                                 |

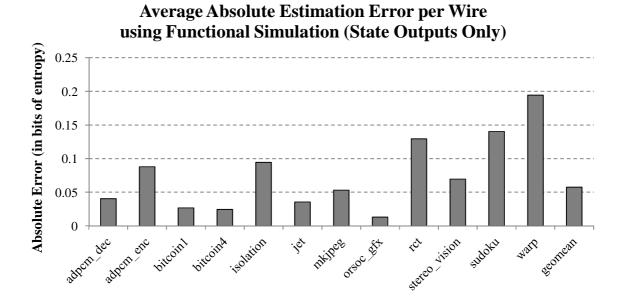

| FIGURE 45. AVERAGE ABSOLUTE ENTROPY ESTIMATION ERROR FOR ALL BENCHMARKS WHEN USING FUNCTIONAL SIMULATION OF THE CIRCUIT AND INCLUDING DATA FROM ONLY STATE OUTPUTS IN FUNCTIONAL SIMULATION.                                                                         |

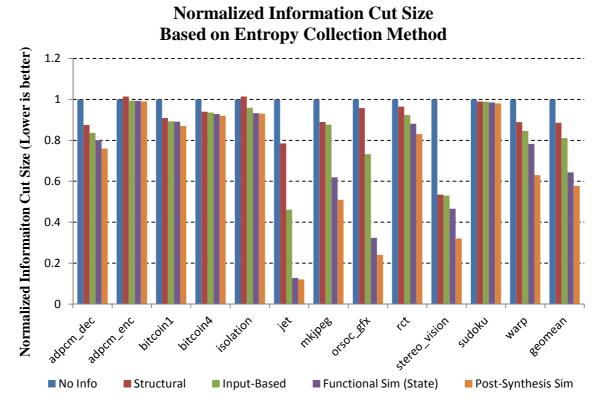

| FIGURE 46. NORMALIZED INFORMATION CUT SIZES ACHIEVED WHEN USING ENTROPY-BASED PARTITIONING WITH DIFFERENT METHODS OF COLLECTING THE WIRE ENTROPY DATA. VALUES ARE NORMALIZED TO PARTITIONING WITH NO ENTROPY INFO (WIRE-BASED PARTITIONING). LOWER VALUES ARE BETTER |

| FIGURE 47. COMPRESSION FACTORS FOR VARIOUS HUFFMAN SYMBOL SIZES IN THE RCT                                                                                                                                                                                           |

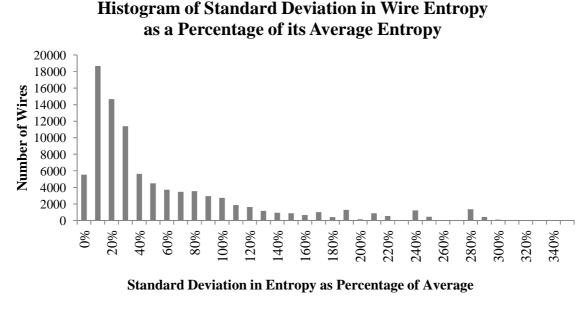

| FIGURE 48. HISTOGRAM OF THE STANDARD DEVIATION IN WIRE ENTROPY (AS A PERCENTAGE OF EACH WIRE'S AVERAGE ENTROPY) FOR THE <i>RCT</i> BENCHMARK WHEN COMPUTING ENTROPY OVER 1 $\mu$ S TIME WINDOWS    | 137  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

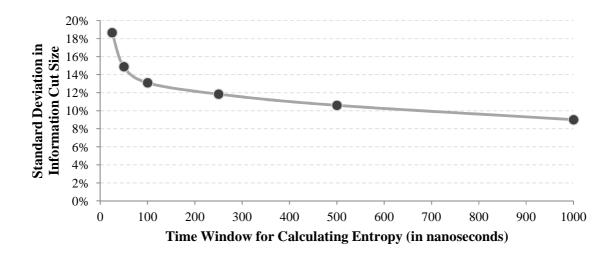

| FIGURE 49. STANDARD DEVIATION IN INFORMATION CUT SIZE FOR THE RCT USING DIFFERENT ENTROPY COLLECT TIME WINDOWS.                                                                                    | TION |

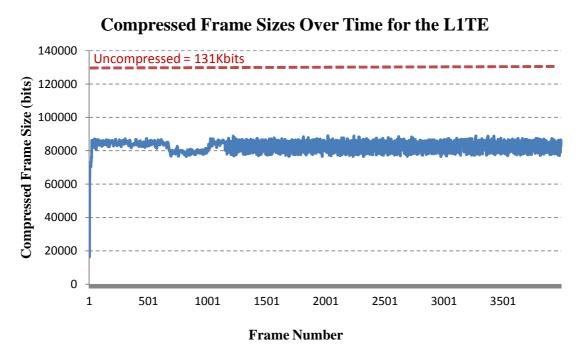

| Figure 50. Huffman compressed frame sizes for the first $4000$ input data sets for the RCT circuit, partitioned for the L1TE.                                                                      | 140  |

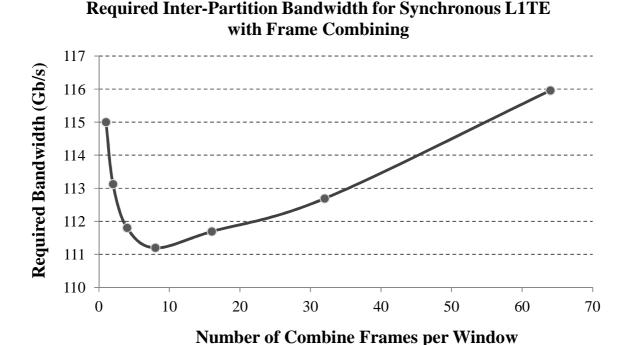

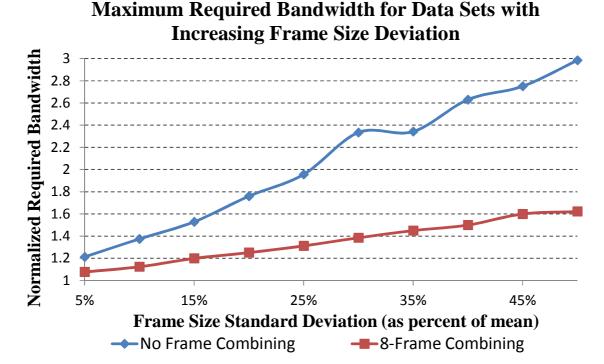

| FIGURE 51. THE REDUCTION IN THE REQUIRED INTER-PARTITION BANDWIDTH FOR THE SYNCHRONOUS L1TE WHE USING FRAME COMBINING TO REDUCE THE VARIATION IN THE DATA THAT MUST BE TRANSMITTED IN EACH TWINDOW | ГІМЕ |

| FIGURE 52. NORMALIZED REDUCTION IN REQUIRED BANDWIDTH WHEN USING FRAME-COMBINING WITH A TIME WINDOW OF 8 FRAMES FOR NORMAL DISTRIBUTIONS WITH INCREASING DEVIATION IN FRAME SIZES                  | 143  |

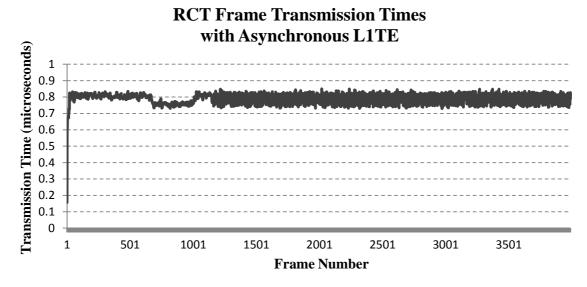

| Figure 53. Frame transmission times (in $\mu$ s) for the first 4000 frames on the asynchronous L1TE which using the same bandwidth as the synchronous L1TE.                                        |      |

| FIGURE 54. ONE OF THE MANY L1 PROCESSING BOARDS FROM THE L3 EXPERIMENT.                                                                                                                            | 159  |

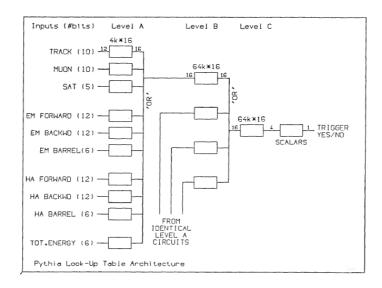

| FIGURE 55. DELPHI'S TREE-BASED LOOK-UP TABLE.                                                                                                                                                      | 160  |

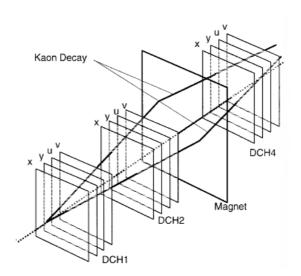

| FIGURE 56. TRACKING SENSORS USED IN THE NA48 EXPERIMENT.                                                                                                                                           | 162  |

| FIGURE 57. ARCHITECTURE OF THE NA48 TRIGGER.                                                                                                                                                       | 163  |

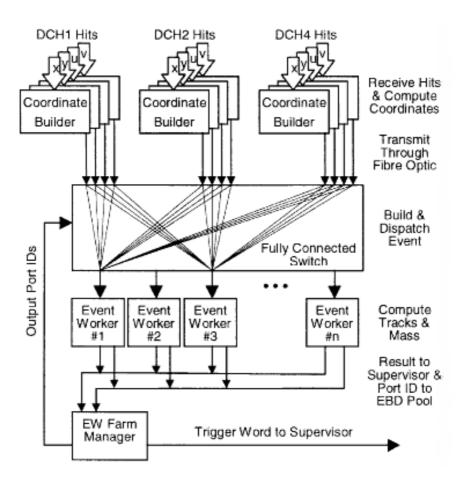

| FIGURE 58. HIGH-LEVEL DIAGRAM OF THE BABAR TRIGGER AND DAQ SYSTEM                                                                                                                                  | 166  |

| FIGURE 59. BABAR L1 TRIGGER ALGORITHMS.                                                                                                                                                            | 167  |

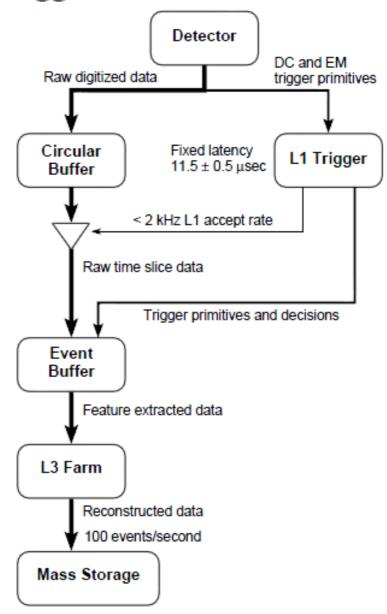

| FIGURE 60. EVENT RATES IN THE PHENIX EXPERIMENT FOR DIFFERENT IONS.                                                                                                                                | 168  |

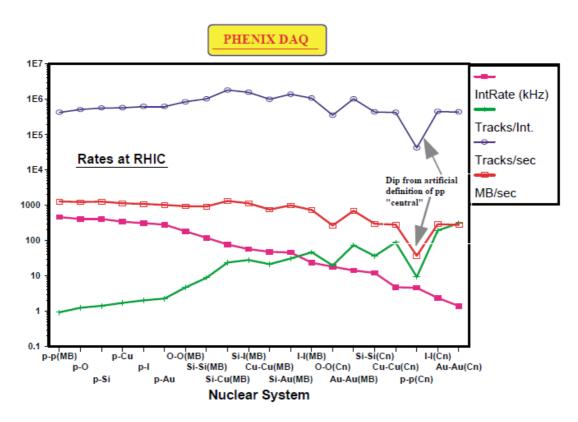

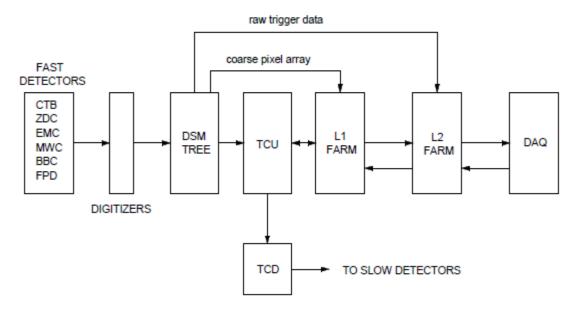

| FIGURE 61. DATA ACQUISITION IN THE STAR EXPERIMENT.                                                                                                                                                | 169  |

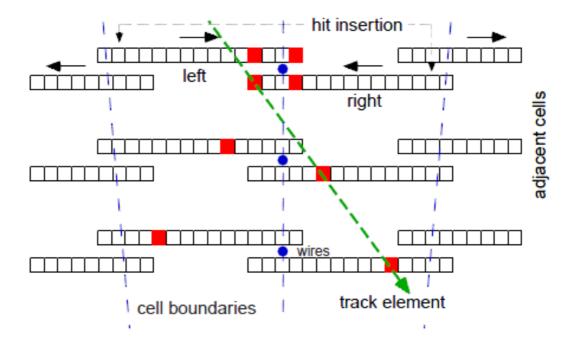

| FIGURE 62. SEGMENT RECONSTRUCTION SCHEME IN THE H1 AT HERA.                                                                                                                                        | 171  |

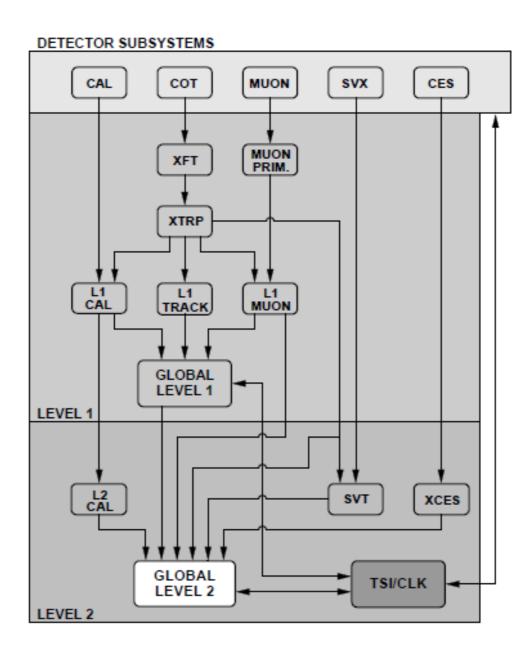

| FIGURE 63. LEVEL-1 AND LEVEL-2 TRIGGER ARCHITECTURE FOR THE CDF EXPERIMENT                                                                                                                         | 174  |

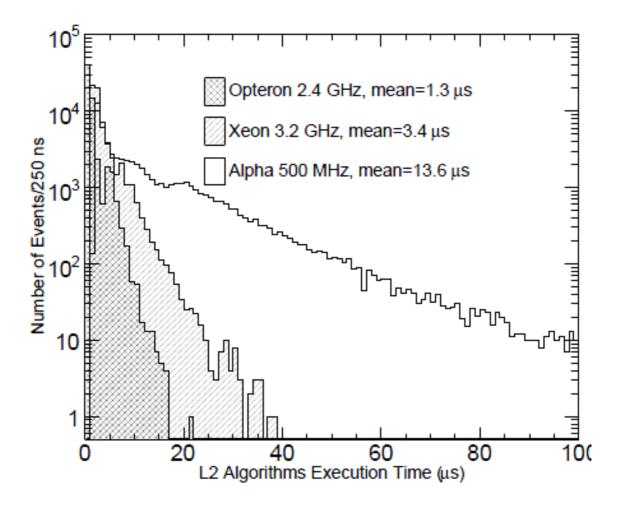

| FIGURE 64. EVENT PROCESSING TIMES FOR DIFFERENT PROCESSOR ARCHITECTURES IN CDF RUN-IIB                                                                                                             | 176  |

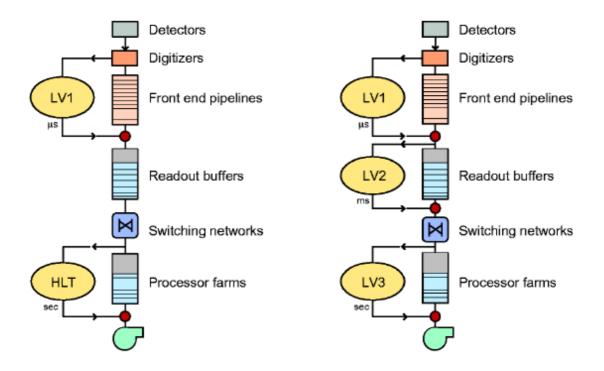

| FIGURE 65. THE CMS TRIGGER ARCHITECTURE (LEFT) COMPARED TO A TRADITIONAL ARCHITECTURE (RIGHT)                                                                                                      | 178  |

# LIST OF TABLES

| Table I. Max frequency and resource utilization (in percent of the TX240T's resources) for implementations of the CMS experiment's Electron/Photon ID module using several different architectures. Utilization values are in percent, and represent the cost of a single instance of the module | 39 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| $TABLE\ II.\ RESOURCE\ utilization\ for\ Electron/Photon\ ID\ architectures\ when\ maximally\ multiplexed.\ .44$                                                                                                                                                                                 | Ю  |

| TABLE III. RESOURCE UTILIZATION RANGES FOR ELECTRON/PHOTON ID ARCHITECTURES ACCOUNTING FOR FREQUENCY AND RESOURCE RANGES FROM MONTE CARLO SIMULATION                                                                                                                                             | 14 |

| TABLE IV. MULTI-PERSONALITY BENCHMARK GRAPHS, SORTED BY ASCENDING NUMBER OF NODES                                                                                                                                                                                                                | 53 |

| TABLE V. NORMALIZED CUT SIZE AND DEVIATION FROM TARGET RESOURCE UTILIZATION RATIO FOR DIFFERENT INITIAL NODE PERSONALITY SELECTION METHODS (RANDOM VS. PROPORTIONAL)                                                                                                                             | 17 |

| TABLE VI. CUT SIZE COMPARISON OF MF, HMETIS, AND THE BEST OF THE 40 PARTITIONERS IN THE WALSHAW PARTITIONING ARCHIVE FOR THE SINGLE-RESOURCE VERSIONS OF OUR CHACO-BASED BENCHMARK GRAPHS.  LOWER VALUES ARE BETTER                                                                              |    |

| TABLE VII. GEOMETRIC MEANS OF THE NORMALIZED CUT SIZE, ABSOLUTE RUR DEVIATION, AND NORMALIZED WALL CLOCK RUN TIMES FOR THE SIX KLFM PARTITIONING STRATEGIES.                                                                                                                                     |    |

| TABLE VIII. SUMMARY OF BENCHMARK CIRCUITS USED IN INFORMATION-AWARE PARTITIONING                                                                                                                                                                                                                 | 8  |

| $TABLE\ IX.\ TRUTH\ TABLE\ WITH\ PROBABILITIES\ FOR\ OR\ GATE\ ENTROPY-COMPUTATION\ EXAMPLE.\11$                                                                                                                                                                                                 | .4 |

| TABLE X. COMPARISON OF CPU TIME REQUIRED FOR ENTROPY GATHERING USING POST-SYNTHESIS SIMULATION AND STRUCTURAL ESTIMATION                                                                                                                                                                         |    |

| TABLE XI. COMPARISON OF CPU TIME REQUIRED FOR ENTROPY GATHERING USING POST-SYNTHESIS SIMULATION AND INPUT-BASED ESTIMATION                                                                                                                                                                       | 9  |

| TABLE XII. COMPARISON OF CPU TIME REQUIRED FOR ENTROPY GATHERING USING POST-SYNTHESIS SIMULATION AND FUNCTIONAL SIMULATION-BASED ENTROPY ESTIMATION                                                                                                                                              | 22 |

| TABLE XIII. PUBLICATIONS DERIVED FROM PROJECTS IN DESCRIBED IN THIS DOCUMENT                                                                                                                                                                                                                     | 52 |

# 1. Introduction

### 1.1. Motivation

In recent years, the rise in prominence of 'Big Data' – a catch-all term for computing problems based on vast datasets generated from domains ranging from scientific experiments to internet search to social networking – has helped to maintain interest in designing large, many-node distributed computing systems in spite of continued increases in per-device logic density. Many systems designed to handle Big Data applications are becoming more and more heterogeneous, as graphical processing units (GPUs) and field programmable gate arrays (FPGAs) are increasingly used to improve these applications' throughput or response time. A prominent example of this type of system is present in the Large Hadron Collider (LHC), a massive high energy physics experiment that processes Petabytes of data per day. To analyze the data produced in its experiments, LHC depends on real-time computing systems made up of thousands of application-specific integrated circuits (ASICs), FPGAs, and general-purpose processors. The original design for these systems was an arduous and expensive process, relying heavily on a manual design process, and resulted in a highly complex system that could not be easily changed.

With the LHC's computing systems due for an overhaul as part of a large-scale upgrade to enable the next generation of high-energy physics experiments [1], there is renewed motivation to rethink the system architecture and automate prototyping techniques to improve the efficiency and reduce the complexity of the system. Previous research in the specific area of high-energy physics computing architectures and on the more general problem of system partitioning does not adequately account for the scale, degree of heterogeneity, or performance requirements of the LHC. This underscores the need for new algorithms capable of improving design automation for massive, heterogeneous computing systems.

The motivation to efficiently partition logic and efficiently utilize communication resources is not limited to the LHC, and applies more broadly to other applications that are distributed across large hardware systems. Multi-chip systems based on heterogeneous FPGAs are frequently used for emulation

and prototyping in ASIC design and for other high throughput, latency-sensitive application domains such as network processing and high-frequency trading. Heterogeneous processor clusters are also increasingly common in supercomputing and cloud computing, where applications must be mapped to heterogeneous compute nodes, and data transmission between partitions is expensive, whether it is at the inter-chip, inter-rack, inter-cluster, or inter-datacenter level. We will examine how the algorithms we developed for automating the design of high-energy physics systems can be more generally applied to the broader problem of partitioning an application across heterogeneous, distributed resources in order to efficiently utilize the available logic and minimize communication costs.

# 1.2. Objectives and Contributions

The goal of this dissertation is to improve the design process for large-scale, heterogeneous digital systems, with a focus on the special challenges presented by the exceptionally large and high-performance distributed hardware systems used in high-energy physics. Such systems have an essential role in enabling cutting-edge scientific research, but present unique problems that often go unaddressed by the commercial market. This presents an excellent opportunity for meaningful contributions from academic research. The research work we will describe in this document is divided into three major projects.

First, we analyze the design process of a state-of-the-art, real world application in the domain of high energy physics: the Regional Calorimeter Trigger (RCT) system for the Compact Muon Solenoid (CMS) experiment. Because high energy physics systems require their algorithms to co-exist on hundreds of chips, feature large amounts of interconnection, and have tight performance constraints, they can be difficult to modify even when built on reprogrammable hardware. This can be a significant limitation for physics researchers, as they may want to evolve or replace their algorithms over time to adapt to experimental conditions or search for new phenomena [2]. To address this problem, we develop new FPGA-based architectures for implementing important operations in physics processing that reduce variations in performance and resource costs. These design allowing physicists to more easily alter and

upgrade their algorithms without requiring major redesigns of the hardware systems that implement the algorithms. As part of our design exploration process, we also attempt to characterize some of the key challenges presented by the design the upgraded RCT system, which serve as motivational factors for our later work on automated design partitioning.

Second, we formulate a new version of a graph partitioning problem, multi-personality partitioning (MPP), in order capture the new challenges presented when partitioning designs for implementation on large heterogeneous systems with flexible resources, such as FPGAs and supercomputers. Although circuit partitioning has been the subject of much research in the past, prior work does not adequately model heterogeneous devices, resulting in either inefficient use of device hardware or high communication costs between devices. For large-scale applications that require many devices, this can lead to more expensive, complex, and difficult to maintain hardware systems. To address these challenges, we develop general and targeted heuristics for optimizing the use of device hardware and communication resources by creating automated algorithms for solving multi-personality partitioning problem, implement them in partitioning software, and analyze their efficacy on a set of modern-sized benchmarks.

Third, we extend our research into partitioning by attempting to improve the ability of automated algorithms to optimize partitioning decisions based on functional knowledge of application-specific circuits. To this end, we develop and evaluate automated methods for analyzing the data content of circuit signals and exploiting signal redundancy to decrease the cost of inter-partition communication in large, partitioned systems. We create a benchmark set of large application-specific circuits with characteristic input data sets and demonstrate that many of the signals within these circuits have low average information content as measured by their Shannon entropy. We demonstrate that we can exploit knowledge of signal entropy with automated partitioning algorithms to create partitions with significantly lower cross-partition information cut sizes. We will explore different methods to characterize signal entropy, including both simulation and logic analysis-based approaches, and evaluate their relative accuracy, computation times, and impact on circuit quality. Finally, we detail one proof-of-concept

application by introducing inter-partition data compression to the Level-1 Trigger Emulator, a hardware validation platform used in the development of high energy physics applications.

The specific contributions of each project are enumerated below.

### Flexible FPGA-based Architectures for High Energy Physics

- We develop firmware and software tools used in the design exploration process of the highluminosity RCT system for the CMS experiment at the Large Hadron Collider.

- We characterize the key algorithms used in calorimeter-based particle triggering applications and their related implementation costs on heterogeneous FPGAs.

- We design and evaluate logic architectures for creating coarse-grained look-up tables to allow flexible implementation of physics algorithms. We also perform a Monte Carlo analysis of cost variations in these architectures based on changes to the parameters of the algorithms to quantify the impact of altering key algorithm parameters.

### Multi-Personality Graph Partitioning

- We provide a formal definition of the new partitioning problem for heterogeneous, flexibleresource systems, describe its complexity, and introduce a new quality metric for balancing resource utilization across heterogeneous processing nodes.

- We create a set of large multi-personality graph benchmarks based on graphs derived from publicly available, real-world circuits and software task graphs

- We design an integer linear programming (ILP) model for multi-personality partitioning, and evaluate its performance and spatial complexity using sophisticated third-party ILP solvers.

- We develop software for implementing MPP using a modified version of the Kernighan-Lin/Fiduccia-Mattheyses (KLFM) heuristic to support multiple personalities, including modification to gain bucket data structures, clustering, personality remapping, and deadlock prevention. In our analysis, we evaluate how various implementation choices affect solution quality and run time.

### Information-Aware Circuit Partitioning

- We evaluate different metrics for characterizing signal information content in circuits, including simulation-based vs. structure-based metrics.

- We develop methods measuring and estimating the entropy of wires within a circuit and experimentally evaluate them in terms of their computation time, measurement accuracy, and impact on circuit synthesis. We integrate entropy data into the partitioning algorithms developed for MPP, prove that it is possible to achieve information cut sizes that are significantly smaller than conventional wire cut sizes, and observe how partitioning decisions vary when using entropy to select partitioning rather than traditional metrics.

- We quantify the advantages of information-aware partitioning through compression of interpartition signals using entropy coding.

- We identify other application domains that may benefit from content-aware partitioning by developing a set of diverse application-specific benchmark circuits with representative data sets.

- We demonstrate the practical use of information-aware partitioning on the RCT design as implemented on the Level-1 Trigger Emulator to identify compressible signals and reduce system bandwidth requirements and improve performance.

## 1.3. Document Organization

The remainder of this document is organized as follows: In Chapter 2, we introduce background information on FPGAs, processing systems for high energy physics, graph partitioning, and high speed serial data transmission, and information measurement in digital systems. In Chapter 3, we describe our work designing flexible hardware designs for the Level-1 Regional Calorimeter Trigger as part of the High-Luminosity Large Hadron Collider project. In Chapter 4, we introduce a new type of graph partitioning problem – multi-personality partitioning (MPP) – designed for partitioning heterogeneous logic devices. We also describe the development and implementation of multiple algorithms for solving

the MPP problem and evaluate their efficacy when partitioning large-scale circuit designs for FPGAs. In Chapter 5, we apply concepts from the field of information theory to the circuit partitioning problem, developing an entropy-based algorithm capable of partitioning circuits to minimize the bandwidth between chips when using compression. We demonstrate that our algorithm can significantly improve the performance of a hardware emulator system built for validating the design of high energy physics computing systems. In the remaining chapters, we summarize our contributions, outline potential future research directions, and enumerate research publications produced from our work. We also include a supplementary survey on triggering systems for high energy physics in the Appendix that provides additional historical context for our research into the development of electronics for physics experiments.

# 2. Background

In this section we provide a brief introduction to some of the core technology and terminology which will serve as a basis for our later description of the research in high energy physics architecture, heterogeneous netlist partitioning, and information-aware circuit partitioning. Additional related work for each project is included within their respective chapters and in the appendix.

# 2.1. Field Programmable Gate Arrays (FPGAs)

Field Programmable Gate Arrays are devices commonly used for implementing digital logic circuits. A key feature of FPGAs is that they are reconfigurable: that is, they can be programmed multiple times, allowing designers to change the logic functions implemented on the same FPGA. In this way, FPGAs offer some compromises between the performance and efficiency of application-specific integrated circuits (ASICs) and the flexibility of software running on general-purpose processors. Unlike the ASIC design model, where a custom circuit is built to implement a specific logic design, FPGAs are mass produced in different sizes, and designers must fit their logic into the available resources of the FPGA. FPGAs are frequently used in the following types of applications:

- Applications that need higher throughput, lower latency, or better efficiency than is offered by software, but must also be easily upgraded or must support multiple different designs.

- Specialized, small market applications where the number of devices needed does not justify

the high fixed costs of ASIC development.

- Time-critical circuit development or design exploration, where the time to produce an ASIC is prohibitive.

- Circuit emulation for the purpose of functional testing and debugging in the process of developing ASICs.

Modern FPGAs contain heterogeneous logic resources. In our work, we will use FPGAs produced by Xilinx [3] in our design processes, but for the purposes of our work they are not substantially different

from FPGAs from other vendors. There are three primary resource types on these FPGAs: small look-up table (LUT)-based blocks that can implement generic functions with a small number of inputs (we refer to these as configurable logic blocks or CLBSs), high density configurable memories (block RAMs or BRAMs), and units for performing fast arithmetic operations, such as multiplication and addition (digital signal processing blocks or DSPs). Circuits are implemented by programming the LUTs and connecting them to one another and the other resources using a configurable routing network. Internally, the resources are organized into blocks and regions, using a hierarchal routing scheme that allows high intrablock connectivity and restricts the amount of global connectivity. For off-chip communication, FPGAs have traditionally contained a large number of parallel I/O pins, but in recent years some FPGAs have added multiple high-speed serial transceivers. We will discuss these further in Section 2.4.

# 2.2. Processing and Data Acquisition for High Energy Physics

High-energy physics (HEP) is a scientific discipline that studies particle interactions at energy levels that exceed those that occur naturally on earth. HEP relies on the use of particle accelerators/colliders, enormous machines that accelerate sub-atomic particles to near-luminal velocities and then collide them together. An accelerator houses one or more *experiments*: collections of complex sensors, signal processing, and computing systems that collect and analyze data from the collections. At various points in this document, we will refer to systems belonging to the Compact Muon Solenoid (CMS) experiment at the Large Hadron Collider (LHC), the largest and most powerful particle accelerator in the world (soon to be upgraded to the High Luminosity LHC (HL-LHC) [4]; this upgrade serves as part of the motivation for our work).

One of the characteristic processing challenges of HEP is the massive amount of data that is produced by experiments. The amount of data produced by an experiment is the product of the rate at which the accelerator can produce collision events and the amount of data that is collected for each event. For instance, the LHC can produce new data sets every 25 ns, and CMS's sensors collect data at a rate of 1 Petabyte (PB) per second [5]. It is infeasible to store such large amounts of data, so HEP experiments

employ *trigger systems* – specialized processing units that perform real-time analysis of the sensor data and rapidly decide which data should be acquired for further study and which data should be immediately discarded. Because sensor data must be buffered during this decision process, trigger response time must be very fast in order to keep buffer sizes reasonable. We will describe the specific properties of trigger algorithms in greater depth in Chapter 3.

## 2.3. Graph Partitioning

Graph partitioning is one of the classic NP-Complete problems in computing [6]. Partitioning has many practical applications, but within the context of this document, we focus on its application to the design of digital systems. Circuits or computational tasks can be expressed as hypergraphs, where nodes are used to model circuit element, logic function, or tasks (depending on the level of granularity) and edges are used to model wires, buses, or communication channels. Partitioning such graphs is a key step in processes such as circuit floorplanning, rapid prototyping of multi-chip systems, and scheduling of large software tasks in distributed computing.

### 2.3.1. Homogeneous Hypergraph Partitioning

The hypergraph bipartitioning problem is defined based on two components: a constraint related to balancing the nodes in each partition and an optimization objected related to the edges that span the partitions. Formally, the node constraint is expressed as follows: Given a hypergraph G = (V, E), composed of nodes  $v \in V$  and hyperedges  $e \in E$ , with node and edge weights w(v) and w(e) respectively, divide all nodes of G into two disjoint sets,  $V_I$  and  $V_2$  (i.e.,  $V_1 \cup V_2 = V$ ,  $V_1 \cap V_2 = \emptyset$ ), subject to the constraint that the sum of node weights in the two subsets are equal:

$$\sum_{v_i \in V_1} w(v_i) = \sum_{v_j \in V_2} w(v_j)$$

(1)

For a circuit netlist, the node weight might represent the area or number of resources consumed by a given logic block, and for a software task it might represent the number of cores or memory footprint

needed by the task. For most practical problems it is sufficient to simply require that the partitions are of similar size rather than being equal. For example, if the constraint were modified to ensure the difference in size was less than 1%, the previous equation becomes:

$$\left| \sum_{v_i \in V_1} w(v_i) - \sum_{v_j \in V_2} w(v_j) \right| \le 0.01 \sum_{v \in V} w(v)$$

(2)

The actual imbalance threshold can be chosen to ensure that each partition can be implemented within a given resource budget. On its own, the node constraints given in Equations (1) and (2) are formulations of the well-studied set partitioning problem [7]. The graph partitioning problem uses set partitioning as a constraint for the graph's vertices and adds an optimization goal based on the graph topology. The other component of the graph partitioning problem is the optimization objective. The most common objective is to minimize the sum of the weights of all edges (or hyperedges in the case of hypergraphs) that span between the partitions – a metric referred to as the *span* or *cut size*. Cut size reduction is a useful optimization goal because inter-partition connections may model expensive communication paths, such as global wires on a circuit or inter-node communication in a supercomputer. Formally, if we define  $e_{v_1,v_2,...,v_k}$  as the hyperedge connected to nodes  $v_1, v_2, ..., v_k$ , then:

$$cut \ size(V_1, V_2) = \sum_{e \in E} w(e_{v_1, \dots v_j}) \quad \text{s.t. for some } i, j, \ v_i \in V_1 \text{ and } v_j \in V_2$$

(3)

Homogeneous graphs were long used as a model for partitioning computing systems, and the majority of partitioning algorithms were developed for homogeneous graphs. However, the transition to heterogeneous computing resources motivated the development of a newer graph model, as we will discuss in the next section.

### 2.3.2. Heterogeneous Hypergraph Partitioning

The homogenous node model used in previously-described graph partitioning problem is insufficient to model many modern digital systems, such as applications to be implemented in Field-Programmable Gate Arrays (FPGAs), Systems-on-Chip (SoCs), and supercomputers, as these systems often include

multiple heterogeneous resource types. This has led to a new problem, referred to alternately in academic literature as *heterogeneous*, *multi-constraint*, or *complex-resource graph partitioning*: Given a graph with nodes that have weights in R resource types, the partitioning solution must balance all R resources within their specified maximum margins of imbalance. The weight of each node is now described by an R-entry weight vector w. If we define  $w_r(v)$  as node v's weight in resource r, and  $I_r$  as the maximum weight imbalance between partitions for resource r, then the imbalance constraint equation becomes:

$$\frac{\left|\sum_{v_i \in V_1} w_r(v_i) - \sum_{v_j \in V_2} w_r(v_j)\right|}{\sum_{v_k \in V} w_r(v_k)} \le I_r \quad \forall \quad r \in 1..R$$

$$(4)$$

Although multi-constraint graphs allow a more detailed model of systems containing heterogeneous logic, further refinement is needed to model the ability to flexibly map computations to different resource types. Specifically, existing work on using multi-constraint partitioning for heterogeneous circuits is based on the assumption that all nodes can only be implemented in one way – a significantly limiting assumption for FPGAs and heterogeneous processors. We will introduce our new model that eliminates this limitation, multi-personality graphs, in Section 4.2. This new model will serve as the basis for one of the major research projects we will describe in this document, Multi-Personality Partitioning.

## 2.4. Multi-Gigabit Serial Data Transmission

Multi-gigabit serial transceivers (MGTs) are becoming a widely used communication method in systems requiring high data throughput. MGTs offer several advantages over traditional parallel buses, such as reduced pin counts, decreased power consumption, and avoidance of clock-skew problems [8]. MGTs have long been used at the network level in technologies such as Ethernet, and they are becoming increasingly prevalent in the design of high performance digital circuits. At the chip and circuit level, FPGA manufacturers are increasingly replacing parallel input/output (I/O) pins with MGTs [9], serial interfaces have been proposed for next-generation memory architectures [10], and serial links for on-chip

communication have been proposed in research [11]. The transition to the use of MGTs rather than parallel I/Os introduces important changes to the computational constraints associated with communication. Devices that use MGTs for communication typically have more available bandwidth, but using MGTs comes with the cost of higher latency than parallel I/Os due to the time it takes to serialize and de-serialize data. These changes will contribute to the motivation for our development of an entropy-based and bandwidth-focused circuit partitioning method in Chapter 5.

# 2.5. Information Content in Digital Signals

The study of the information content of signals and stored data – information theory – is a broad topic with applications in many fields. Within the context of this document, we will focus on providing a basic introduction to the way information is quantified and measured in digital systems.

### 2.5.1. Quantifying Information

The field of information theory was established with Claude Shannon's foundational work to develop a mathematical framework for describing and analyzing communication [12]. Shannon introduced the idea that the amount of information contained in a signal or data set could be uniformly quantified using a concept he referred to as 'information entropy.' Information entropy should not be confused with thermodynamic entropy. Although they are linked [13], and the laws of thermodynamic entropy have been used to define constraints on information entropy [14] [15] and vice versa [16] [17], they are not synonymous. Throughout this document, when we refer to 'entropy', it will refer to Shannon's concept of information entropy unless otherwise stated.

If we consider a signal that is capable of producing different values (also referred to as 'symbols') at a given time, Shannon's information entropy is based on the statistical likelihood of specific data values occurring. If we define S as the set of all possible symbols and p(s) as the probability that a given symbol, s, is produced by the signal, then the Shannon entropy can be defined as:

$$E = -\sum_{s \in S} p(s) \log_b(p(s))$$

where

$$p(s) \log_b(p(s)) = 0 \quad \text{for} \quad p(s) = 0$$

(5)

Shannon's definition of information entropy mirrors Boltzmann's equation for thermodynamic entropy in statistical mechanics. The base of the logarithm, b, may be chosen differently depending on the application. In our discussion of entropy in digital systems, we will use b = 2, which results in the entropy having units of 'bits'.

From its inception, there has been debate over whether entropy is truly a measure of the information content of a signal or whether it is better described as a measure of the uncertainty of predicting a signal's value [18]. From a practical standpoint in the design of communications systems, entropy is a useful metric for quantifying information. Entropy-based coding has been used to compress data in many application domains [19] [20] [21], demonstrating that signals with high entropy require more bits to transmit (and conversely that signals with low entropy can be more effectively compressed). Since our interest in entropy is related to communication efficiency, we treat entropy as a measurement of the quantity of information and defer the semantic argument to others.

### 2.5.2. Entropy in Digital Systems

In Equation (5) we gave the formula for computing the entropy of a signal with a set of possible symbols. Within the context of digital logic circuits, the signal is a wire or group of wires and the symbols are the possible values the wire(s) can transmit. For a single wire in a binary digital system, there are two

possible values: '0' and '1'. If  $p(s_0)$  is the probability of the symbol '0' occurring, the entropy equation can be rewritten as:

$$E = -p(s_0)\log_2(p(s_0)) - p(s_1)\log_2(p(s_1))$$

(6)

Since  $p(s_0) + p(s_1) = 1$ , Equation (6) can be further rewritten as:

$$E = -(1 - p(s_1))\log_2(1 - p(s_1)) - p(s_1)\log_2(p(s_1))$$

(7)

Thus, we can consider the entropy of any given wire in the circuit to be a function of the probability that its value will be '1' at a given time (we can also derive an identical equation based on the probability

Figure 1. Entropy (in bits) versus probability of having a value of '1' for a binary variable [221].

the wire will be '0'). Equation (7) is represented graphically in Figure 1. From this diagram, we can observe two important properties of the entropy of a binary signal. First, the maximum entropy of the wire is 1 bit. We consider an individual wire to physically represent 1 bit in a digital system, but the actual amount of information that wire caries is at most 1 bit and may be less than that. Second, the maximum entropy occurs when there are equal probabilities that the wire will have a value of '0' or '1'. This agrees with our earlier description of entropy as quantifying the predictability of a signal's value. These observations also hold true when we consider logical groupings of multiple wires that may have

more than two possible values. The entropy (in bits) of a multi-wire signal is always less than or equal to the number of wires in the signal, and the maximum entropy (which is equal to the number of wires) occurs when there is an equal probability of all symbols occurring.

The idea of combining the entropies of multiple signals into a single value will become important in our later discussion of entropy-based partitioning. Formally, Shannon defined the 'joint entropy' to describe the combined entropy of multiple signals. To compute the joint entropy of wires (or wire groups)  $W_1, ..., W_n$  with symbol sets  $S_1, ..., S_n$  respectively:

$$E(W_1,...,W_n) = -\sum_{s_1 \in S_1} ... \sum_{s_n \in S_n} p(s_1,...,s_n) \log_2(p(s_1,...,s_n))$$

where

$$p(s_1,...,s_n) \log_2(p(s_1,...,s_n)) = 0 \quad \text{for} \quad p(s_1,...,s_n) = 0$$

(8)

In Equation (8),  $p(s_1,...,s_n)$  is the joint probability that the symbols  $s_1$ , ...,  $s_n$  will occur together. If the wires' values are independent, the joint probability is the product of the individual symbol probabilities and the joint entropy is equal to the sum of the entropies of the individual wires. This represents the upper bound on the joint entropy since we cannot use any wire's value to predict another wire's value. Thus:

$$E(W_1, ..., W_n) \le \sum_{i=1}^n E(W_i)$$

(9)

We will utilize this upper bound on the joint entropy of groups of wires when we explore the idea of computing and minimizing the maximum joint entropy of the wires that cross between circuit partition boundaries in Chapter 5.

### 2.5.3. Other Information Measurement Metrics

Thus far, we have used Shannon's definition for entropy. A key aspect of Shannon's definition of entropy is that it treats signals as random variables. In real digital systems, do not necessarily have uniform probability distributions over time [22]. If we assume that the signals are not independent

random variables, the Shannon entropy may overestimate their information content [23]. As a result, other entropy formulations have been proposed for quantifying the amount of information in binary sequences. Several alternate entropy metrics are based on computing a binary derivative of a signal's value changes over time [24] [25] and have led to new methods of computing entropies [26].

If we approach metrics for quantifying information based on their applications to compression, we can define the amount of information in a signal based on its Kolmogorov-Chaitlin complexity [27] [28], a measure of the minimal amount of information that would be required to reproduce a signal. Kolmogorov complexity has been proven to be incomputable [29]; this implies that there is no feasible metric we can compute that will ensure minimal compression. As such, we will continue to use the Shannon entropy as our information metric since it is easily computed, well understood, and commonly used as a metric for optimizing communications.

# 3. Mixed-Granularity Reconfigurable Architectures for High

# **Energy Physics Processing**

In this chapter, we describe our work to develop and evaluate an FPGA-based processing system for the high-luminosity calorimeter trigger system of the Compact Muon Solenoid experiment at the Large Hadron Collider. This project also helped us to gain insight into areas of the circuit design process that could derive significant benefit from the development of new algorithms for design automation and rapid prototyping. These insights will serve as the motivational foundation of the research described in Chapters 4 and 5.

### 3.1. Motivation

On-going trends in the fields of high energy particle accelerators and electronics have created new design challenges for their real-time processing systems. For example, increases in collision rates and event resolution have driven sensor data rates to 1 Petabyte per second at the state-of-the-art Large Hadron Collider (LHC) particle accelerator. To handle this large amount of data, scientists employ triggering systems consisting of hundreds of specialized processing units capable of handling huge amounts of data with µs-scale processing latencies. High throughput and low latency is particularly important in the Level-1 (L1) trigger system responsible for making the first triggering decisions. As shown in Figure 2, the output throughput of L1 systems has been scaling exponentially, increasing by 1-2 orders of magnitude with each new generation of accelerator. This has driven trigger design away from the use of general-purpose processors, and toward application-specific custom electronics. Meanwhile, the rising cost and complexity of constructing particle accelerators has had a major impact on their design process. The LHC has been designed to be upgraded to support higher luminosities and newer experimental objectives, and the supporting electronics must be capable of adapting to perform new algorithms. As the process of simply shutting down and restarting the experiment for maintenance

Figure 2. The required throughput of trigger systems has been increasing exponentially over time [23]. Note: Both axes are log-scale.

requires several months and generates enormous costs, it is essential that the processing architecture be flexible and robust to change over the lifetime of the accelerator.

Designing systems for a large-scale, collaborative project like the LHC presents its own challenges. Components of the hardware and firmware design are handled by many disparate scientific and academic groups. The design specifications and hardware platforms may change frequently during development. This has motivated a need for automated tools to aid in rapid prototyping and retargeting based on changes in system specifications.

Initially, the extremely high performance requirements of the LHC necessitated the use of high-speed ASICs [30]. With advancements in process technologies and the associated boost in logic density and performance, FPGAs have become an attractive platform to replace ASICs for real-time processing, due to their reprogrammable nature. However, reprogrammability alone does not guarantee that an FPGA-based system architecture will be able to easily support changes to in the experiments, as new circuits for new algorithms may have vastly different timing and area requirements.

### 3.2. Related Work

The inception of modern computer-based trigger systems can arguably be traced back to the 1970s at ADONE electron-positron collider at Frascati National Laboratory [31] and its 'spiral reader' system [32] for bubble physics. The spiral reader was perhaps the first on-line processing system based on software running on mainframe computers. A few years later, CERN's Intersecting Storage Rings (ISR) was the first particle accelerator to achieve proton-proton collisions by colliding separate beams [33]. The development of colliding beam accelerators vastly increased collision rates; since then, data rates have been a dominating constraint in trigger design.

In the 1980s and 1990s, the increasing cost of constructing accelerators began motivating thoughts of how to increase their architectures' flexibility and lifespan. The Axial Field Spectrometer Trigger introduced a heterogeneous, multi-level design, using both simple processing based on 'coincidence counting' and pre-computed RAM look-up tables (LUTs) [34] and a custom, 16-bit programmable DSP processor [35]. Both the contents of the RAM LUT and the software running on the DSP could be modified to change the physics algorithms after the system was installed. The CDF experiment at Fermilab extended heterogeneity with a 3-level trigger system that used ASIC-based L1 & L2 triggers and a software-based L3 running on a computer farm [36]. CDF was one of the first triggers built for modularity and flexibility; its L2 'Mercury' ASICs were designed to be physically swappable. This helped CDF stay in operation for 20 years. The Large Electron Positron (LEP) ring was built to study events caused by beam-gas interactions that were not well understood prior to the start of real experiments. LEP therefore needed to be able to alter trigger algorithms after the system was deployed [37]. It was also one of the earliest systems to incorporate limited use of FPGAs (alongside RAM LUTs) for this purpose [38].

By the 2000s, exponential increases in detector luminosity and data throughput had massively increased the scale of computing systems necessary to process the data being collected. The ATLAS and CMS experiments are characterized by event rates that dwarf other experiments, giving them each a data rate of over 1 Petabyte per second [39]. Both ATLAS and CMS feature a hardware-based L1 Trigger and