**Explainable Artificial Intelligence for Better Design of

Very Large Scale Integrated Circuits**

by

Wei Zeng

A dissertation submitted in partial fulfillment of

the requirements for the degree of

Doctor of Philosophy

(Electrical Engineering)

at the

UNIVERSITY OF WISCONSIN-MADISON

2021

Date of final oral examination: 08/12/2021

The dissertation is approved by the following members of the Final Oral Committee:

Azadeh Davoodi, Professor, Electrical and Computer Engineering

Yu Hen Hu, Professor, Electrical and Computer Engineering

Mikko Lipasti, Professor, Electrical and Computer Engineering

Dan Negrut, Professor, Mechanical Engineering

## ABSTRACT

---

With the advance of Very Large Scale Integration (VLSI) technology, the design process of VLSI circuits becomes more complex, challenging, and time-consuming. Recent years have seen a rising trend of machine learning (ML) incorporated in VLSI design flow for better and more efficient design and implementation of integrated circuits.

Explainable Artificial Intelligence (XAI) is an emerging technique that aims to perform prediction tasks while providing explanations for the predictions. XAI adds transparency and trustworthiness to ML models, leading to better human understanding and exploitation of the models. With ML being applied in VLSI design, it is desirable to adopt ideas from XAI for even better and more trustworthy outcomes of VLSI design.

This dissertation explores the usage of Shapley Additive Explanation (SHAP)—a recent development in XAI, on different aspects and stages of VLSI design flow. Specifically, we propose three techniques that adopt SHAP in front-end and back-end design flows, including (a) SHAP-guided layout obfuscation for enhanced hardware security in split manufacturing, (b) explainable routability prediction, which accelerates the physical design flow and provides hints for improving the design, and (c) explainable-ML-guided approximate logic synthesis for area-efficient computing in error-tolerant applications. These are the first works that incorporate XAI into VLSI design methodology. All of them achieve better results than their conventional counterparts or existing works in similar settings.

## ACKNOWLEDGMENTS

---

First and foremost, I would like to thank Prof. Azadeh Davoodi, whom I am so fortunate to have as my PhD advisor. She has been very helpful and supportive not only academically but also mentally, as well as in my post-graduate career. She is a nice advisor who really cares about her students in all aspects, to an extent far beyond my expectations.

I am very grateful to all my family members, colleagues and friends for their kind supports during my PhD study, especially during the hard times of COVID-19 pandemic. A special gratitude goes to my dearest parents and grandparents for their generous, continuous and unconditional love for decades and counting.

I would like to appreciate Dr. Rasit O. Topaloglu, one of the co-authors of most of my research papers adapted in this dissertation, for his commitment to our regular discussions and constructive suggestions and comments during my course of PhD research.

Also, thanks to all final oral committee members for their valuable feedback on my research proposal and this dissertation.

Last but never the least, I would like to acknowledge Prof. Xuan Zeng, Prof. Xin Li, and Dr. Hengliang Zhu, who had guided me through my very first research in this field even before I started this great PhD journey.

## CONTENTS

---

Abstract i

Acknowledgments ii

**1** Introduction and Motivation 1

**2** Related Works 4

2.1 *ML Applications in VLSI Design* 4

2.2 *Studies on Explaining ML Models* 5

**3** Summary of Contributions 8

**4** Preliminaries 11

4.1 *Shapley Value and SHAP* 11

4.2 *SHAP Tree Explainer for Tree-Based ML Models* 12

4.3 *Examples of SHAP Analysis* 13

**5** Routing Obfuscation Guided by Explanatory Analysis of a ML Attack 15

5.1 *Related Works on Layout Obfuscation* 15

5.2 *Overview of SHAP-Guided Routing Obfuscation* 17

5.3 *ML Attack Model for Split Manufacturing* 19

5.4 *SHAP Analysis for One V-pin Pair* 21

5.5 *Details of SHAP-Guided Routing Obfuscation* 23

5.6 *Experimental Results* 31

5.7 *Conclusion* 36

**6** Explainable Prediction of DRC Violation Hotspots 37

6.1 *Related Works on DRC Hotspot Prediction* 37

6.2 *Overview of Explainable DRC Hotspot Prediction* 39

|     |                                                      |    |

|-----|------------------------------------------------------|----|

| 6.3 | <i>Details of Explainable DRC Hotspot Prediction</i> | 42 |

| 6.4 | <i>Experimental Results</i>                          | 47 |

| 6.5 | <i>Conclusion</i>                                    | 54 |

| 7   | Approximate Logic Synthesis Guided by Explainable ML | 56 |

| 7.1 | <i>Preliminaries on Sampling-Based ALS</i>           | 58 |

| 7.2 | <i>Related Works on Sampling-Based ALS</i>           | 59 |

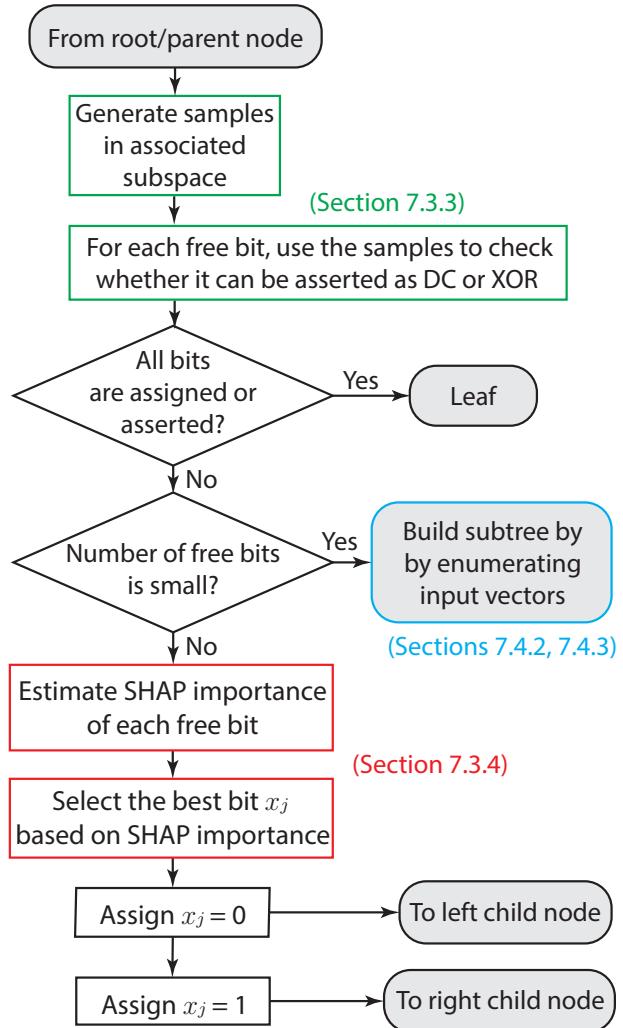

| 7.3 | <i>Overview of SHAP-Guided Logic Approximation</i>   | 61 |

| 7.4 | <i>Implementation Details</i>                        | 73 |

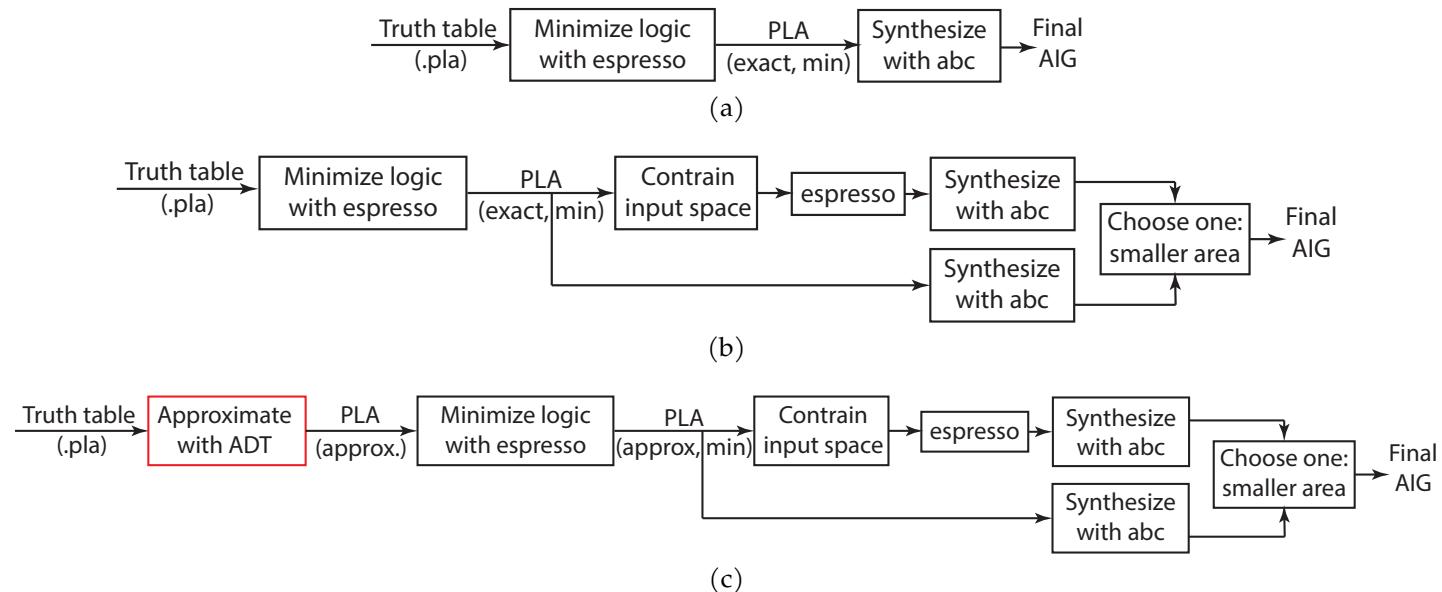

| 7.5 | <i>Experimental Results</i>                          | 76 |

| 7.6 | <i>Conclusion</i>                                    | 83 |

| 8   | Conclusion and Future Directions                     | 84 |

|     | Bibliography                                         | 86 |

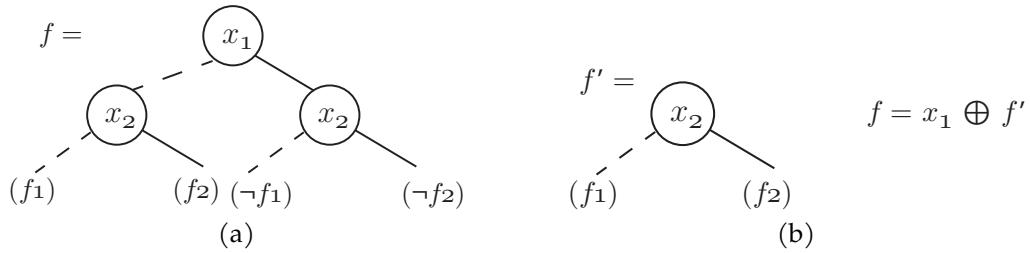

**LIST OF TABLES**

---

|     |                                                                                                                              |    |

|-----|------------------------------------------------------------------------------------------------------------------------------|----|

| 5.1 | Results of via perturbation on five ISPD'11 benchmark designs                                                                | 32 |

| 5.2 | Results of wire lifting on six ISCAS'85 benchmark designs                                                                    | 34 |

| 6.1 | The Profile and Grouping of Designs                                                                                          | 41 |

| 6.2 | Comparison of Performances of RF and Different ML Models<br>Used in Prior Works                                              | 49 |

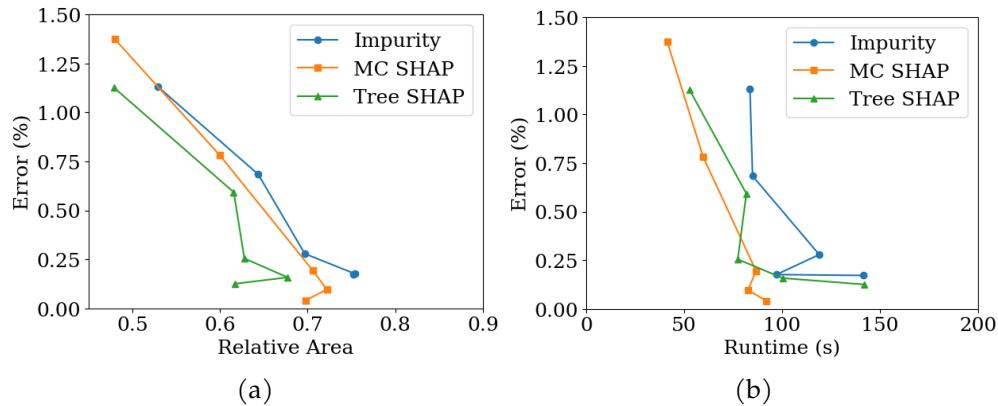

| 7.1 | Comparison of different metrics as splitting criteria                                                                        | 71 |

| 7.2 | Approximation errors, relative area (unitless) and runtimes<br>(in seconds) with different models and an error bound of 0.5% | 80 |

**LIST OF FIGURES**

---

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

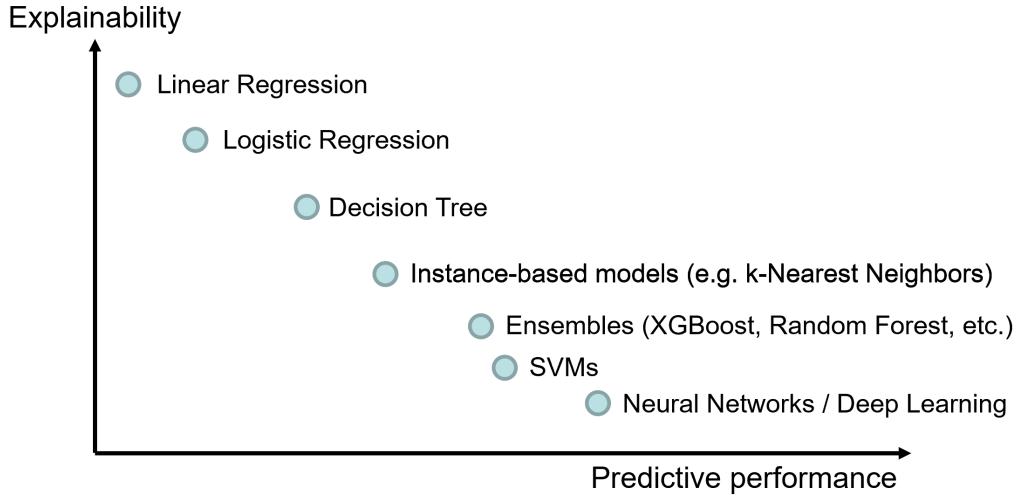

| 1.1 | Tradeoff of predictive performance and explainability of different ML models (not to scale) . . . . .                                                                                                                                                                                                                                                                                                                                                                                                                        | 2  |

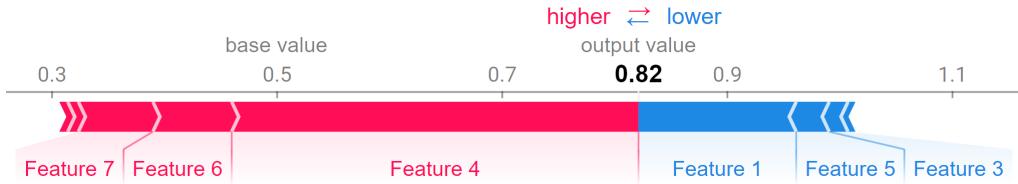

| 4.1 | An example of force plot from SHAP analysis. Six out of nine features (that contribute the most to the final prediction) are labeled. . . . .                                                                                                                                                                                                                                                                                                                                                                                | 13 |

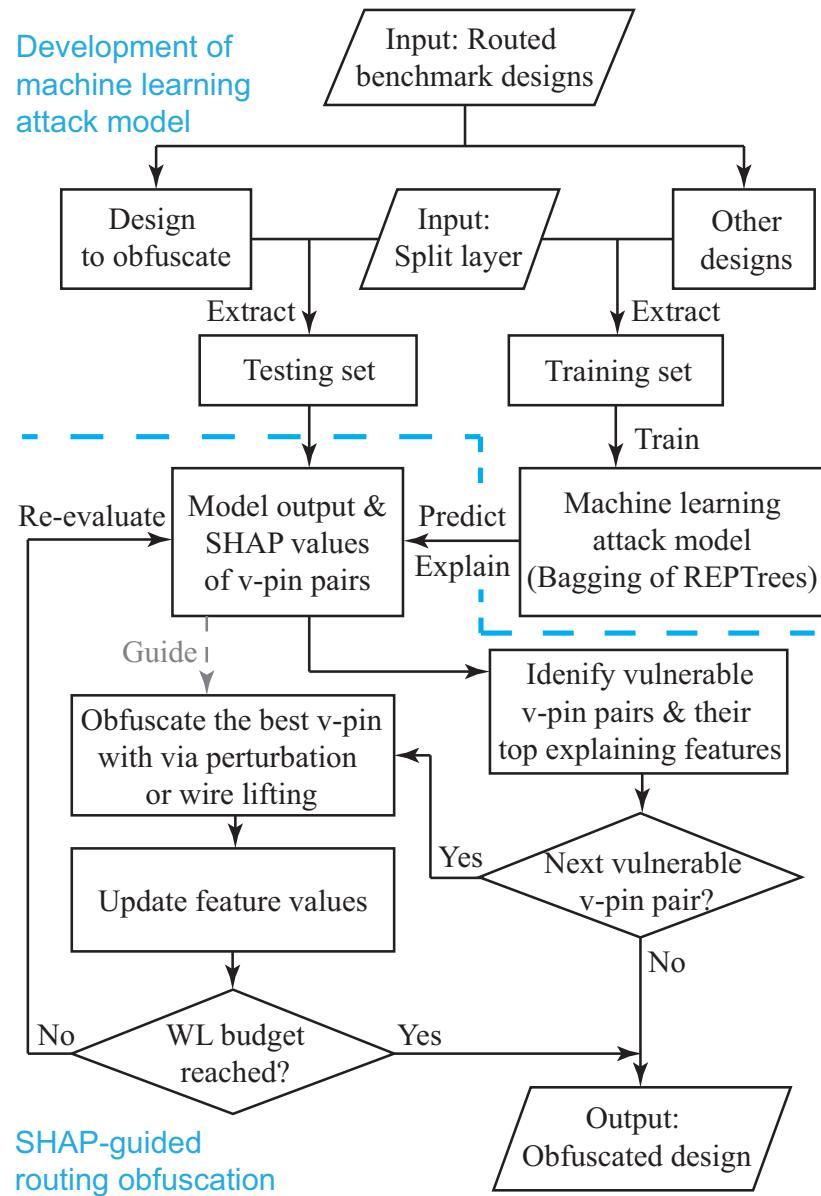

| 5.1 | Flow chart of ObfusX. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 18 |

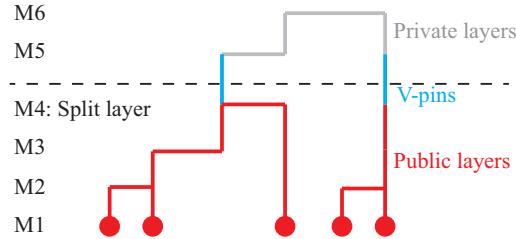

| 5.2 | Illustration of public/private layers and v-pins in split manufacturing. The split layer is M4. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                      | 19 |

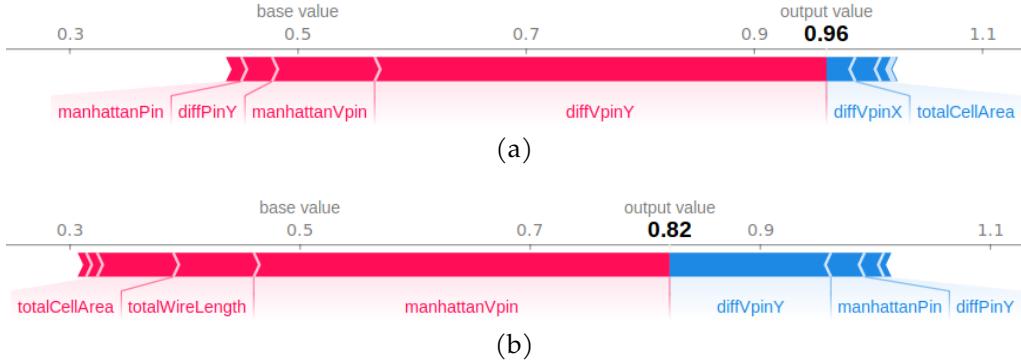

| 5.3 | SHAP force plots of two actually-connected v-pin pairs. The pink/blue bars quantify to what extent each layout feature positively/negatively contributes to the ML attack that predicts their connectivity. The top contributing features (longest pink bars) may vary from one v-pin pair to another. For example, <code>diffVpinY</code> is the most contributing feature in predicting (a) (longest pink bar) while it is actually the most negatively contributing feature to predicting (b) (longest blue bar). . . . . | 22 |

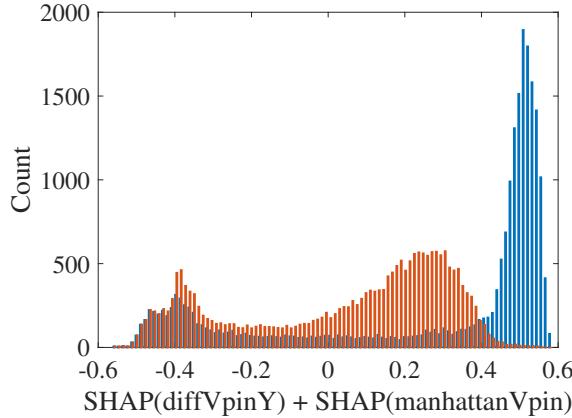

| 5.4 | Contributions of top two features <code>diffVpinY</code> and <code>manhattanVpin</code> , shown as a distribution for all connected v-pin pairs, before (blue) and after (red) obfuscation. ObfusX flattens the distribution and decreases the top contributions. . . . .                                                                                                                                                                                                                                                    | 24 |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

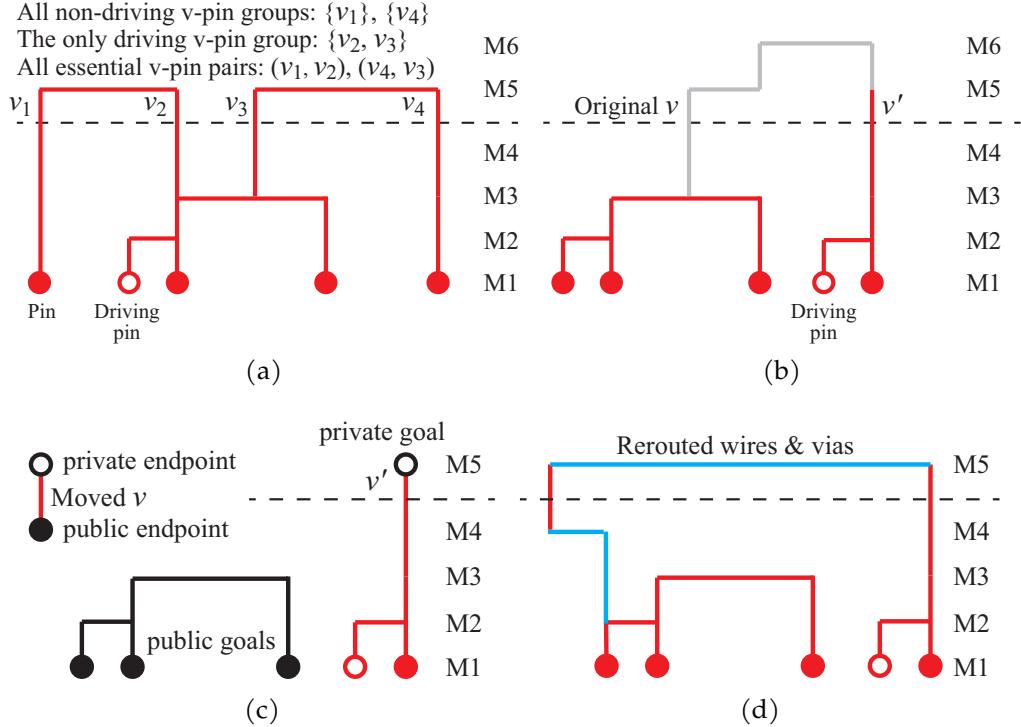

| 5.5 | (a) Illustration of terminology. (b–d) Rip up and reroute for v-pin pair $(v, v')$ when $v$ is perturbed. The horizontal lines in the illustration correspond to wires (which can be in $x$ - or $y$ -direction) and the vertical lines correspond to vias. The dashed lines separate the EOL and BEOL. (b) Original wires and vias of the net containing $v$ and $v'$ ; the gray segments are to be removed. (c) The new location of $v$ after perturbation is identified. The unconnected parts (including both endpoints of $v$ and rerouting goals) are identified in the public layers (shown in black wires and dots) and private layers (shown in black circles). (d) The unconnected parts are reconnected (in blue) using public and private layers respectively, with A* search algorithm in 3D grids. . . . . | 26 |

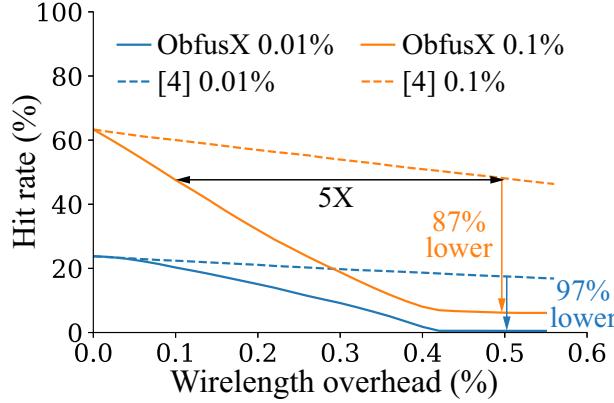

| 5.6 | Comparison of tradeoff in HR vs WL in superblue1. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 34 |

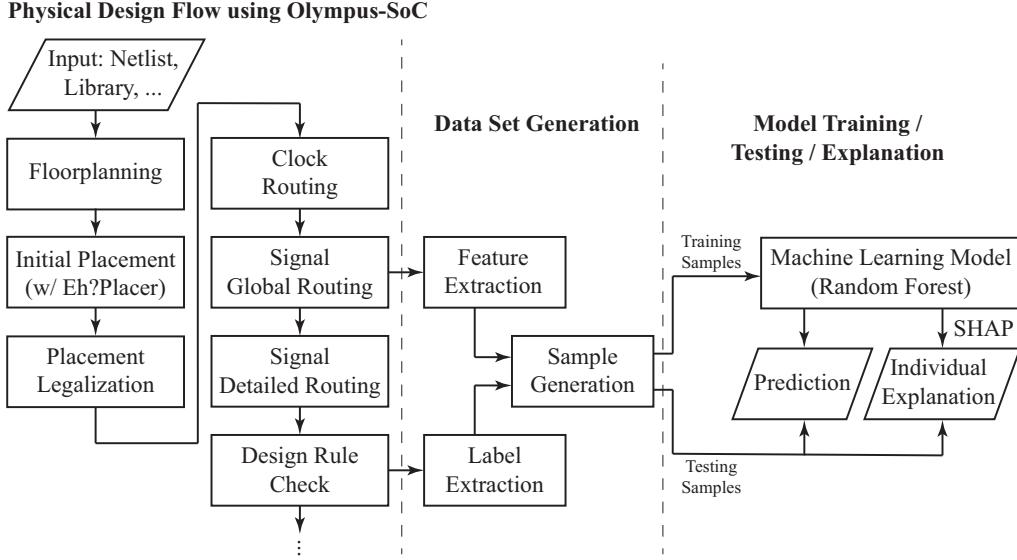

| 6.1 | Workflow of explainable DRC hotspot prediction. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 40 |

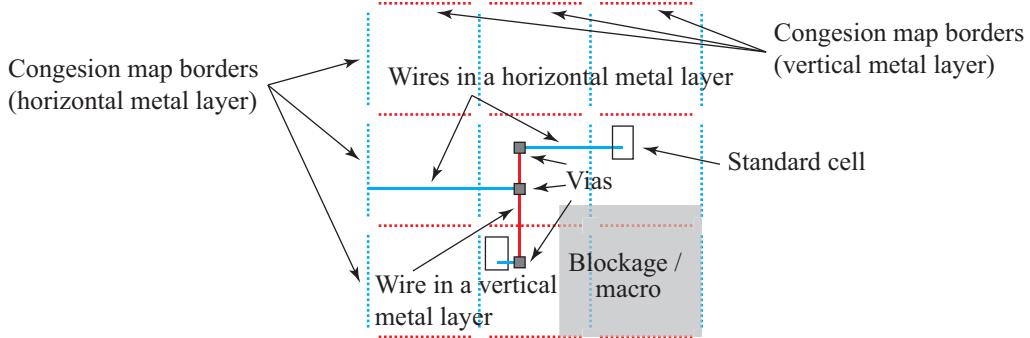

| 6.2 | A $3 \times 3$ g-cell window with standard cells, wires (different colors indicate different metal layers), vias, congestion map borders, blockage/macro. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 42 |

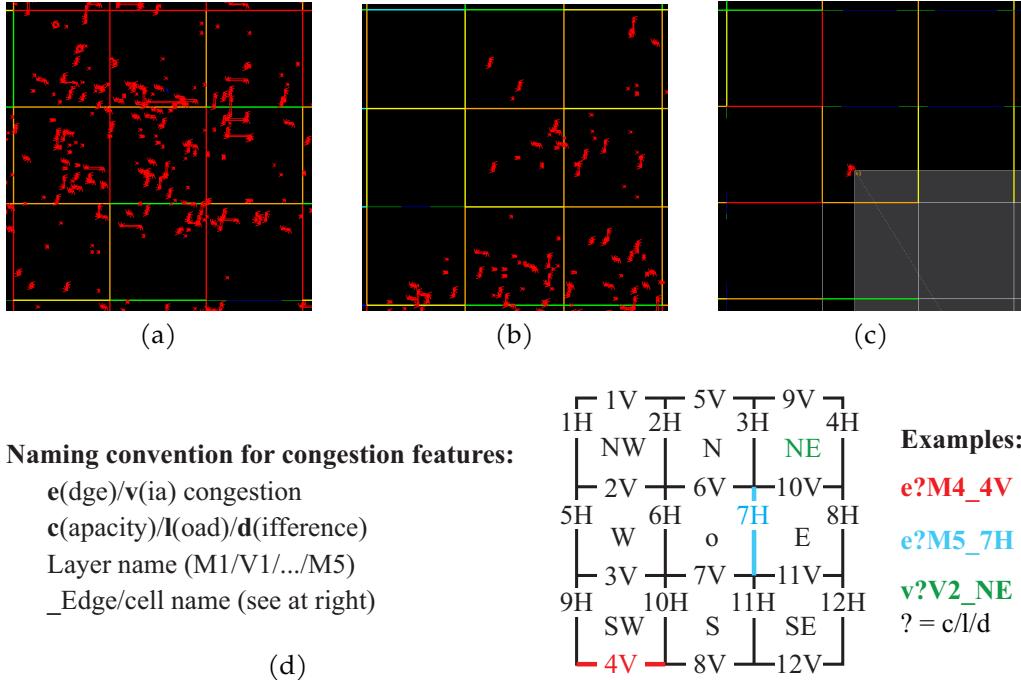

| 6.3 | Example DRC hotspots to be explained. (a) A hotspot in highly congested area from <code>des_perf_1</code> . (b) A hotspot with moderate edge congestion from <code>des_perf_1</code> . (c) A hotspot near a macro from <code>matrix_mult_a</code> . (d) The naming convention for GR congestion features. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 52 |

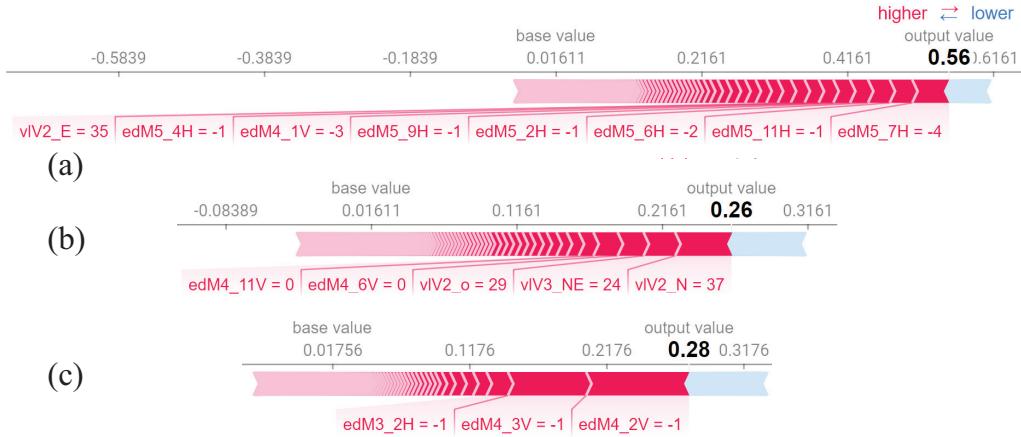

| 6.4 | (a)–(c) Most contributing features for predicting DRC hotspots in Figure 6.3(a)–(c), evaluated by the SHAP tree explainer. (The blue regions on the right contain many features that are not visible as the pink bars dominate.) . . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 53 |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 7.1 | Illustration of building an ADT for ALS using SHAP importance. Steps taken to process a node are illustrated which could be to further split the tree, reach a leaf, or build a subtree at one shot. . . . .                                                                                                                                                                                                                                                                                                         | 63 |

| 7.2 | Logic synthesis flows compared: (a) Exact functionality without constraint in input space (baseline), (b) exact functionality with constraints in input space, and (c) approximated functionality with constraints in input space (proposed). Other synthesis techniques may be applied thereafter to the produced AIGs. . . . .                                                                                                                                                                                     | 64 |

| 7.3 | XOR bit assertion in ADT for $f = x_1 \oplus ((\neg x_2 \wedge f_1) \vee (x_2 \wedge f_2))$ where $f_1$ and $f_2$ are Boolean functions independent of both $x_1$ and $x_2$ . Dash lines are 0 assignments and solid lines are 1 assignments. (a) Not asserting $x_1$ as an XOR bit and instead splitting on $x_1$ would result in two subtrees with opposite polarities. (b) Asserting $x_1$ as an XOR bit, we only need to develop one subtree and take the XOR of $x_1$ and the resulting function $f'$ . . . . . | 67 |

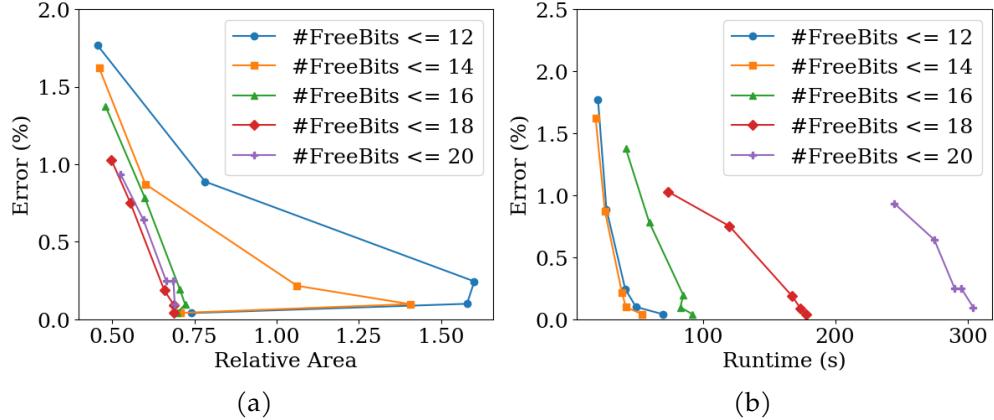

| 7.4 | Comparison of tradeoffs (a) between error and area, and (b) between error and runtime for ADT models with different splitting criteria: impurity, MC SHAP, and Tree SHAP. Values are averaged over all functions. Points on each curve are generated by varying $r$ in $\{128, 256, 512, 1024, 2048\}$ . . . . .                                                                                                                                                                                                     | 81 |

| 7.5 | Comparison of tradeoffs (a) between error and area, and (b) between error and runtime, with MC SHAP and different thresholds for the number of free bits in a node to trigger sample enumeration. Error, area and runtime values are averaged over all functions. Points on each curve are generated by varying $r$ in $\{128, 256, 512, 1024, 2048\}$ . . . . .                                                                                                                                                     | 83 |

**LIST OF ALGORITHMS**

---

|   |                            |    |

|---|----------------------------|----|

| 1 | Via Perturbation . . . . . | 30 |

|---|----------------------------|----|

## 1 INTRODUCTION AND MOTIVATION

---

With the advance of Very Large Scale Integration (VLSI) technology, the design of VLSI circuits becomes more complex, challenging, and time-consuming. Recent years have seen a rising trend of machine learning (ML) applied in different aspects of VLSI design and manufacturing, including accelerating the design flows of logic synthesis, optimization and verification [49, 25, 24], physical design and verification [37, 64, 9], as well as in the fabrication stage, such as yield analysis and improvement [31] and lithographic hotspot detection [71], and also in hardware security, including logic locking [7] and split manufacturing [72]. Overall, the incorporation of ML is making the designs more efficient, robust and secure, thus helping reduce the time-to-market, improve reliability, and protect the intellectual property of the products.

Generally speaking, ML performs prediction tasks based on a trained model, which is derived with a set of training data by a specific algorithm. Depending on the problem, different learning paradigms (e.g., supervised learning, reinforcement learning) and types of models (e.g. logistic regression, decision tree, neural network) may be adopted.

On one hand, due to the high complexity of VLSI design tasks, the adopted ML models usually need to be complex enough to achieve good accuracy. On the other hand, in practice, it is always desirable for designers and managers to understand what happens behind the ML model. They may raise questions like, why the model predicts a design failure with a specific parameter set, why the model predicts a lithographic hotspot at a specific location, why the design is predicted as not secure at a specific gate, etc. Therefore, problems of root causing and trustworthy may arise when a ML model is too complex to understand why it predicts a specific data point as such.

In general, the predictive performance of a model is positively corre-

Figure 1.1: Tradeoff of predictive performance and explainability of different ML models (not to scale).

lated to its complexity, which in turn is negatively correlated to its explainability. This results in a negative correlation of predictive performance vs explainability, as notationally illustrated in Figure 1.1.

Different from pure ML, Explainable Artificial Intelligence (XAI) is an emerging technique that aims to perform predicting tasks and provide *explanations* for the predictions simultaneously. In other words, XAI tries to move the points in Figure 1.1 upwards for a better tradeoff of predictive performance vs explainability.

Besides providing better human understanding and attribution, XAI also enables better exploitation of the model. For example, with the understanding of *why* a design is predicted not secure at a certain location, designers know how to enhance the security in the most effective manner, whereas a pure ML prediction may not provide such insights.

Based on this idea, we propose three novel techniques from different aspects of VLSI computer-aided design (CAD) that utilize XAI, including routing obfuscation for enhanced security for split manufacturing,

explainable prediction of design rule check (DRC) violation hotspots in early stages of physical design flow, and a sampling-based approximate logic synthesis technique powered by explainable ML.

In the remainder of this dissertation, we first give an overview of the related works in Chapter 2. Chapter 3 summarizes the contributions of this dissertation. Chapter 4 introduces Shapley Additive Explanations (SHAP)—the technical basis of explanatory analysis adopted throughout this dissertation. In Chapters 5 through 7, we show the three proposed techniques as applications of XAI in VLSI design, focusing on hardware security, layout routability, and approximate logic synthesis, respectively.<sup>1</sup> Finally, in Chapter 8, we conclude this dissertation and discuss future directions.

---

<sup>1</sup>These chapters are slightly modified versions of works [74, 73, 75] published or to be published in conference proceedings, and have been reproduced here in accordance with the permission of the copyright holders.

## 2 RELATED WORKS

---

In this chapter, we first give an overview of related work on applying ML in the VLSI design flow. We note, none of these existing works utilize explainability. Next, we give an overview of existing techniques on explaining ML models in general (and not in the field of VLSI design).

### 2.1 ML Applications in VLSI Design

ML has been applied in different aspects of VLSI design: to accelerate the design flows, to analyze and improve the robustness in design and manufacturing, and to analyze and enhance the design security against reverse engineering and intellectual property theft.

#### 2.1.1 For Efficient Design Flows

ML plays a role in almost every stage of the VLSI design flow in both front end and back end [28], including logic synthesis, technology mapping, logic optimization, logic verification, placement, and routing. One common usage of ML is to predict the results of a design stage and/or its downstream stages in the design flow, thus reducing the overall runtime of the design flow.

In logic synthesis and optimization, Rokach *et al.* proposed a decision-tree-based circuit decomposition engine for logic synthesis [49]. Pasandi *et al.* proposed a technology mapping approach for approximate logic synthesis based on deep reinforcement learning [41]. Deep reinforcement learning has also been adopted for logic optimization [25, 79]. In logic verification, techniques that accelerate functional coverage closure have been proposed using multiple ML models [24]. Different types of neural networks have been adopted for analyses of testability [35], power [76],

signal integrity [15]. In physical design, deep learning and reinforcement learning have been applied to chip placement and legalization [37, 39]. There are works on predicting the routability, in particular, design rule violations, before the detailed routing stage using different ML models [9, 55, 54, 12, 64]. Besides, ML has been used to automate the design space exploration [32] and tuning of flow parameters [63], which helps reduce the design turnaround time.

### 2.1.2 For Robust Fabrication

For chip fabrication, ML has been applied in VLSI testing [65], yield analysis and optimization of integrated circuits (ICs) [31, 1, 11, 30]. For VLSI in particular, recent focuses are on lithographic modeling and hotspot detection [71, 67, 47], and mask optimization [69, 68].

### 2.1.3 For Hardware Security

ML has also been applied in the community of hardware security [22], especially in the analysis of spectre attacks [77], IC counterfeit [29], IC reverse engineering [3], logic encryption [7, 53], and split manufacturing [72], etc.

## 2.2 Studies on Explaining ML Models

There are different methods of explaining the prediction of a ML model to humans [2, 38]. Given a specific prediction/decision from the model, one way to explain it is to analyze important features that contributes most to a specific prediction [48, 34]. Other methods include training an approximated model that has higher explainability [18], learning a separate explanatory model from human-provided explanations [27], etc.

In this proposal, we will focus on the first method, i.e., the attribution of features in predicting a specific data sample. LIME [48] and SHAP [34] are among the most famous explanatory frameworks in this category. They explain individual predictions by evaluating the effects of different features in inferring on each specific data sample. Next, we give a brief overview of these methods.

### 2.2.1 Local Interpretable Model-Agnostic Explanations (LIME)

LIME [48] is the first work in this category. It finds a local linear approximation of the prediction, such that the most important features for predicting a specific data sample can be identified by observing the coefficients of the linear approximation. In other words, it estimates how much the prediction will change if a feature value changes in its vicinity.

However, LIME is based on local linearity of the ML model, and assumes no interactions among different features. Therefore, it may be inaccurate where the model is complex and/or some features are correlated, as is often the case in practice. To address these, Lundberg *et al.* proposed another additive explanation method named SHAP [34], which does not rely on these assumptions.

### 2.2.2 Shapley Additive Explanations (SHAP)

SHAP [34] is based on the concept of Shapley value in game theory. It seeks a linear decomposition of contributions made by each feature in predicting a specific data sample. By exploiting the definition of Shapley value, SHAP is reported to be more accurate and more consistent with human intuition, though computationally expensive to calculate exactly. To alleviate the runtime while preserving the accuracy, SHAP tree explainer [33] is later proposed as an extension specifically for tree-based ML models.

This dissertation will be utilizing SHAP analysis in later chapters. More details on SHAP analysis will be provided in Chapter 4.

### 3 SUMMARY OF CONTRIBUTIONS

---

In this dissertation, we propose three techniques where XAI is applied in different aspects of VLSI CAD, including logic synthesis, physical design, and hardware security for higher efficiency and effectiveness. To date, the idea of incorporating XAI into VLSI CAD is novel and of great interest to both academia and industry. Specifically, our contributions are summarized as follows.

#### **Routing Obfuscation Guided by Explanatory Analysis of a ML Attack**

Split manufacturing is a technique to protect the intellectual property related to a design from being stolen by an untrusted foundry, where only a partial layout (e.g., patterns in lower layers) is revealed to an untrusted foundry. Given a lower part of the layout (up to a predefined split level), the ML attack model in [72] tries to find whether a pair of broken vias at the split level are connected in higher metal and via layers that are not available to the attacker.

To thwart this attack, we propose a routing obfuscator that incorporates explanatory analysis on a recent attack powered by a tree-based ML model [72]. The proposed routing obfuscator is to thwart this kind of attack. While the ML attack model reveals that routing features like Manhattan distance of two broken vias are the most important features overall in the attack, it may not be the case for the entire layout of the design. With XAI on the attack model, we can obfuscate the layout and thwart the attack in a more precise and effective manner — we can not only identify and focus on the most vulnerable pairs of vias, but also obfuscate them by just the necessary amount, thereby reducing the overhead while having better performance of obfuscation. Specifically, we propose to adopt SHAP tree explainer [33] to evaluate the feature importance of each pair of vias at or one level below the split level. This explanatory result can guide us not

only to identify the most vulnerable ones to the attack, but also to derive the most “efficient” amount to alternate the location or layer of the vias for obfuscation purposes.

**Explainable Prediction of DRC Violation Hotspots** In VLSI physical design, detail routing is the most time-consuming step, which could take up to days for each run. Several works address this issue by predicting DRC violation hotspots in early design stages. However, they mainly focused on the predictive performance, without providing the reason why it is predicted as a DRC violation hotspot and how to possibly fix it. In fact, from the perspective of designers and project managers in practice, the reason behind a potential violation hotspot is more important than the prediction itself, which pure ML cannot provide.

As one of the applications of XAI, we propose to combine random forest and SHAP tree explainer to build an explainable predictor of DRC violation hotspots in VLSI physical design, based on information from early design stages (e.g. placement and global routing). With XAI powered by SHAP tree explainer, we can figure out the most important features, which can be interpreted as specific key factors for each predicted DRC violation hotspots, such as the overflow of a certain edge in the congestion map, high pin density at a specific location, etc. Designers can use this information to make local adjustments in placement and routing that help alleviate the violations if they are fixable. Since all of these happen before the most time-consuming step of detailed routing, both the length and numbers of design iterations could be reduced, which potentially translates to much faster time-to-market.

**Approximate Logic Synthesis Guided by Explainable ML** Approximate logic synthesis (ALS) is the process of generating a Boolean circuit that approximates the functionality of an original circuit within a tolerance of error, in trade of better quality of results (usually a smaller area, power

and/or delay). Many ALS techniques have been proposed in the past decades [51].

A specific subset of ALS techniques (e.g., [40]) construct an approximate circuit only based on samples of input-output pairs (i.e., entries in a truth table), which are generally achieved by learning a function that generalizes these samples. We refer to this subset of techniques as *sampling-based ALS* in this dissertation. Sampling-based ALS is drawing increasing research interest, as many promising studies and interesting contests are conducted in recent years [10, 13, 4, 52, 45].

As one of the applications of XAI in this field, we proposed a novel sampling-based ALS framework with focus on utilizing explainable ML. We formulate the approximation of a Boolean function as a supervised ML problem, and propose to use explainable ML to guide the model training. Specifically, we measure the importance of each individual primary input bit with respect to the function output based on the SHAP values, which we further utilize to achieve an efficient implementation of Boolean function approximation with minimal loss in accuracy.

## 4 PRELIMINARIES

---

In this dissertation, we adopt SHAP [34], a recently proposed explanatory model that explains predictions from a ML model. This chapter introduces the technical basis of SHAP.

### 4.1 Shapley Value and SHAP

SHAP [34] is a recent advance in ML community. It is based on Shapley value—a concept from game theory.

Shapley value was originally proposed to quantify the contribution of a player in a cooperative game of  $n$  players. Let  $v(S)$  be the value generated by the cooperation of players in set  $S \subseteq N = \{1, 2, \dots, n\}$  with  $v(\emptyset) = 0$ , then the Shapley value (contribution) of player  $j$  is defined as

$$s(v, j) = \sum_{S \subseteq N \setminus \{j\}} \frac{|S|!(n - |S| - 1)!}{n!} \cdot [v(S \cup \{j\}) - v(S)]. \quad (4.1)$$

Shapley value has many desirable properties. One of them is that the sum of all Shapley values of individual players equals the value generated by the cooperation of all players, formally

$$\sum_{j=1}^n s(v, j) = v(N). \quad (4.2)$$

Based on this property, SHAP was proposed as an additive explanation of a ML prediction. Let  $f(\mathbf{x}^*)$  be the ML prediction output for a data instance  $\mathbf{x}^* \in \mathbb{R}^n$ . In SHAP, the cooperation value  $v(S)$  is defined as the expected change in prediction output conditioned on feature values indexed by  $S$ .

$$v(S) \equiv \mathbb{E}[f(\mathbf{x}) \mid x_S^*] - \mathbb{E}[f(\mathbf{x})], \quad (4.3)$$

where we denote  $\mathbb{E}[f(\mathbf{x}) \mid x_S^*] = \mathbb{E}[f(\mathbf{x}) \mid x_j^*, \forall j \in S]$  for simplicity.

The *SHAP value* of a feature  $j$  in predicting  $\mathbf{x}^*$  is defined by substituting (4.3) in (4.1),

$$c(\mathbf{x}^*, j) = \sum_{S \subseteq N \setminus \{j\}} \frac{|S|!(n - |S| - 1)!}{n!} \cdot \left\{ \mathbb{E}[f(\mathbf{x}) \mid x_{S \cup \{j\}}^*] - \mathbb{E}[f(\mathbf{x}) \mid x_S^*] \right\}. \quad (4.4)$$

Substituting (4.3) in (4.2), we have

$$f(\mathbf{x}^*) = \mathbb{E}[f(\mathbf{x})] + \sum_{j=1}^n c(\mathbf{x}^*, j). \quad (4.5)$$

The above equation reveals the essential idea of SHAP—decomposing the prediction output  $f(\mathbf{x}^*)$  as the sum of a base value and contributions from each individual feature. Specifically, the base value  $\mathbb{E}[f(\mathbf{x})]$  is the expected prediction based on all training data, and  $c(\mathbf{x}^*, j)$  is the contribution of feature  $j$  of instance  $\mathbf{x}^*$ . Each contribution  $c(\mathbf{x}^*, j)$  can be positive, negative, or zero, which indicates how (and how much) feature  $j$  makes the prediction of this specific instance deviate from the average.

## 4.2 SHAP Tree Explainer for Tree-Based ML Models

Derived from Shapley values, SHAP values in (4.4) have unique properties that lead to consistent explanations [34]. However, exact evaluation of SHAP values is computationally expensive in general due to the exponential time complexity. Therefore, estimations are generally needed in practical use. A recent extension [33], referred to as *SHAP tree explainer*, shows that the *exact* evaluation of SHAP values can be done in polynomial time exclusively for tree-based models (e.g., decision tree, random forest). The SHAP tree explainer does not assume feature independence, as feature

Figure 4.1: An example of force plot from SHAP analysis. Six out of nine features (that contribute the most to the final prediction) are labeled.

interactions are already captured in the underlying trees.

### 4.3 Examples of SHAP Analysis

In this section, we use an example to show how SHAP analysis works. It can work in different modes. We demonstrate two usages that will be applied in this dissertation.

#### 4.3.1 Explaining a Single Prediction

Suppose in a classification problem, each data instance includes 9 features  $x_1, \dots, x_9$  and the output class  $y \in \{0, 1\}$ . In the training data set, a half of the instances are of class  $y = 1$ . A ML model is trained with the training data set and is being used to predict a specific data instance. In this situation, we can gather the base value (the average prediction) and the SHAP values of each feature as defined in (4.4), and visualize them as a *force plot* in Figure 4.1.

In this example, the base value is 0.5 (the same value throughout all data instances), and the prediction of this specific data instance is 0.82. The pink (resp. blue) bars correspond to features that positively (resp. negatively) contribute to this prediction. The lengths of the bars indicate the absolute values of such contributions (i.e. SHAP values). For example, Feature 4 is the most positively contributing feature, indicated

by the longest pink bar; Feature 1 is the most negatively contributing feature, indicated by the longest blue bar. Three features that have the smallest contributions (i.e., with the shortest bar lengths on both sides) are not labeled due to space limit. Per (4.5), all bar lengths of positive contributions minus those of negative contributions should equal  $d = 0.82 - 0.5 = 0.32$ , i.e., the difference of this prediction and the average prediction. The name “force” comes after the metaphor that each feature “pushes” the final prediction from the base value, in the direction indicated by the sign of its SHAP value, by the amount of the magnitude of its SHAP value. The total effect of these “forces” is to push its prediction result from the (common) base value 0.5 to the (instance-specific) output value 0.82.

### 4.3.2 Comparing Feature Importance

Besides individual explanation, when SHAP is applied to a batch of  $M$  instances, we can estimate the *SHAP importance* of each feature. This is done by examining the mean absolute value of SHAP values of a feature implied by the instances. Specifically, the SHAP importance of feature  $j$  is defined as

$$Q(j) = \mathbb{E}_{\mathbf{x}} |c(\mathbf{x}, j)| \approx \frac{1}{M} \sum_{i=1}^M |c(\mathbf{x}^{(i)}, j)|, \quad (4.6)$$

where  $\mathbf{x}^{(i)}$  is the  $i$ -th instance. Studies have shown that conventional (e.g., impurity-based) feature importance metrics can be biased and not reliable [50], and that SHAP importance is more consistent [33] owing to the properties of Shapley values it bases on.

## 5 ROUTING OBFUSCATION GUIDED BY EXPLANATORY ANALYSIS OF A ML ATTACK

---

While recent advances in VLSI manufacturing technology keep pushing the performance boundaries of integrated circuits, the cost of fabricating high-end chips also surges. Consequently, manufacturing outsourcing of VLSI has become more common than ever before. As a result, security issues including design piracy and hardware Trojans injection may arise when an untrusted foundry is involved in manufacturing. To alleviate these problems, split manufacturing is proposed as a technique where the untrusted foundry only receives and fabricates a partial layout up to a metal layer (called a “split layer”). However, this may still not prevent an attacker to extract the full design, if the layout is not obfuscated or if the split layer is too high, as suggested by [46, 59, 36, 72, 58, 66].

### 5.1 Related Works on Layout Obfuscation

Existing techniques on layout obfuscation may be classified as two categories: placement-based and routing-based. Placement-based techniques include pin swapping [46], cell insertion [62], and cell location perturbation [59]. Routing-based techniques include routing blockage insertion [36], routing perturbation [60], and wire lifting [43]. The two techniques may also been combined, as in [42].

The key idea of design obfuscation for split manufacturing is to make an attack model fail to identify correct connections above the split layer. As for the attack models for split manufacturing, Rajendran *et al.* first proposed the proximity attack [46]. Wang *et al.* proposed a more advanced network-flow-based proximity attack [59], which employs the network flow model that considers more heuristics for better attack performance. Magaña *et al.* proposed a congestion based attack [36], which redefined proximity

measures based on the observation that placement and routing congestions are better indicators in large commercial designs. Recently, a ML-based attack model [72] is proposed, which is trained with empirically-selected layout features that reflect the hints from routing conventions.

In this chapter, we present a novel way to build an obfuscator for split manufacturing based on XAI. We adopt SHAP to analyze the ML attack model in [72]. This ML attack model is especially suitable for large commercial designs while other attack models (e.g. [59]) would take prohibitively long attack time.

The SHAP-based analysis reveals to what extent *each* layout feature contributes to correctly predicting *each* individual unknown connection as seen by an untrusted foundry. We then exploit this information to design a SHAP-guided obfuscator against the ML attack model where only truly vulnerable connections are identified and each is obfuscated by just the necessary amount. This results in minimal perturbation to the layout as measured by increase in wirelength and number of perturbed nets. Our obfuscator (named ObfusX) is routing-based and is performed by utilizing via perturbation and wire lifting schemes. (Placement-based obfuscation was not found to be as effective by our SHAP-based analysis.)

ObfusX sets an example of how XAI can be used to obfuscate a design; while we focus on routing obfuscation for a ML-based split manufacturing attack, our approach is generalizable to build any obfuscator as long as a ML attack model is available. We demonstrate the benefits of ObfusX in identifying and focusing on the most vulnerable candidates and obfuscating each by just the right amount, thereby reducing the obfuscation overhead, while having better performance. Our results are compared with two prominent prior works, using not only the ML attack [72], but also an independent network flow-based attack from a recent work [59].

## 5.2 Overview of SHAP-Guided Routing Obfuscation

The core idea of a SHAP-guided obfuscation is to perturb the design, such that a ML attack model would perform worse. As we will show in experiments, such obfuscation also performs well under an independent, non-ML attack model [59]. A flow chart of the overall process of ObfusX is shown in Figure 5.1.

The upper panel shows how the ML model is developed. To generate the training set and testing set for a design to obfuscate (i.e., “target design”), we generate data samples by extracting layout features from routed designs, with the same split layer applied as will be used in manufacturing. All data samples from the target design are allocated in the testing set, which we will use to monitor the progress and performance of obfuscation. Other designs in the same benchmark suite as the target design are used to generate the training set that will be used to train the attack model. ObfusX uses the ML predictor in [72], whose details will be summarized later in Section 5.3. With a trained attack model, it predicts how likely each pair of (two) v-pins in the target design could be a match (i.e., are actually connected), which can be interpreted as the vulnerability of the pair to the ML attack.

To develop ObfusX, as shown in the lower panel, the ML prediction for a v-pin pair is fed to the SHAP tree explainer, which generates a set of SHAP values to explain the prediction.

Each SHAP value corresponds to an extracted feature and quantifies to what extent that feature contributes to the ML predictor for that specific v-pin pair. These SHAP values are next analyzed across all actually-connected v-pin pairs to identify the most vulnerable ones to the ML attack, along with the layout features that contribute the most to their individual vulnerabilities.

Figure 5.1: Flow chart of ObfusX.

Figure 5.2: Illustration of public/private layers and v-pins in split manufacturing. The split layer is M4.

Next, the output of SHAP analysis guides the actual obfuscation which is done iteratively. ObfusX utilizes two layout perturbation techniques—via perturbation and wire lifting—each of which effectively change the routing and locations of a vulnerable v-pin pair. At each iteration, the most vulnerable v-pin pair is obfuscated if its obfuscation does not violate routing feasibility. Next, the feature vector of the obfuscated pair is updated and consequently its vulnerability is re-evaluated by the attack model (given that the layout has been slightly perturbed). ObfusX then proceeds to obfuscate the next vulnerable pair, until there is no more vulnerable pair, or a budget of wirelength (WL) overhead is reached.

### 5.3 ML Attack Model for Split Manufacturing

To build an obfuscator, we use SHAP explanatory analysis to break a ML-based attack. Here, we review the ML attack model used by our work.

Given a metal layer as the split layer, the layout is partitioned into public layers, v-pins (as termed in [72]) and private layers from low to high levels. Specifically, as illustrated in Figure 5.2, a *split layer* refers to the topmost metal layer available to the attacker; *public layers* refer to all metal on or below the split layer and via layers in between; *private layers* are all metal layers above the split layer and the via layers in between; *v-pins* are vias connecting public and private layers. The attacker has access to the

layout (cells, pins, wires, vias) in public layers and all v-pins. The goal of the split manufacturing attack is to predict the connectivity on private layers based on the available layout on public layers.

Recently, a ML-based attack model was proposed for split manufacturing in [72]. To build the ML model, for each pair of v-pins in a design, first a vector of layout “features” was extracted from the public layers. Using these features, the ML model was built based on Bagging of 10 reduced error pruning trees (REPTrees) in Weka [23]. The ML model mapped each v-pin pair with feature vector  $\mathbf{x}$  to a probability  $f(\mathbf{x}) \in [0, 1]$ , indicating how likely the v-pin pair is a “match” (i.e. actually connected to each other on private layers).

For each v-pin  $v$ , we record the the v-pin’s coordinates on the split layer, denoted by  $(vx, vy)$ . We compute wirelength  $W$  for the route fragment that connects  $v$  to one or more pins of standard cells on the underneath placement layer. We also calculate the location where the v-pin connects on the placement layer, which we denote by  $(px, py)$ . If the connection is to multiple pins on the placement layer, the location is computed by averaging the coordinates of pins of the standard cells that connect to  $v$ . We also record the areas of its driving cells and its loads in the placement layer that connects to the v-pin, denoted  $OutArea$  and  $InArea$ , respectively.

Then for a pair of v-pins, we consider the following features extracted in [72]. These features are used to train the ML attack model.

- $DiffPinX = |px_1 - px_2|$ : This feature records the difference in the  $x$ -coordinates of the pins on the placement layer which connect to the two v-pins.

- $DiffPinY = |py_1 - py_2|$ : Same as the previous feature except calculated using the  $y$ -coordinates.

- $ManhattanPin = |px_1 - px_2| + |py_1 - py_2|$ : Same as the previous feature except it is calculated based on the pin locations on the placement

layer.

- $\text{DiffVpinX} = |vx_1 - vx_2|$ : This feature records the difference in the  $x$ -coordinates of the two v-pins.

- $\text{DiffVpinY} = |vy_1 - vy_2|$ : Same as the previous feature except calculated using the  $y$ -coordinates.

- $\text{ManhattanVpin} = |vx_1 - vx_2| + |vy_1 - vy_2|$ : This feature records the Manhattan distance between two v-pins.

- $\text{TotalWirelength} = W_1 + W_2$ : This is the known wirelength connecting the v-pin pair below the split layer.

- $\text{TotalArea} = \text{InArea}_1 + \text{InArea}_2 + \text{OutArea}_1 + \text{OutArea}_2$ : This records the sum of cell areas connecting to the two v-pins.

- $\text{DiffArea} = (\text{OutArea}_1 + \text{OutArea}_2) - (\text{InArea}_1 + \text{InArea}_2)$ : This feature calculates the area difference of the driving cells from its loads.

In this application, we will use SHAP tree explainer on this ML model to analyze the vulnerability of individual v-pin pairs to the attack, and use it to guide the obfuscation.

## 5.4 SHAP Analysis for One V-pin Pair

Before discussing the details of ObfusX, we first explain how SHAP-based analysis is performed for a single pair of connected v-pins. This helps us to illustrate the true benefits of such analysis in building ObfusX.

Consider two connected v-pins from the design *superblue1* with split layer M6. The ML attack model, predicts the first pair to be connected with probability 0.96 (which is a relatively high prediction indicating a successful attack if there is no obfuscation). Figure 5.3(a) shows the *force plot*

Figure 5.3: SHAP force plots of two actually-connected v-pin pairs. The pink/blue bars quantify to what extent each layout feature positively/negatively contributes to the ML attack that predicts their connectivity. The top contributing features (longest pink bars) may vary from one v-pin pair to another. For example, `diffVpinY` is the most contributing feature in predicting (a) (longest pink bar) while it is actually the most negatively contributing feature to predicting (b) (longest blue bar).

generated by SHAP analysis performed on the ML prediction for this pair. The color and length of pink/blue bars show the signs and magnitudes of each contribution  $c(\mathbf{x}, j)$  in Equation (4.5), respectively. For the pair in Figure 5.3(a), the analysis breaks down the prediction output of 0.96 as sum of a base value of 0.5 and a total deviation of +0.46. The pink/blue bars correspond to the features which positively/negatively contribute to the model output (i.e., with a positive/negative “force” pushing towards this 0.96 prediction). The length of the bars indicate the degree of contribution such that the sum of the lengths of pink bars (with positive sign) and blue bars (with negative sign) adds up to +0.46.

More specifically, for pair (a), among all its features, `diffVpinY` has the highest SHAP value of around +0.4 (corresponding to the length of its pink bar). Figure 5.3(b) shows the force plot for a second pair (b). For pair (b), we observe a different feature, i.e., `manhattanVpin` is dominant. Moreover, `diffVpinY`, which was the top feature in (a), has a negative

SHAP value in (b), indicating it actually contributes negatively to the prediction of pair (b).

In fact, for pair (a), if we were to increase the values of `diffVpinY` and `manhattanVpin` by the size of one routing grid (which simulates a via perturbation in  $y$  direction), the output (i.e., the probability of matching) from the ML attack model would drop significantly from 0.96 to 0.37. However, if the same were done for pair (b), the model output would only have a small drop from 0.82 to 0.64. It confirms that `diffVpinY` is a useful feature from an obfuscation perspective for pair (a), but is less useful for pair (b).

The above example yields the following two key observations to illustrate the unique benefits of SHAP analysis for obfuscation:

1. The vulnerable v-pin pairs can be identified as the ones which have few features with large positive SHAP values.

2. The top feature may vary across individual pairs, implying a different degree or scheme of obfuscation is needed for each.

These observations motivate us to develop `ObfusX`, a SHAP-based obfuscator which decides, precisely, how much each v-pin pair should be uniquely obfuscated for most efficiency.

## 5.5 Details of SHAP-Guided Routing Obfuscation

The goal of SHAP-guided obfuscation is to alter the SHAP values such that there will not be any dominant feature with a high positive SHAP. It could mean that obfuscation makes originally dominant features to have a lower positive SHAP value or a negative one.

Figure 5.4: Contributions of top two features `diffVpinY` and `manhattanVpin`, shown as a distribution for all connected v-pin pairs, before (blue) and after (red) obfuscation. `ObfusX` flattens the distribution and decreases the top contributions.

Our SHAP analysis of design `superblue1` with split layer M6 shows that, for about half of the connected v-pin pairs, the SHAP value of `diffVpinY` is consistently dominant (followed by that of `manhattanVpin`). However, for the other half of pairs, the distribution of SHAP values over features becomes fuzzy, which suggests that no single feature dominates the model. Such pairs (which do not have any dominant feature) do not need to be obfuscated.

For the two dominant features (`diffVpinY` and `manhattanVpin`) in the above example, Figure 5.4 shows the distribution of the combined contribution (i.e., sum of SHAP values) of these two top features, before and after obfuscation. This is when using `ObfusX` with via perturbation (which will be discussed in detail in Section 5.5.1). The before-obfuscation distribution is shown in blue and the after-obfuscation one is shown in red. As can be seen, `ObfusX` flattens the distribution and shifts it to the left (so it decreases the top contributions, making some less positive and some even negative).

Similar to the example of `superblue1` with split layer M6, SHAP-based analysis with the rest of the designs showed that `diffVpinY` and `manhattanVpin` are always the top two contributing features for many of the vulnerable nets when the split layer is even. (For odd split layers, `diffVpinY` should be replaced by `diffVpinX` because wires are preferred to route vertically on even layers and horizontally on odd layers.) The nets which did not have a dominant feature simply will not need to be obfuscated with SHAP-guided analysis. Therefore, these two features are the only ones utilized by `ObfusX`.

We note, these two dominant features are related to routing which explains our choice to obfuscate the design with routing-based techniques, i.e., via perturbation and wire lifting. However, we note, our general approach is not restricted to routing.

Next, we explain the two routing-based techniques used by `ObfusX`.

### 5.5.1 **ObfusX with Via Perturbation**

The procedure for via perturbation only considers perturbing v-pin pairs which are determined to be “essential”. Essential v-pin pairs are a subset of all connected v-pin pairs, after disregarding trivial cases, e.g., when some v-pins connect to each other using the public layer, which are easily identifiable by the attacker. `ObfusX` also ensures feasibility of the routing throughout the process without any area overhead. We first introduce the following which will be used when explaining the algorithm.

#### 5.5.1.1 **Terminology**

We introduce the following terminology as shown in Figure 5.5(a), where the split layer is M4, public layers are M1 through M4, and private layers are M5 and M6. Wires in all metal layers are shown as horizontal lines and vias as vertical lines.

Figure 5.5: (a) Illustration of terminology. (b-d) Rip up and reroute for v-pin pair  $(v, v')$  when  $v$  is perturbed. The horizontal lines in the illustration correspond to wires (which can be in  $x$ - or  $y$ -direction) and the vertical lines correspond to vias. The dashed lines separate the EOL and BEOL. (b) Original wires and vias of the net containing  $v$  and  $v'$ ; the gray segments are to be removed. (c) The new location of  $v$  after perturbation is identified. The unconnected parts (including both endpoints of  $v$  and rerouting goals) are identified in the public layers (shown in black wires and dots) and private layers (shown in black circles). (d) The unconnected parts are reconnected (in blue) using public and private layers respectively, with A\* search algorithm in 3D grids.

A *driving pin* is a pin that drives other components in the net. It can be the output pin of a logic cell or that of a primary input. Note that there is exactly one driving pin in each net, unless in rare cases where tri-state logic is involved.

A *v-pin group* consists of v-pins in the same net that connect to each other using public layers. The v-pins in the same group can be easily identified by an attacker because they are connected in public layers that are available to the attacker.

A *driving v-pin group* is a v-pin group that connects to a driving pin using public layers. In general, since each net has exactly one driving pin, there is exactly one driving v-pin group in each net.

A *non-driving v-pin group* is a v-pin group that does not connect to any driving pin in public layers.

An *essential v-pin pair*  $(v, v')$  consists of a pair of v-pins, where  $v$  is in a non-driving v-pin group  $G$ , and  $v'$  is in a driving v-pin group  $G'$ . If  $G'$  has more than one v-pin,  $v'$  is the closest v-pin to  $v$  in  $G'$ .

### 5.5.1.2 Algorithm

We propose an algorithm that perturbs the locations of v-pins based on SHAP values of the top features `manhattanVpin` and `diffVpinR` where  $R$  is  $X$  for odd split layers and  $Y$  for even split layers. This is done iteratively, one v-pin at a time. We first calculate the SHAP values  $S(i, j)$  for all essential v-pin pairs  $i$  and all features  $j$ . Then for each essential v-pin pair  $i$ , we take the maximum of the SHAP values over all features  $j$ , i.e.,  $S_{\max}(i) = \max_j S(i, j)$ .

For efficiency considerations, we only perturb “eligible” v-pins, which satisfy all of the following criteria:

- The v-pin belongs to an essential v-pin pair  $p = (v, v')$ , with  $v$  and  $v'$  in the same net. This is to avoid duplicated or invalid perturbations,

e.g. perturbing the same v-pin later when a different v-pin pair is being considered.

- $S_{\max}(p) = S(p, \text{manhattanVpin})$  or  $S_{\max}(p) = S(p, \text{diffVpinR})$ . This ensures the essential v-pin pair  $p$  is vulnerable, i.e., likely predictable with the top features.

- $S(p, \text{diffVpinR}) \geq S(p, \text{diffVpinR}')$ , where  $R' \in \{X, Y\}$  is the routing direction other than  $R$ . This condition ensures the effectiveness of perturbing  $v$  or  $v'$  in  $R$  direction.

- If there are more than one non-driving v-pin group in the net of  $v$  and  $v'$ , then  $v'$  in the driving v-pin group is not eligible for perturbation and only  $v$  may be perturbed. Otherwise, perturbing  $v'$  may affect multiple essential v-pin pairs at the same time.

The procedures of SHAP-guided via perturbation are summarized in Algorithm 1. We maintain a list  $\mathcal{L}$  of essential v-pin pairs  $p = (v, v')$  sorted in decreasing order of  $S_{\max}(p)$ . As shown in Algorithm 1 (lines 7–8), in each iteration, we select  $p$  from the top of the list, and apply trial perturbing moves (a series of “dry runs” that do not actually perturb) to each eligible v-pin in pair  $p$  within a predefined small radius  $r$  (detailed in lines 23–36) to find the most efficient move  $(v^*, \delta^*)$  which means to move v-pin  $v^*$  by amount  $\delta^*$ . Efficiency of a move is defined in terms of the decrease in the model output  $-\Delta f(\mathbf{x})$  and the extra WL  $\Delta WL$  (as an integer). Specifically, to quantify the efficiency of a move, we define its *gain* as

$$gain = \begin{cases} -\Delta f(\mathbf{x})/\Delta WL, & \text{if } \Delta f(\mathbf{x}) < 0 \text{ and } \Delta WL \geq 1 \\ 1 - \Delta f(\mathbf{x}), & \text{if } \Delta f(\mathbf{x}) < 0 \text{ and } \Delta WL \leq 0, \\ 0, & \text{if } \Delta f(\mathbf{x}) \geq 0 \text{ or not feasible} \end{cases} \quad (5.1)$$

which prioritizes moves that lead to a decrease in model output at no or low extra cost of WL.

The trial perturbing is necessary as it would be difficult to estimate the routing feasibility and extra WL without any trials due to complex layout congestion. After the trial perturbing, if there is no feasible move<sup>1</sup>, we remove pair  $p$  from  $\mathcal{L}$  (line 19), and proceed to the next v-pin pair in  $\mathcal{L}$ ; if there is any feasible move (lines 10–18), we take the actual move that has the highest gain, update the feature vector and the SHAP values (as in Figure 5.1), re-check the v-pin eligibility, and go to the next iteration.

### 5.5.1.3 Rip-up and Reroute Procedure

To apply a perturbing move to a v-pin  $v$ , we rip up and reroute the wires connecting  $v$  to the other components. To facilitate the rerouting procedure, we rip up  $v$  and all wires connecting to  $v$  that do not result in more than two connected components, while not touching any other v-pins, as shown in Figure 5.5(b). Then we move  $v$  to the new location and identify the unconnected parts (i.e. both endpoints of  $v$  and the other connected components of the net, referred to as “rerouting goals”) in the public and private portions, respectively, as in Figure 5.5(c). Finally, we use A\* search algorithm [26] to reconnect the unconnected parts of the net in the public portion using public layers, and then reconnect for the private portion using private layers, as shown in Figure 5.5(d). Specifically, the routing graph  $G(V, E)$  for A\* search is built in three dimensions. The vertices are valid routing grids in all metal layers, and the edges are in  $x$ ,  $y$  and  $z$  directions, corresponding to potential wires (in  $x$  and  $y$  directions) and vias (in  $z$  direction) where the routing resources permit. The edge set  $E$  changes dynamically as the routing resources are occupied or released in rip-up and reroute. This rip-up and reroute procedure ensures a feasible route (if possible) and optimizes the WL. Also, for via perturbation, the number of v-pins is not changed after rip-up and reroute, as we reconnect

---

<sup>1</sup>We say a move is feasible if it does not violate routing resources, i.e., does not cause any congestion overflow in global routing, or any short in detailed routing.

---

**Algorithm 1** Via Perturbation

---

```

1: procedure VIA-PERTURBATION( $\mathcal{L}, R, r, N$ )

2:   Input:  $\mathcal{L}$ : list of all essential v-pin pairs,  $R$ : perturbing direction, which is  $X$  for

odd split layer and  $Y$  for even split layer,  $r$ : radius for trial perturbing,  $N$ : maximum

number of iterations.

3:   for  $iter \leftarrow 1$  to  $N$  do

4:     if  $\mathcal{L}$  is empty then

5:       break

6:     end if

7:     for  $p$  in  $\mathcal{L}$  in descending order of  $S_{\max}(p)$  do

8:        $(v^*, \delta^*) \leftarrow \text{TRIAL-PERTURBING}(p, R, r)$

9:       if  $v^* \neq \text{null}$  then                                 $\triangleright$  take the actual move

10:         $\text{RIPUP-AND-REROUTE}(v^*, R, \delta^*)$

11:        Update the feature vector and SHAP values of  $p$

12:        Re-check the eligibility of both v-pins in  $p$

13:        if neither v-pin is eligible then

14:          Remove  $p$  from  $\mathcal{L}$

15:        end if

16:        Re-sort  $\mathcal{L}$  by  $S_{\max}$

17:        break                                 $\triangleright$  only move one v-pin at a time

18:      end if

19:      Remove  $p$  from  $\mathcal{L}$

20:    end for

21:  end for

22: end procedure

23: procedure TRIAL-PERTURBING( $p, R, r$ )

24:    $v^* \leftarrow \text{null}, \delta^* \leftarrow \text{null}$

25:    $\text{maxGain} \leftarrow 0$

26:   for eligible  $v$  in v-pin pair  $p$  do

27:     for  $\delta \leftarrow -r$  to  $r$  do

28:        $gain \leftarrow \text{RIPUP-AND-REROUTE}(v, R, \delta)$                                  $\triangleright$  move  $v$  in  $R$ -dir by  $\delta$

29:       if  $gain > \text{maxGain}$  then

30:          $v^* \leftarrow v, \delta^* \leftarrow \delta$

31:          $\text{maxGain} \leftarrow gain$

32:       end if

33:     end for

34:   end for

35:   return  $(v^*, \delta^*)$                                  $\triangleright$  Best v-pin to move & the amount

36: end procedure

37: procedure RIPUP-AND-REROUTE( $v, R, \delta$ )

38:   Rip up  $v$  and any wire connecting to  $v$  that does not result in more than two

connected components or touch other v-pins. (Figure 5.5(b))

39:   Move  $v$  in  $R$  direction by amount  $\delta$

40:   Identify unconnected parts for rerouting (Figure 5.5(c))

41:   Build/update the routing graph and reroute using A* search algorithm (Figure 5.5(d))

42:   Calculate  $gain$  according to (5.1)

43:   return  $gain$

44: end procedure

```

---

the net using public and private layers separately.

### 5.5.2 ObfusX with Wire Lifting

Wire lifting is the second routing-based technique in ObfusX. It moves wires from the public layers to private layers, and therefore creates more v-pins, which can make the attack more difficult.

Here, the same flow in Figure 5.1 is followed. However, instead of going through the v-pins connecting public and private layers as in via perturbation, we now consider the vias *one layer below* (i.e. the vias connecting the topmost public metal layer and the metal layer immediately below it). The goal of wire lifting is to make it most difficult for the attack model to identify the created v-pin pairs as connected, after lifting. To this end, ObfusX iteratively selects the via  $v$  on this layer which, when lifted above the split layer, would create an essential v-pin pair  $p$  whose maximal SHAP value  $S_{\max}(p)$ , is the lowest among all options of  $v$ .

After we select the v-pin  $v$  at each iteration, we perform the wire lifting by applying the same rip up and reroute procedure to  $v$  as in Section 5.5.1.3, except that,

- (a) we do not move the location of  $v$  after ripping up for saving WL, and

- (b) when rerouting with A\* search, we put a higher weight on wires in public layers, so that the use of public wires is discouraged and thus extra v-pins are created.

## 5.6 Experimental Results

We obtained the source code of the ML attack from [72], used the shap library for Python for SHAP analysis, and implemented all procedures of ObfusX in C++. Experiments were done on a Linux workstation with an Intel 16-core 3.60 GHz CPU and 64 GB memory.

Table 5.1: Results of via perturbation on five ISPD’11 benchmark designs

| Design<br>(#v-pins)    | No obfuscation<br>HR: 0.01%/0.1% | [72]          |               |       |       |           | ObfusX       |               |       |       |           |

|------------------------|----------------------------------|---------------|---------------|-------|-------|-----------|--------------|---------------|-------|-------|-----------|

|                        |                                  | HR            | $\Delta WL\%$ | PN%   | PV%   | $t_{CPU}$ | HR           | $\Delta WL\%$ | PN%   | PV%   | $t_{CPU}$ |

| <b>Split layer: M6</b> |                                  |               |               |       |       |           |              |               |       |       |           |

| sb1 (44486)            | 23.79 / 63.33                    | 2.19 / 11.58  | 3.03          | 99.83 | 99.58 | 3.86      | 0.52 / 6.12  | 0.55          | 66.57 | 36.01 | 3.28      |

| sb5 (60034)            | 29.47 / 63.96                    | 5.75 / 20.38  | 4.09          | 96.81 | 91.75 | 7.13      | 4.34 / 15.46 | 0.67          | 55.62 | 30.08 | 5.30      |

| sb10 (89846)           | 31.84 / 64.34                    | 10.24 / 28.31 | 4.52          | 92.45 | 79.77 | 7.75      | 9.37 / 23.93 | 0.71          | 46.49 | 23.96 | 8.05      |

| sb12 (80816)           | 33.01 / 75.58                    | 8.23 / 24.78  | 3.31          | 97.70 | 90.12 | 6.46      | 4.32 / 11.67 | 0.64          | 73.87 | 37.12 | 5.45      |

| sb18 (36026)           | 20.06 / 66.11                    | 4.27 / 16.55  | 2.64          | 98.91 | 94.35 | 2.88      | 2.16 / 8.68  | 0.67          | 63.02 | 34.27 | 2.06      |

| Average                | 27.63 / 66.66                    | 6.14 / 20.32  | 3.52          | 97.14 | 91.11 | 5.62      | 4.14 / 13.17 | 0.65          | 61.11 | 32.29 | 4.83      |

| <b>Split layer: M4</b> |                                  |               |               |       |       |           |              |               |       |       |           |

| sb1 (150510)           | 49.82 / 68.33                    | 6.46 / 25.37  | 9.50          | 99.79 | 93.91 | 9.00      | 1.70 / 24.08 | 2.14          | 65.23 | 35.26 | 18.90     |

| sb5 (179844)           | 38.78 / 60.40                    | 7.54 / 23.84  | 9.86          | 96.94 | 87.87 | 11.48     | 3.03 / 23.35 | 1.87          | 51.43 | 28.09 | 18.41     |

| sb10 (200896)          | 33.50 / 60.21                    | 13.16 / 37.36 | 8.53          | 91.38 | 73.21 | 15.05     | 9.81 / 36.54 | 1.31          | 38.81 | 19.55 | 17.19     |

| sb12 (173294)          | 47.07 / 71.52                    | 9.01 / 22.40  | 7.61          | 98.61 | 92.32 | 13.48     | 4.42 / 17.39 | 1.12          | 65.32 | 32.81 | 18.09     |

| sb18 (86658)           | 29.83 / 59.89                    | 5.15 / 17.89  | 6.43          | 99.37 | 95.29 | 4.26      | 1.87 / 10.95 | 1.53          | 57.00 | 30.80 | 7.18      |

| Average                | 39.80 / 64.07                    | 8.26 / 25.37  | 8.39          | 97.22 | 88.52 | 10.65     | 4.17 / 22.46 | 1.59          | 55.56 | 29.30 | 15.95     |

### 5.6.1 Via Perturbation with ObfusX

We first show in Table 5.1 the performance of via perturbation with ObfusX using five designs in ISPD’11 benchmark suite that are also used in [36, 43, 72]. We obtain routed overflow-free designs from [72], to which we apply the proposed SHAP-based via perturbation, with parameter  $r = 3 \times$  routing grid size. We compare the performance and the cost of obfuscation with the via perturbation technique proposed in [72]. This is based on the same ML attack model<sup>2</sup>.

We use the following metrics to evaluate the performance and the cost of an obfuscation<sup>3</sup>.

- Hit rate (HR) at X%: For a v-pin  $v$ , we first identify the top X% of other v-pins  $u$  which have the highest ML model output for essential v-pin pair  $(v, u)$ . These v-pins are predicted by ML to most likely

<sup>2</sup>Note that the popular network flow attack model [59] takes prohibitively long time to run on these designs and hence is not applicable here.

<sup>3</sup>Note that the functions of standard cells are not available in ISPD’11 benchmark. Therefore metrics related to circuit outputs (e.g. Hamming distance (HD), output error rate (OER)) are not applicable.

be the match for  $v$ . We call it a “hit” of  $v$  if its real matching v-pin is among the v-pins identified above. We then report the average percentage of hits of all v-pins  $v$  in the design.

For each design, we report two HR values with  $X = 0.01$  and  $0.1$ , respectively. (As a point of reference,  $X = 0.1$  results in up to 89 v-pins identified on split layer M6, or up to 200 v-pins on split layer M4 in these designs. The total number of v-pins is quite large as reported in the first column of the table.) *A lower HR means better obfuscation.*

- WL overhead ( $\Delta WL\%$ ): percentage of increase in WL after the obfuscation. *Lower is better.*

- Perturbed nets (PN%): number of perturbed nets divided by total number of nets that *contain any v-pin*. *Lower is better.*

- Perturbed v-pins (PV%): number of perturbed v-pins divided by the number of v-pins in the design. *Lower is better.*

- Total CPU time ( $t_{CPU}$ , in hours) for running ObfusX.

Several observations can be made from the results in Table 5.1. **First**, the HR of the ML model for 0.01% and 0.1% v-pin lists drops drastically after obfuscation; for ObfusX it drops from 28% and 67% to 4% and 13%, respectively, better than the HR reductions with in [72]. **Second**, the WL overhead of ObfusX is less than 1/5 of that with [72]. **Third**, with ObfusX, only around 30% of v-pins and 60% of nets (that contain v-pins) are finally perturbed, compared to nearly-all nets and v-pins when perturbed with [72].

To observe the tradeoff between performance and cost of obfuscation, we plot in Figure 5.6 the curves of HR and WL overhead with ObfusX and [72], respectively. Compared to [72], ObfusX achieves 87% and 97% lower HR in 0.1% and 0.01% v-pin lists, respectively, for the same WL overhead

Figure 5.6: Comparison of tradeoff in HR vs WL in *superblue1*.

Table 5.2: Results of wire lifting on six ISCAS'85 benchmark designs

| Design | #Nets | No obfuscation |      |      | [60]                         |                              |      |              | ObfusX                        |                              |      |              |                 |

|--------|-------|----------------|------|------|------------------------------|------------------------------|------|--------------|-------------------------------|------------------------------|------|--------------|-----------------|

|        |       | PNR%           | OER% | HD%  | PNR%                         | OER%                         | HD%  | $\Delta$ WL% | PNR%                          | OER%                         | HD%  | $\Delta$ WL% | $t_{CPU}$ (min) |

| c880   | 252   | 100.0          | 0.0  | 0.0  | 91.7                         | 99.9                         | 18.0 | 4.3          | 85.3                          | 100.0                        | 23.3 | 3.4          | 2.4             |

| c2670  | 607   | 95.8           | 99.9 | 7.0  | 87.1                         | 100.0                        | 14.0 | 4.4          | 77.8                          | 100.0                        | 23.5 | 3.2          | 7.0             |

| c3540  | 638   | 97.2           | 95.4 | 18.2 | 93.5                         | 100.0                        | 33.4 | 2.5          | 84.5                          | 100.0                        | 38.2 | 2.5          | 18.4            |

| c5315  | 997   | 98.7           | 98.7 | 4.3  | 95.0                         | 100.0                        | 18.1 | 1.7          | 88.9                          | 100.0                        | 23.2 | 1.7          | 13.6            |

| c6288  | 1921  | 99.8           | 36.8 | 3.0  | 98.6                         | 100.0                        | 42.1 | 1.8          | 95.3                          | 100.0                        | 45.3 | 1.8          | 14.1            |

| c7552  | 1041  | 99.6           | 69.5 | 1.6  | 95.3                         | 100.0                        | 20.3 | 2.2          | 87.5                          | 100.0                        | 27.2 | 2.2          | 12.7            |