## **Fabrication of Grafted UWBG Bipolar Devices**

By

Donghyeok Kim

A dissertation submitted in partial fulfillment of the requirements of the degree of

Doctor of Philosophy

(Electrical & Computer Engineering)

at the

UNIVERSITY OF WISCONSIN-MADISON

2023

Date of final oral examination: 5/4/2023

The dissertation is to be approved by the following members of the Final Oral Committee:

Zhenqiang Ma, Professor, Electrical and Computer Engineering (Advisor)

Gupta Chirag, Assistant Professor, Electrical and Computer Engineering

Jun Xiao, Assistant Professor, Material Science and Engineering

Shubhra Pasayat, Assistant Professor, Electrical and Computer Engineering

Vincent Gambin, Principal Scientist and Group Lead, Northrop Grumman

© Copyright by Donghyeok Kim 2023 All Rights Reserved

# To Madison,

the beautiful city that has been my home for 4 years.

### Acknowledgments

My Ph.D. journey would have been impossible if it had not been for my advisor, Professor Zhenqiang Ma. He started my Ph.D. study by accepting me as his graduate student at UW-Madison. Then, he funded my entire graduate program and helped me when I was struggling with my journey. Finally, he finished my journey by letting me graduate. Throughout the entire Ph.D. program, from the beginning to the end, I learned not only academic expertise from him but also the perseverance and courage to pursue my goals.

I would like to express my appreciation to Professor Shubhra Pasayat, Chirag Gupta, and Jun Xiao for serving as committee members for my preliminary examination and final examination. Their invaluable feedback and words of encouragement were instrumental in helping me successfully complete my Ph.D. program.

Additionally, Dr. Vincent Gambin from NGC collaborated with me on the DARPA project. His expertise in bipolar devices guided me toward the successful completion of the project. Dr. Gambin also participated in my final examination as a committee member. Without him, it would have been much more difficult for me to graduate from the Ph.D. program. Furthermore, I am grateful to Professor Shaoqin Gong for giving me the opportunity to work under her guidance and for allowing me to study on the biomedical research alongside Seunghwan.

I was never alone during the Ph.D. journey because my fellow graduate students and postdoctoral researchers taught and helped me a lot. I would like to extend my gratitude to Sang June, Jisoo, Seunghwan, Jie, Haris, Moheb, Hokyung and Jiarui. In particular, Jiarui helped me write Chapter 4 of my dissertation and contributed to the theoretical analysis, as well as conducting XRD, STEM, and EELS jobs in the study featured in Chapter 4. Hokyung did the partial

fabrication of the devices studied in Chapter 4. Haris and Moheb assissted me in fabricating the devices featured in Chapter 3. Jisoo also contributed to the fabrication and taught me how to fabricate the devices demonstrated in Chapter 2.

The Ph.D. journey could be endurable thanks to the support of my Korean friends—Choi Haeran, Sohn Byungmin, Seo Sangmin and Namkung Jin—and my family in Geoje, Korea during this journey.

I also appreciate Sam Choi (the CEO of Sam's Academy) for providing me with various opportunities and being a good friend of mine. It was a stroke of luck to meet him while studying the Chinese language in Beijing.

I want to sincerely thank the following organizations for their financial support of the thesis work: Defense Advanced Research Projects Agency (DARPA) (Grant # HR00112190107, N00014-18-1-2032, N660011914038, and HR0011-21-9-0109), Air Force Office of Scientific Research (AFOSR) (Grant # FA9550-19-1-0102 and FA9550-21-1-0081), Northrop Grumman Corporation (NGC) (Grant # HR0011-21-9-0109), and Wisconsin Alumni Research Foundation (WARF).

I would like to express my gratitude to Lee Byeonggeon, also known as CalmDownMan, for his engaging Youtube content. I listened to him so much while working or resting. Last but not least, I want to thank me for believing in me, doing all this hard work, never quitting, taking no days off, and overcoming all the struggles within my inner self.

#### **Abstract**

In this dissertation, the fabrication of Heterojunction Bipolar Transistors (HBTs) and PN junction diodes using Ultra Wide BandGap (UWBG) materials is explored, demonstrated and tested. Specifically, working HBTs composed of n-AlGaAs/p-GaAs/p-GaAsP/n-GaN and p-AlGaAs/n-GaAs/p-C(diamond) and a PN diode of p-Si/n-Ga<sub>2</sub>O<sub>3</sub> were fabricated and characterized, exhibiting excellent IV-characteristics. The fabrication of abrupt heterojunctions, such as GaAsP/GaN, GaAs/diamond, and Si/Ga<sub>2</sub>O<sub>3</sub> with high quality, was made possible through the semiconductor grafting technique. This method fundamentally removes he limitation on material selections for forming heterojunctions. The demonstrated GaN, diamond HBT and Ga<sub>2</sub>O<sub>3</sub> PN junction diode pave the way for high-power and high-speed devices applications in electric vehicles (EV), cloud computing, photovoltaic devices, and artificial intelligence (AI) systems, enabling more efficient and sustainable technological advancements.

In the first chapter, current trends in semiconductor devices and their applications are explored, emphasizing the need for a paradigm shift from silicon-based devices to compound semiconductor or UWBG-based applications. The semiconductor grafting technique is introduced as a novel approach to address one of the biggest challenges in utilizing compound material or UWBG semiconductors for device applications: forming heterojunctions with semiconductors of abrupt lattice mismatch. The chapter then suggestes how the semiconductor grafting technique can be applied to the fabrication of HBTs and PN junction diodes, discussing technical challenges and their solutions.

The second chapter investigates the fabrication of grafted p-AlGaAs/n-GaAs/p-C (diamond) HBT. A newly developed transfer-printing technique—double-flip transfer—is

introduced to address concerns related to the remaining AlAs layer after undercutting p-AlGaAs/n-GaAs nanomembranes. Additionally, surface treatment on diamond samples are discussed to lower the electron affinity and reduce valence band discontinuity between n-GaAs and p-C. Following successful fabrication, the diamond HBT features a DC gain of up to 2000. Further characterizations are needed to improve the yield of diamond HBT.

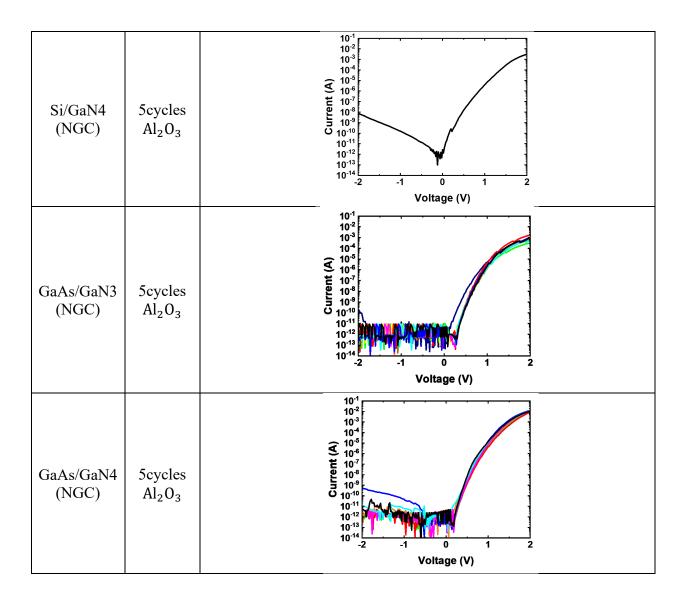

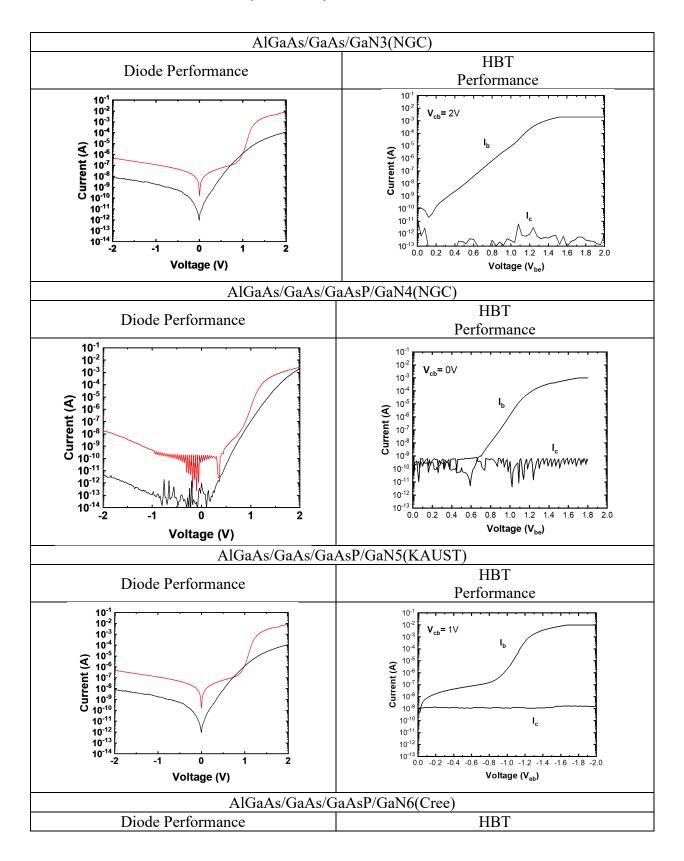

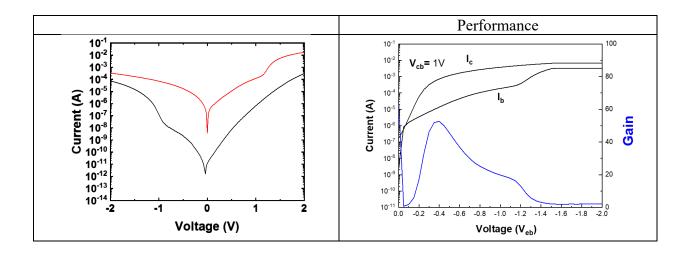

In the third chapter, an n-AlGaAs/p-GaAsP/n-GaN HBT is demonstrated, featuring a DC gain of around 80. By employing the semiconductor grafting technique, six different types of n-GaN substrates are seamlessly integrated with four types of nanomembranes, resulting in four different combinations of HBT. The only functioning HBT is composed of the n-AlGaAs/p-GaAs/p-GaAsP membrane and the GaN substrate with a high doping concentration on the surface. The IV characteristics are analyzed, examining the effects of surface treatment using ALD and a thin doping concentration layer on GaN substrate. These results will provide insights into developing high-yield GaN HBTs for high-speed and high-voltage applications.

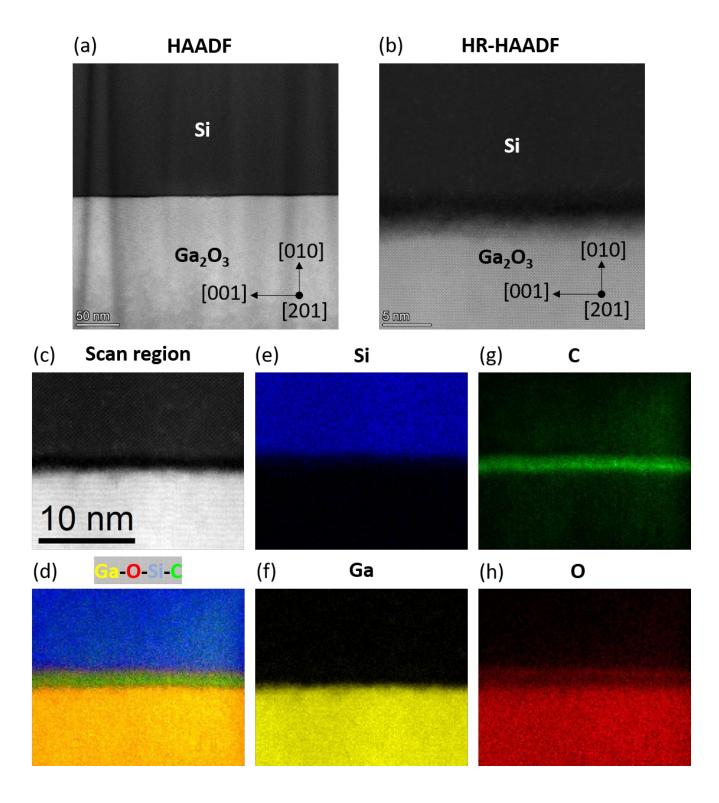

In the fourth chapter, PN junction diodes of n-type  $\beta-Ga_2O_3$  integrated with p-type silicon are explored, along with  $\beta-Ga_2O_3$  Schottky diodes created through the semiconductor grafting techniques. While most published PN junction diodes have utilized p-type sputtered oxide materials, such as NiOx and  $Cu_2O_3$ , for forming heterojunctions with  $\beta-Ga_2O_3$ , this study features the novelty of forming epitaxy-like heterojunctions by grafting p-type silicon nanomembrane onto n-type  $Ga_2O_3$ . The high interface quality in the grafted heterojunctions is measured by EELS and STEM.

Finally, the last chapter of the dissertation briefly summarizes possible future work, conclusions, and insights derived from these studies. The semiconductor grafting technique offers a revolutionary method for fabricating bipolar devices employing UWBG materials, which will be

applied in future device applications, such as artificial intelligence, cloud computing, electric vehicles, and photovoltaic devices. This groundbreaking approach will contribute to the development of more efficient and sustainable technologies in various fields.

## **Table of contents**

| Chapter 1: Introduction                               | 1                                                                             |  |  |  |  |  |  |  |  |

|-------------------------------------------------------|-------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Chapter 2: Fabrication and Characterization of AlGaAs | r 2: Fabrication and Characterization of AlGaAs/GaAs/C DHBT by Nanomembrane g |  |  |  |  |  |  |  |  |

| Grafting                                              | 21                                                                            |  |  |  |  |  |  |  |  |

| 2.1 Introduction                                      | 21                                                                            |  |  |  |  |  |  |  |  |

| 2.2 Materials                                         | 23                                                                            |  |  |  |  |  |  |  |  |

| 2.3 Methods of Fabrication                            | 26                                                                            |  |  |  |  |  |  |  |  |

| 2.4 Results                                           | 32                                                                            |  |  |  |  |  |  |  |  |

| 2.5 Conclusions                                       | 41                                                                            |  |  |  |  |  |  |  |  |

| 2.6 References                                        | 42                                                                            |  |  |  |  |  |  |  |  |

| Chapter 3: Fabrication and Characterization of AlG    | GaAs/GaAs/GaAsP/GaN DHBT by                                                   |  |  |  |  |  |  |  |  |

| Nanomembrane Grafting                                 | 45                                                                            |  |  |  |  |  |  |  |  |

| 3.1 Introduction                                      | 45                                                                            |  |  |  |  |  |  |  |  |

| 3.2 Materials and Characterization                    | 51                                                                            |  |  |  |  |  |  |  |  |

| 3.3 Methods of Fabrication                            | 53                                                                            |  |  |  |  |  |  |  |  |

| 3.4 Results                                           | 57                                                                            |  |  |  |  |  |  |  |  |

| 3.5 Conclusions                                       | 62                                                                            |  |  |  |  |  |  |  |  |

| 3.6 References                                        | 63                                                                            |  |  |  |  |  |  |  |  |

| Chapter 4: Fabrication and Characterization of p-Si/n- Ga <sub>2</sub> O <sub>3</sub> Heterojunction | on by |

|------------------------------------------------------------------------------------------------------|-------|

| Nanomembrane Grafting                                                                                | 68    |

| 4.1 Introduction                                                                                     | 68    |

| 4.2 Materials and Characterization                                                                   | 72    |

| 4.3 Methods of Fabrication                                                                           | 72    |

| 4.4 Results                                                                                          | 77    |

| 4.5 Conclusions                                                                                      | 82    |

| 4.6 References                                                                                       | 83    |

| Chapter 5: Conclusions and Future Directions                                                         | 89    |

## List of Figures

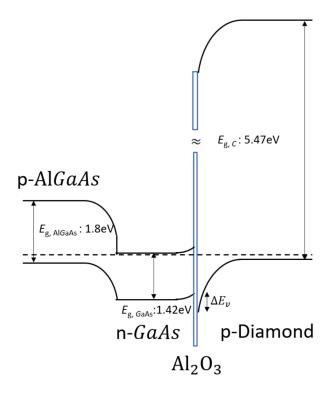

- Figure 2.1 The band diagram of p-AlGaAs/n-GaAs/p-C DHBT.

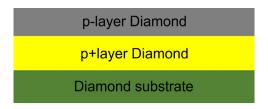

- **Figure 2.2** The schematic diagram of the diamond sample utilized as a collector of p-AlGaAs/n-GaAs/p-C DHBT.

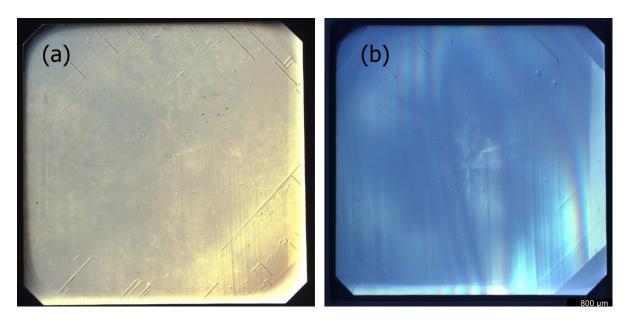

- *Figure 2.3* (a) The diamond sample before the CMP process. (b) The diamond sample after 120 minutes of CMP.

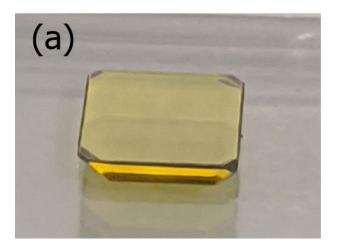

- **Figure 2.4** (a) The diamond sample after the CMP process. (b) The diamond sample taken in the ALD chamber.

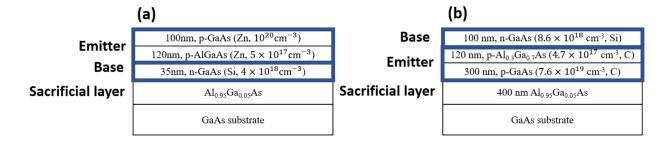

- **Figure 2.5** The schematic diagram of the samples of (a) conventional p-GaAs/p-AlGaAs/n-GaAs/GaAs substrate (b) inverted n-GaAs/p-AlGaAs/p-GaAs/GaAs substrate.

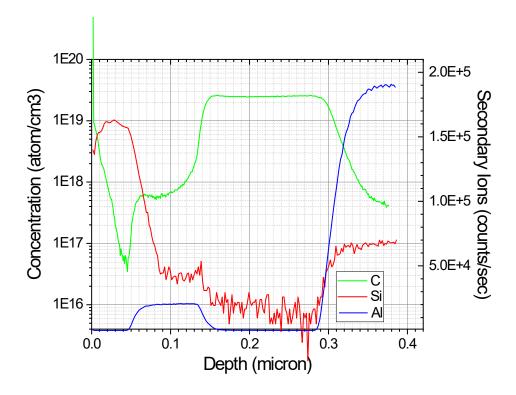

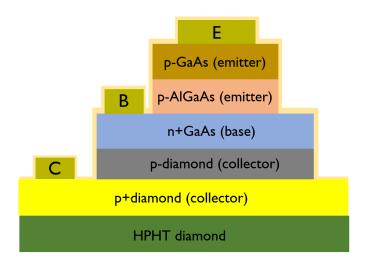

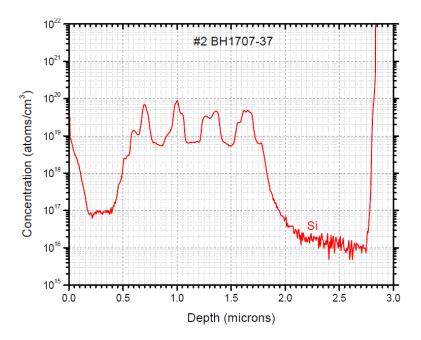

- Figure 2.6 The SIMS data of the sample of p-GaAs/p-AlGaAs/n-GaAs/GaAs substrate.

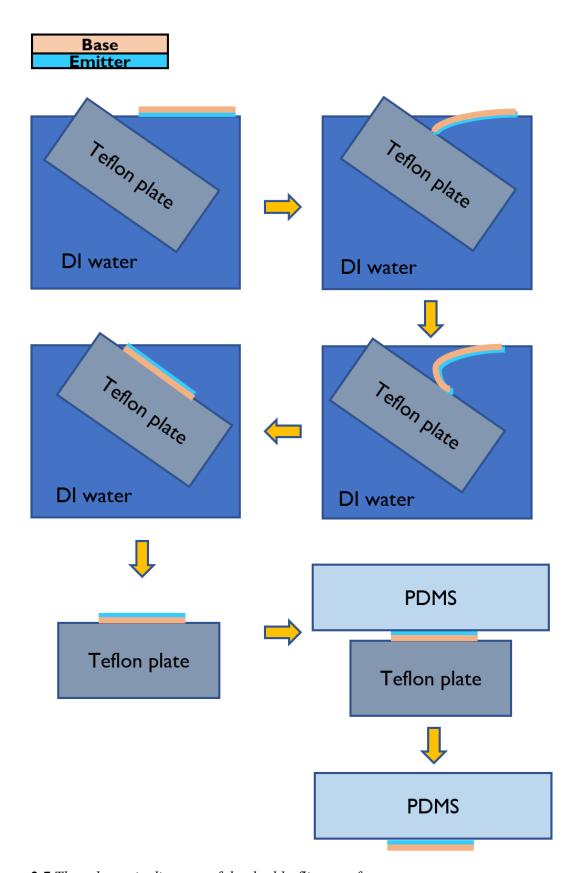

- Figure 2.7 The schematic diagram of the double-flip transfer.

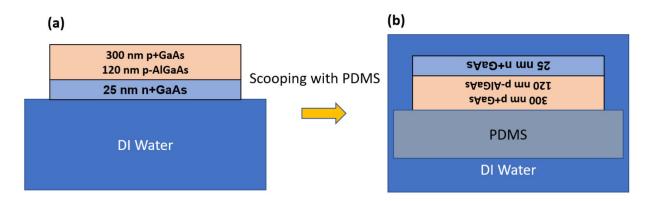

- **Figure 2.8** (a) After nanomembranes are undercut, the nanomembranes immediately float up on the surface of DI water. At this point, n+GaAs (base layer) does already face down to the DI water. (b) After scooping with PDMS described in **Figure 2.10**, the p+GaAs layer is directly contacting the PDMS, so as for n+GaAs to be directly contacting the diamond sample.

- Figure 2.9 The process flow of p+AlGaAs/n-GaAs/p-diamond DHBT.

- Figure 2.10 p-AlGaAs/n-GaAs/p-Diamond DHBT.

- **Figure 2.11** The AFM results of the top surface (a base layer) of nanomembranes before undercut.

- **Figure 2.12** The AFM results of the top surface (a base layer) of nanomembranes before the undercut.

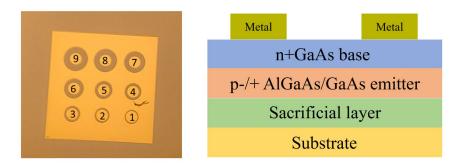

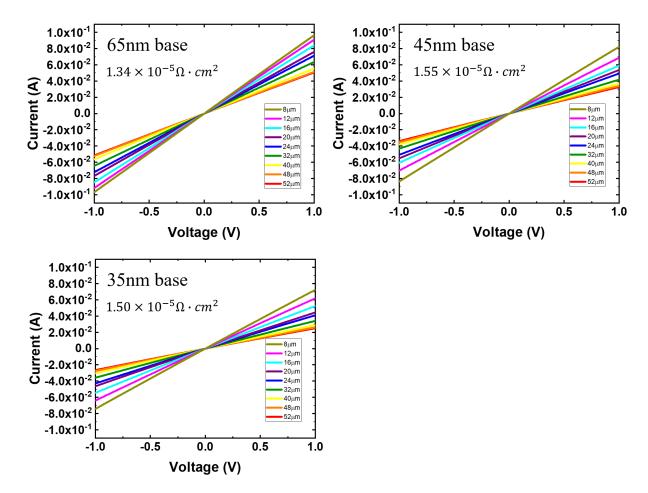

- **Figure 2.13** The CTLM results of the samples with the base thickness of (a) 65nm, (b) 45nm, and (c) 35nm.

- Figure 2.14 The schematic diagram of EB diode transferred on silicon substrates.

- Figure 2.15 The IV characteristics of EB diodes that have a base of 45nm and 35nm.

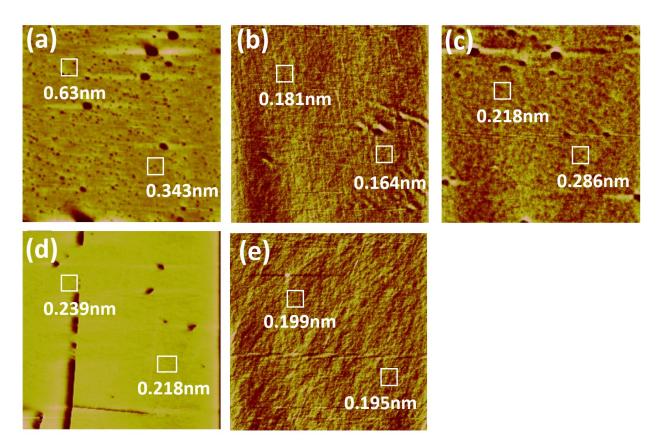

- Figure 2.16 The images of AFM on the diamond surface taken in the areas of  $100\mu m$  by  $100\mu m$ . The white squares of each figure represent the AFM scanning areas of  $10\mu m$  by  $10\mu m$  and the value below each square means the corresponding surface roughness. (a) The upper left side (b) The upper right side (c) The center, (d) The lower left, (e) The lower right side.

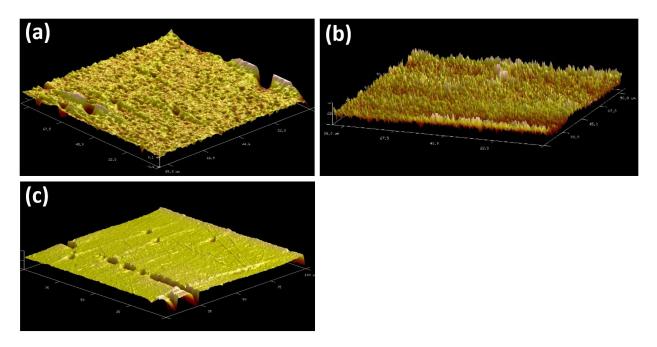

- *Figure 2.17* The 3D visualization of the images featured in *Figure 2.5*. (a) The upper right side (b), The lower left side (c), and The lower right side.

- **Figure 2.18** (a) The side view taken when the contact angle with a waterdrop on the diamond substrate in order to estimate the electron affinity of the diamond.

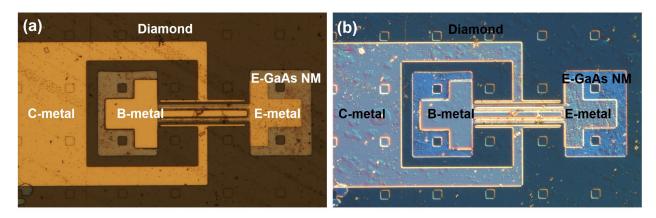

- Figure 2.19 (a) A microscopic image of individual HBT (b) A filtered image of the same HBT.

- Figure 2.20 (a) A microscopic image of individual HBT (b) A filtered image of the same HBT.

- **Figure 2.21** (a) Diode performance (Red EB diode and Black BC diode) (b) HBT performance (Offset  $V_{cb} = 0V$ )

- Figure 3.1. The SIMS data of GaN6 (Cree).

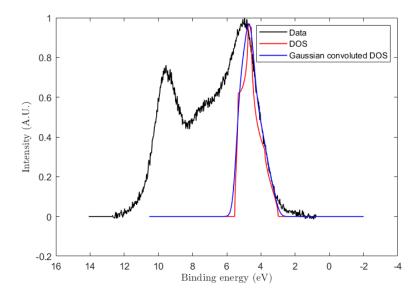

- **Figure 3.2.** The XPS data of GaN6 (Cree) after surface treatment. (Pass energy: 10eV, spot size: 400µm, dweel time: 40s, step: 0.02eV, C reference.) The XPS results determines that the upward band-bending is around 0.413eV when it is not treated. [15].

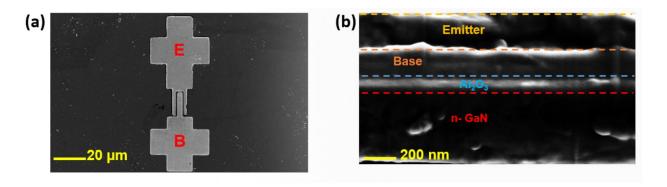

- Figure 3.3. (a) SEM Top view image of the device (b) the cross-sectional image.

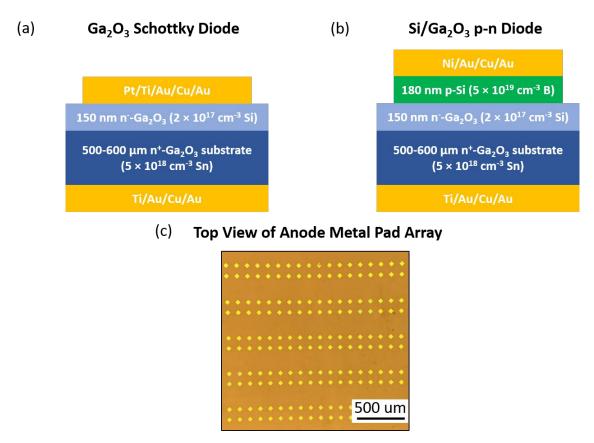

- **Figure 4.1** The schematic device layer structure of (a) the  $Ga_2O_3$  Schottky diode and (b) the  $Si/Ga_2O_3$  p-n diode. (c) The optical image of the top anode metal pad array.

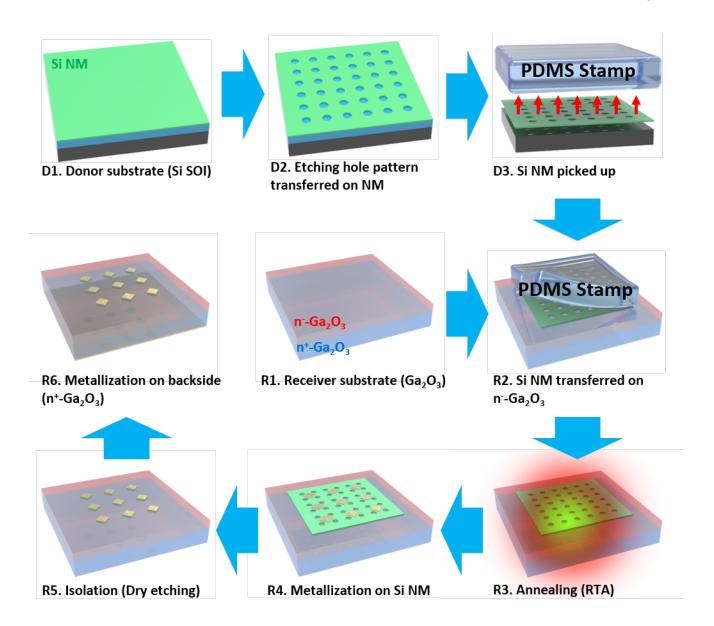

- **Figure 4.2.** The fabrication process flow of the Si/Ga<sub>2</sub>O<sub>3</sub> p-n diode. (D1)-(D3) The fabrication of the donor Si NM on SOI. (R1)-(R2) The transfer-printing of the Si NM onto the receiver  $Ga_2O_3$  substrate. (R3)-(R6) The following fabrication of the Si/Ga<sub>2</sub>O<sub>3</sub> p-n diode.

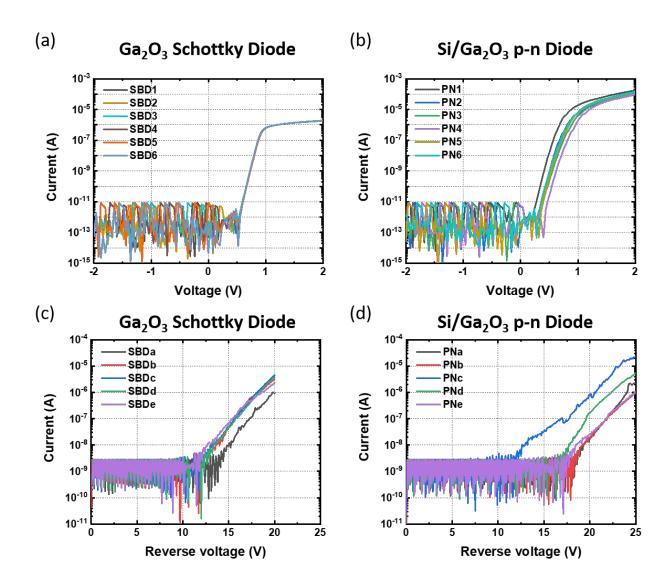

- **Figure 4.3.** The statistical I-V characteristics of (a) the  $Ga_2O_3$  Schottky diodes and (b) the  $Si/Ga_2O_3$  p-n diodes between  $\pm$  2 V. The statistical reverse bias characteristics of (c) the  $Ga_2O_3$  Schottky diodes and (d) the  $Si/Ga_2O_3$  p-n diodes.

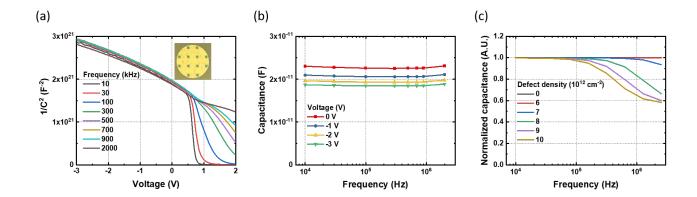

- **Figure 4.4** (a) The C-V characteristics of the Si/Ga<sub>2</sub>O<sub>3</sub> p-n diode under multiple frequencies. The inset shows the optical image of the device fabricated for the C-V measurement. (b) The capacitance-frequency plots of the Si/Ga<sub>2</sub>O<sub>3</sub> p-n diode under various biases. (c) The simulated capacitance-frequency plots of the Si/Ga<sub>2</sub>O<sub>3</sub> p-n diode under 0 bias with different interface defect densities.

- **Figure 4.5** STEM imaging and EELS elemental mapping: (a) The HAADF image and (b) the HR-HAADF image showing the cross-sectional view of the p-Si/n-Ga<sub>2</sub>O<sub>3</sub> device. (c) The scan region of the EELS mapping. (d) The fake color image showing the distribution of the corresponding element (Ga-O-Si-C) at the interface. (e)-(h) The EELS maps of Si, Ga, interfacial C, and O elements, respectively.

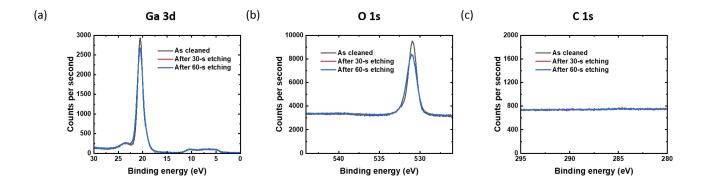

- **Figure 4.6** The (a) Ga 3d, (b) O 1s, and (c) C 1s XPS spectra of the  $Ga_2O_3$  substrate. A 30-s iongun etching was conducted between each measurement.

# Chapter 1

#### Introduction

In 2022, the entire semiconductor market was valued at around 580 billion USD [1, 2], while compound semiconductors, such as silicon carbide, gallium nitride, and gallium oxide, etc., were accounted for 40.5 billion USD, representing less than 10% of the entire semiconductor market. [3] The remaining 90% of the market size consisted of the silicon-based semiconductor industry. Despite the superiority of compound materials, which will be discussed in this chapter later, applications and developments of the compound materials have been relatively underdeveloped compared to those of silicon semiconductors [4-6]. For example, in 2016, the most advanced III-V semiconductor devices only contained a few thousand components per chip [7, 8]. Focusing on more specific functions of device applications, 87% of the high-power semiconductor devices market is based on mature silicon technology [9], while more than 90% of the photovoltaic cell devices in the markets utilize silicon as their most important material [10]. Two major reasons contributed to the huge success of silicon in the modern chip industries. The first one is the stability

of silicon dioxide, maintaining a great quality under high temperatures. Silicon dioxide is grown and used for Metal Oxide Semiconductor Field-Effect Transistors (MOSFETs). Second, the economic advantage has contributed to the dominant position of silicon in the markets. Silicon is the second most abundant element on Earth. Silicon makes up 27.7% of the mass of the Earth's crust [81]. The mature technology of fabricating integrated circuit chips on silicon wafers has contributed to silicon's near-monopoly. This technology has been developed since 1955, when the first MOSFETs were commercialized [12 13]. Historians and sociologists argue that the Digital Revolution, also known as the Third Industrial Revolution, has been made possible by the rapid and aggressive growth of the markets of silicon-based devices in the last century [14, 15]. This trend is partly illustrated by Dr. Gordon Moore's iconic observation called "Moore's Law," which states that "every two years, the number of electrical components such as transistors in a dense integrated circuit doubles [16]." Even though the empirical observation was formulated more than five decades ago, it is still valid today, reflecting the exponential nature of the miniaturization of silicon devices [17, 18]. With these advantages and the surge of demand in the market, the silicon chip market is projected to grow to 1034 billion USD by 2031 [19]. To meet the increasing demand for better-performing chips, big semiconductor manufacturers—Samsung Electronics, TSMC and Intel—have already declared the development of MOSFETs with a node size smaller than 2nm, which is only eleven times as larger as the diameter of a single silicon atom [19, 20]. Namely, the size of the devices approaches the fundamental limit of silicon-based devices.

Despite the enormous growth of silicon-based semiconductor markets, the innovation of silicon devices through miniaturization is becoming harder due to the physical bottom line drawn by quantum mechanics [21]. Even if the engineering barriers, such as high heat dissipation and high leakage currents in devices of a few Angstroms' dimensions, are solved, the Compton

wavelength of an electron defines the smallest dimension of possible transistors [21]. If Dr. Moore's prediction keeps valid, then the node length of transistors will converge to the quantum limit in 2036 [21]. However, it is obviously forecasted that there will be even more needs for larger storage, faster computing, and higher efficiency for cloud computing, Artificial-Intelligence (AI), Electric Vehicle (EV) and green energy/carbon-neutral trends to fight climate change beyond 2036 [22-27]. In addition, AI applications generate data of 80 exabytes each year, and this is expected to increase to 845 exabytes by 2025 [22]. Thus, demand for computing hardware such as CPU, GPU and memory chips will increase by 10 to 15 percent by 2025 [22]. This trend not only intensifies the need for a larger volume of storage and higher speed of processors but also requires efficient heat dissipation that cannot be achieved with the material properties of silicon [27]. In terms of high-power applications, power capability  $(V_B^2/R_{on})$  and maximum operating temperature are not desirable for the future demand of power electronics [12]. Furthermore, international regulations and movements to fight global warming that causes climate change are one of the most powerful driving factors calling for innovation in semiconductor devices [29-32]. To reduce pollutant emissions from internal combustion engines in cars, many governments, including the United States, the United Kingdom and Europe Union, encourage or force the automotive industries to prepare for a transition toward total electrification of vehicles [33-35]. Especially, the U.S. Department of Energy set a goal of the development of high-power converters that will be utilized in EV/HEV with power densities as high as 14.1kW/kg and efficiencies greater than 98% [36]. This cannot be achieved with traditional silicon power devices due to silicon's limit of physical properties [36]. The development of silicon-based solar cells is at its saturation while the efficiencies of silicon Photo-Voltaic devices (PV) are approaching the fundamental limit of the material [10]. It has been suggested that the intrinsic limit of silicon PV devices is around 29%,

while one of the latest crystalline silicon solar cells has an efficiency of 26.7% [10]. Despite this ultimate challenge for better PV devices with silicon, the demand for renewable energies has been increasing rapidly. Whereas only 12% of electricity was generated from renewable sources in 2000 in the EU, the number has increased to 37.5% today [48]. To keep up with these trends toward fast and efficient devices, a paradigm shift for developing semiconductor devices is inevitable rather than depending mostly on silicon materials.

**Table 1.1** The material characteristics of silicon and WBG materials. The Figure of Merits of the materials rather than silicon are normalized based on those of silicon [82].

|                                                            | Si   | GaAs | 4H-SiC | GaN    | Diamond | $\beta$ – $Ga_2O_3$ |

|------------------------------------------------------------|------|------|--------|--------|---------|---------------------|

| Bandgap (eV)                                               | 1.1  | 1.43 | 3.25   | 3.4    | 5.5     | 4.85                |

| Dielectric constant, $\epsilon$                            | 11.8 | 12.9 | 9.7    | 9      | 5.5     | 10                  |

| Breakdown field (MV/cm)                                    | 0.3  | 0.4  | 2.5    | 3.3    | 10      | 8                   |

| Electron mobility, $\mu$ (cm <sup>2</sup> /V·s)            | 1480 | 8400 | 1000   | 1250   | 2000    | 300                 |

| Electron Saturation velocity, $v_s$ (10 <sup>7</sup> cm/s) | 1    | 1.2  | 2      | 2.5    | 1       | 1.8-2               |

| Hole mobility (cm <sup>2</sup> /V·s)                       | 450  | 400  | 120    | 30-100 | 2000    | 1.3                 |

| Thermal conductivity (W/cm · K)                            | 1.5  | 0.5  | 4.9    | 2.3    | 20      | 0.1-0.3             |

| $Johnson = E_c^2 V_s^2 / 4\pi^2$                           | 1    | 1.8  | 278    | 1089   | 1110    | 2844                |

| Baliga= $\epsilon \mu E_c^3$                               | 1    | 14.7 | 317    | 846    | 24660   | 3214                |

| Keyes= $\lambda [(cV_s)/(4\pi\epsilon)]^{1/2}$             | 1    | 0.3  | 3.6    | 1.8    | 41.5    | 0.2                 |

One of the obvious choices to meet the future requirements for better devices and overcome the challenge posed on silicon-based industries is to fabricate devices by using Wide-BandGap (WBG) materials, such as Silicon Carbide (SiC), Gallium Nitride (GaN), Gallium Oxide  $(\beta - Ga_2O_3)$ , and diamond (C) that are superior compared to silicon in terms of material properties [37-40]. Their characteristics are summarized in Table 1.1. For power electronics, device performances are directly affected by material properties such as carrier mobilities, critical field strength, intrinsic concentration, and thermal conductivity [41-43]. High electron and hole

mobilities greatly reduce the switching recovery time, which leads to higher switching frequency. Faster-switching means that there can be fewer passive components on IC chips, which reduces the cost of manufacture [44]. Furthermore, a high breakdown field offers chances to operate with high voltage and current without compromising the stability of devices [45]. Low intrinsic concentration also plays a key role in increasing operation temperature along with high thermal conductivity [46]. The WBG materials in Table 1.1 are perfect candidates for high-power and high-speed applications owing to their superior properties [47]. Furthermore, it is required to use III-V materials in tandem structures for PV applications to exceed the fundamental efficiency of silicon-based photovoltaic devices [49]. Thus, the usage of WBG materials is also essential for PV applications.

However, using these materials presents its own set of challenges, such as the relatively less mature technology for fabricating WBG-based devices. For instance, the cost of growing wafer-scale substrates for these materials is significantly higher than that for silicon [50, 51]. Most of all, the biggest and most fundamental challenge is forming heterojunctions with other semiconductors. To design advanced semiconductor devices, it is critical to form heterojunctions between semiconductors with different band gaps. These heterojunctions are essential for creating solar cells, lasers, bipolar transistors, and field-effect transistors [52-54]. Namely, heterojunctions are basically building blocks to make devices, such as Bipolar Junction Transistors (BJTs), MOSFET and Schottky Junction Diodes (SJDs) [55]. Due to the heterogeneous nature of heterojunctions, a lattice mismatch between two materials is a major concern. The interface between two materials must maintain high quality with a minimum density of defects. Poor interface quality leads to defects that create trapped energy states on the interface, acting as recombination centers. This can cause a reduced on/off ratio, an Ideality Factor (IF) for diodes,

and a low gain for transistors [53]. One method for fabricating heterojunctions is the epitaxial growth of one semiconductor on another semiconductor with a minimal difference in lattice parameters [56]. This limit greatly reduces the potential for using these materials because even a slightly higher lattice mismatch can cause several defects, including stacking faults and dangling bonds [60-61]. The requirement for a lattice match restricts the number of possible combinations of semiconductors for compound semiconductors. For example, GaN only has been exclusively used with AlGaN and InGaN for high-power applications through conventional epitaxy. Likewise, GaAs has been usually used with AlGaAs and InGaAs for forming heterostructures.

Naturally, there have been a few technologies developed to form heterojunctions without worrying about a lattice-match. The first one is direct bonding of wafers [57-59]. Two smoothly polished wafers with an abrupt lattice mismatch are preprocessed through chemical and dry cleaning etc. Then, one of the wafers is placed on the top of the other, and they are bonded at room temperature. Then, the fused wafers are annealed, and the interface forms heterojunctions. It has been shown that the wafer-fused interface suffers vast amounts of defects, such as unfilled dangling bonds, fixed charges, trapped particles and weak bonding [62-64]. Because there is no buffer layer between the two wafers, atoms of each side freely diffuse to the other side when being annealed at high temperatures, which degrades the quality of the surface even more [65]. The performances of the diodes and Heterojunction Bipolar Transistors (HBTs) fabricated on bonded wafers are not as good as the devices fabricated by using the continuous epitaxy [66-68]. The second of the technologies is to transfer thin two-dimensional materials, such as graphene, hBN, MoS<sub>2</sub>, WSe<sub>2</sub>, and fluorographene on foreign semiconductor substrates to fabricate diodes, HBT, and MOSFET [69, 70]. There still exist engineering challenges to control the synthesis of the 2D materials and manipulate the interface conditions due to their 2D nature [71, 72]. Most of all, it is

still difficult and expensive to grow two-dimensional materials whose size is up to the wafer scales, which is necessitated to meet the demand from the chip markets [68]. The final and most notable one is the semiconductor grafting technique.

*Table 1.2* The diodes fabricated by the semiconductor grafting technique and their performances.

| Nanomembrane | Substrate       | I <sub>on</sub> /I <sub>off</sub> @1V | Ideality factor | Reference |

|--------------|-----------------|---------------------------------------|-----------------|-----------|

| p-Si         | n-GaAs          | $7.9 \times 10^9$                     | 1.07            | [55]      |

| p-GaAs       | n-GaN           | $1.1 \times 10^{6}$                   | 1.13            | [55]      |

| p-Ge         | n-Si            | $1.5 \times 10^{8}$                   | 1.02            | [55]      |

| p-Si         | n-GaN           | $4.1 \times 10^{8}$                   | 1.14            | [55]      |

| n-GaAs       | p-C             | $1.27 \times 10^9 (@3V)$              | 1.85            | [11]      |

| p-GaAsP      | n-GaN           | $1.84 \times 10^{8}$                  | 1.1             | This work |

| p-Si         | $n$ - $Ga_2O_3$ | $3.15 \times 10^{7}$                  | 1.13            | This work |

This technique has proven that more than 7 combinations of semiconductors with very high quality can be formed without worrying about an abrupt lattice mismatch, as organized in Table 1.2. The process flow of the grafting technique proceeds in the following order. First, deposit an ultra-thin oxide layer on any semiconductor substrate. Second, produce wafer-scale Nano-Membranes (NMs) whose thickness can vary from dozens of nanometers to several micrometers. Finally, transfer the sheets of NM picked up by PDMS onto the prepared semiconductor substrate. The ultra-thin layer between two semiconductors plays a crucial role by filling up dangling bonds on the interface [73-75]. The theoretical model has suggested that an ideality factor n of grafted diodes is calculated in the following equation when a density of states between a nanomembrane and a substrate is given as  $D_{SSN}$  [55].

$$n = 1 + \frac{1.81 \times 10^{-13}}{\epsilon_{ri}} W_i D_{ssn}$$

, where  $W_i$  is a thickness of a depletion region. It has been measured that a density of states on grafted interfaces can be low up to  $\sim 10^{11}/eV \cdot cm^2$  for silicon surfaces [55]. Provided  $W_i$  is 1nm, then the ideality factor, n, is expected to be around 1.01-1.05. One of the most important part of the equation is that it does not involve with materials being utilized for heterojunctions. Regardless of what kinds of materials are forming heterojunctions, a diode performance is determined by a density of defect. Not only have the devices integrating silicon/germanium heterojunctions shown one of the lowest ideality factors and highest  $I_{\rm on}/I_{\rm off}$  ratio, but also the diode combinations of Si/GaN, GaAs/GaN and Si/Ga<sub>2</sub>O<sub>3</sub> that had been impossible to fabricate through the conventional epitaxy have shown the record-breaking diode performances with a low ideality factor and a high on/off ratio. Their performances are well summarized in Table 1.2.

One of the most prominent applications of the semiconductor grafting technique is Heterojunction Bipolar Transistors (HBTs). By incorporating a heterojunction between an emitter and a base semiconductor in Bipolar Junction Transistors (BJTs), the HBTs acquire the benefits of higher gain and higher doping concentrations in base regions. HBTs generally feature several advantages over Field-Effect Transistors (FET) for low-noise, high-frequency, and high-power applications because HBTs have a higher conductance  $g_m$ , greater linearity, better threshold uniformity, a larger maximum oscillation frequency  $f_{max}$ , and higher breakdown voltages compared to FETs [53, 76, 77]. Exploiting these characteristics of HBTs, they are commonly used in automotive radar systems where high-power efficiency is necessary and wireless communication systems, including cellular devices [78-80]. However, single HBTs that have a single heterojunction in only an emitter-base junction also suffer several disadvantages. One disadvantage of single HBTs is high offset  $V_{ce}$  in the saturation region. If  $V_{ce}$  is low enough for single HBTs, the current from the base, Ib, cannot easily penetrate through an emitter-base

heterojunction because of its heterogeneous nature. Thus, electric current goes from a base to a collector instead, making the base-collector current negative, which eventually decreases the  $I_c$ current. Thus, a larger  $V_{ce}$  is necessary to turn on the transistors, which reduces the output signals. Furthermore, a material with a lower band gap than that of an emitter material is usually incorporated for a base to improve performance. However, a base with a lower band gap has a lower breakdown voltage on a base-collector junction due to the lower band gap. To improve the performance of a single HBT, a base and collector junction can also be made of materials that have different lattice structures. The HBTs that have heterojunctions on both emitter-base and basecollector junctions are called Double Heterojunction Bipolar Transistors (DHBT). By incorporating another heterojunction as a base-collector junction along with an emitter-base junction, DHBTs can have two major advantages over single HBTs: low offset voltage at a saturation region and a high breakdown voltage of a base-collection junction. For a DHBT, a basecollector junction also suppresses a collector current that compensates for the suppression effect of the EB heterojunction. Thus, the offset voltage of  $V_{ce}$  is reduced compared to that of single HBTs. Another advantage of DHBTs is the high breakdown voltage of base-collector junctions when wide-bandgap materials are used for collectors. Despite the advantages of DHBTs that play a very important role in high-power applications, they also come with their own engineering challenges—Discontinuity of conduction bands on the base-collector junctions which is also called "band-bending."

The band-bending effect prevents electrons in a base from being collected in a collector. In a single HBT, the current of electrons collected to a collector,  $I_{nC}$

$$I_{nC} = \frac{A_E q D_n n_{po}}{L_n} cosech\left(\frac{W}{L_n}\right) \left\{ \left[ \exp\left(\frac{q V_{BE}}{kT}\right) - 1 \right] - \coth\left(\frac{W}{L_n}\right) \left[\frac{n_p(W)}{n_{po}} - 1 \right] \right\}$$

If a base-collector junction is a homojunction,  $\frac{n_p(W)}{n_{po}} = \exp\left(\frac{qV_{BC}}{kT}\right)$ . On the other hand, consider the case where there exists a discontinuity in the conduction bands,  $\Delta E_c$  when a heterojunction is incorporated in the base-collection junction. Then, there is a stronger internal electric field generated in the junction because of the discontinuity. Thus, more electrons are diffused from the collector to the base, which increases the density of electrons at the base region,  $n_p(W)$ . As  $n_p(W)$ gets higher, the current of the electrons collected  $I_{nC}$  becomes even lower, which leads to degraded performance of HBTs, leading to a lower DC gain. To suppress the band-bending effect, substrate semiconductors must be treated in a special way. In the following chapters, novel ways to lower the discontinuity of conduction bands on the base-collector junction will be introduced with experimental measurements. The processes include integrating triple compound materials on junctions, treating substrates with ozone plasma, and conducting Atomic Layer Deposition (ALD). By solving the engineering challenge to suppress the band-bending effect, DHBTs utilizing AlGaAs, GaAs, and GaAsP as the emitters and the bases, GaN and diamond as the collector, respectively, have been demonstrated with a high DC gain of up to 80. Additionally, DHBTs that was deemed to be impossible, p-AlGaAs/n-GaAs/p-diamond, has been fabricated, showing the DC gain up to 2000.

$\beta$  –  $Ga_2O_3$  is also one of the most promising WBG materials. While there have been many pieces of research on growing n-type doped  $\beta$  –  $Ga_2O_3$ , p-type doping of the material with high quality has been essentially not possible. Due to this issue, the development of Ga2O3 as a power application has usually been focused on unipolar devices such as MOSFETs and SJDs despite the superior properties of the material. By using the grafting technique, bipolar p-n junction heterostructures have been fabricated with p-type silicon and n-type  $\beta$  –  $Ga_2O_3$  with record-high

diode performances, opening up the new possibility toward HBT integrating  $\beta$  –  $Ga_2O_3$  as a collector.

The rest of the contents of this dissertation is organized in the following order. First, HBTs with a diamond as a collector and III-V materials as a base and an emitter are demonstrated in Chapter 2. The characterization methods of diamond materials are demonstrated with the experimental results, focusing on how to reduce band-bending on the diamond substrates. Notably, the newly developed double-flip transfer is introduced as a way to graft nanomembranes on external semiconductor substrates. The IV characteristics of the AlGaAs/GaAs/diamond, including the high DC gain up to 2000, are discussed along with the potential of the research and the prospect for the future development of diamond HBTs. Second, diodes and HBTs utilizing GaN as a collector are introduced with the method of fabrication and characterization in Chapter 3. The band-bending effect of several GaN substrates is discussed in terms of device designs, followed by analyzing the IV characteristics of the fabricated diodes and HBTs, including Gummel plots. Then, the potential of the devices will be discussed along with research topics for the future. Third, the p-n bipolar heterojunction diodes of n-type  $\beta - Ga_2O_3$  and p-type silicon are presented with the method of fabrication in Chapter 4. The experimental results of material characterizations, including TEM and EELS, are shown and analyzed. Along with them, the IV characteristics, such as diode performances and C-V measurements, are measured and studied. The prospect of possible DHBT incorporating  $\beta$  –  $Ga_2O_3$  as a collector is also discussed.

#### References

- [1] Global Semiconductor Market Size from 1987 to 2023, Statista, Available:

<a href="https://www.statista.com/statistics/266973/global-semiconductor-sales-since-1988/">https://www.statista.com/statistics/266973/global-semiconductor-sales-since-1988/</a>

- [2] Global Semiconductor Sales Increase 3.3% in 2022 Despite Second-Half Slowdown,

Semiconductor Industry Association, Available:

<a href="https://www.semiconductors.org/global-semiconductor-sales-increase-3-2-in-2022-despite-second-half-slowdown/">https://www.semiconductors.org/global-semiconductor-sales-increase-3-2-in-2022-despite-second-half-slowdown/></a>

- [3] Compound Semiconductor Market Size by Type, Markets And Markets, Available: <a href="https://www.marketsandmarkets.com/Market-Reports/compound-semiconductor-market-178858112.html">https://www.marketsandmarkets.com/Market-Reports/compound-semiconductor-market-178858112.html</a>>

- [4] Liang, Di, and John E. Bowers. "Recent progress in heterogeneous III-V-on-silicon photonic integration." *Light: Advanced Manufacturing* 2.1 (2021): 59-83.

- [5] Zhang, Lei, et al. "Wafer-scale monolithic hybrid integration of Si-based IC and III–V epi-layers—A mass manufacturable approach for active matrix micro-LED micro-displays." *Journal of the Society for Information Display* 26.3 (2018): 137-145.

- [6] Tsao, J. Y., et al. "Ultrawide-bandgap semiconductors: research opportunities and challenges." *Advanced Electronic Materials* 4.1 (2018): 1600501.

- [7] Heck, Martijn JR. "Highly integrated optical phased arrays: photonic integrated circuits for optical beam shaping and beam steering." *Nanophotonics* 6.1 (2017): 93-107.

- [8] Hänsel, Andreas, and Martijn JR Heck. "Opportunities for photonic integrated circuits in optical gas sensors." *Journal of Physics: Photonics* 2.1 (2020): 012002.

- [9] Roccaforte, Fabrizio, et al. "Emerging trends in wide band gap semiconductors (SiC and GaN) technology for power devices." *Microelectronic Engineering* 187 (2018): 66-77.

- [10] Andreani, Lucio Claudio, et al. "Silicon solar cells: toward the efficiency limits."

Advances in Physics: X 4.1 (2019): 1548305.

- [11] Kim, Jisoo. "Study on Heterostructure Semiconductor Devices Using Grafting Technique," University of Wisconsin-Madison, Ph.D. dissertation.

- [12] Chabal, Yves J., ed. "Fundamental aspects of silicon oxidation." (2001).

- [13] Van Zant, Peter. Microchip fabrication. McGraw-Hill Education, 2014.

- [14] Dreyer, Keith J., et al. A guide to the digital revolution. New York: Springer, 2006.

- [15] Knell, Mark. "The digital revolution and digitalized network society." *Review of Evolutionary Political Economy* 2.1 (2021): 9-25.

- [16] G. E. Moore, "Cramming more components onto integrated circuits, Reprinted from Electronics, volume 38, number 8, April 19, 1965, pp.114 ff.," in *IEEE Solid-State Circuits Society Newsletter*, vol. 11, no. 3, pp. 33-35, Sept. 2006, doi: 10.1109/N-SSC.2006.4785860.

- [17] TSMC 3nm Technology Roadmap,

<a href="mailto:Available:https://www.tsmc.com/english/dedicatedFoundry/technology/logic/l\_3nm">https://www.tsmc.com/english/dedicatedFoundry/technology/logic/l\_3nm</a>

- [18] Samsung Technology Roadmap, <Available:</p>

https://semiconductor.samsung.com/us/foundry/process-technology/advanced-node/>

- [19] Semiconductor Market Expected to Reach \$1033.5 Billion by 2031—Allied Market Research, <Available: https://www.alliedmarketresearch.com/press-release/semiconductor-market.html>

- [20] TSMC R&D Plans, <Available: https://www.tsmc.com/english/dedicatedFoundry/technology/future\_rd>

- [21] Powell, James R. "The quantum limit to Moore's law." *Proceedings of the IEEE* 96.8 (2008): 1247-1248.

- [22] Batra, Gaurav, et al. "Artificial-intelligence hardware: New opportunities for semiconductor companies." *McKinsey and Company, January* 2 (2019).

- [23] Husain, Iqbal, et al. "Electric drive technology trends, challenges, and opportunities for future electric vehicles." *Proceedings of the IEEE* 109.6 (2021): 1039-1059.

- [24] Kumar, Jitendra, and Ashutosh Kumar Singh. "Cloud resource demand prediction using differential evolution based learning." 2019 7th International Conference on Smart Computing & Communications (ICSCC). IEEE, 2019.

- [25] Islam, Rejaul, S. M. Rafin, and Osama A. Mohammed. "Comprehensive Review of Power Electronic Converters in Electric Vehicle Applications." *Forecasting* 5.1 (2023): 22-80.

- [26] Hertwich, E., et al. "Green Energy Choices: The benefits, risks, and trade-offs of low-carbon technologies for electricity production." (2016).

- [27] Shastri, Bhavin J., et al. "Photonics for artificial intelligence and neuromorphic computing." *Nature Photonics* 15.2 (2021): 102-114.

- [28] Roccaforte, Fabrizio, et al. "Challenges for energy efficient wide band gap semiconductor power devices." *physica status solidi (a)* 211.9 (2014): 2063-2071.

- [29] Marszewski, Michal, et al. "Semiconductor-based photocatalytic CO 2 conversion." *Materials Horizons* 2.3 (2015): 261-278.

- [30] Nowotny, Janusz. "Titanium dioxide-based semiconductors for solar-driven environmentally friendly applications: impact of point defects on performance." *Energy & Environmental Science* 1.5 (2008): 565-572.

- [31] Lee, Ki-Hoon, and Ji-Whan Kim. "Integrating suppliers into green product innovation development: an empirical case study in the semiconductor industry." *Business Strategy* and the Environment 20.8 (2011): 527-538.

- [32] Tsai, Wen-Tien, Horng-Ping Chen, and Wu-Yuan Hsien. "A review of uses, environmental hazards and recovery/recycle technologies of perfluorocarbons (PFCs) emissions from the semiconductor manufacturing processes." *Journal of Loss Prevention in the Process Industries* 15.2 (2002): 65-75.

- [33] https://www.reuters.com/business/autos-transportation/eu-lawmakers-approve-effective-2035-ban-new-fossil-fuel-cars-2023-02-14/

- [34] https://www.energy-uk.org.uk/index.php/media-and-campaigns/energy-uk-blogs/8368-the-necessary-potential-of-a-strong-and-ambitious-uk-zev-mandate.html

- [35] https://www.gao.gov/products/gao-23-105635

- [36] Matallana, A., et al. "Power module electronics in HEV/EV applications: New trends in wide-bandgap semiconductor technologies and design aspects." *Renewable and Sustainable Energy Reviews* 113 (2019): 109264.

- [37] Del Alamo, Jesús A. "Nanometre-scale electronics with III–V compound semiconductors." *Nature* 479.7373 (2011): 317-323.

- [38] Liao, Meiyong. "Progress in semiconductor diamond photodetectors and MEMS sensors." *Functional Diamond* 1.1 (2022): 29-46.

- [39] Casady, J. B., and R. Wayne Johnson. "Status of silicon carbide (SiC) as a wide-bandgap semiconductor for high-temperature applications: A review." *Solid-State Electronics* 39.10 (1996): 1409-1422.

- [40] Moutanabbir, Oussama, and Ulrich Goesele. "Heterogeneous integration of compound semiconductors." *Annual Review of Materials Research* 40 (2010): 469-500.

- [41] Wort, Chris JH, and Richard S. Balmer. "Diamond as an electronic material." *Materials today* 11.1-2 (2008): 22-28.

- [42] Flack, Tyler J., Bejoy N. Pushpakaran, and Stephen B. Bayne. "GaN technology for power electronic applications: a review." *Journal of Electronic Materials* 45 (2016): 2673-2682.

- [43] Buttay, Cyril, et al. "State of the art of high temperature power electronics." *Materials Science and Engineering: B* 176.4 (2011): 283-288.

- [44] Armstrong, Kristina O., Sujit Das, and Joe Cresko. "Wide bandgap semiconductor opportunities in power electronics." 2016 IEEE 4th Workshop on Wide Bandgap Power Devices and Applications (WiPDA). IEEE, 2016.

- [45] Armstrong, Kristina O., Sujit Das, and Joe Cresko. "Wide bandgap semiconductor opportunities in power electronics." 2016 IEEE 4th Workshop on Wide Bandgap Power Devices and Applications (WiPDA). IEEE, 2016.

- [46] Wang, Fei Fred, and Zheyu Zhang. "Overview of silicon carbide technology: Device, converter, system, and application." *CPSS Transactions on Power Electronics and Applications* 1.1 (2016): 13-32.

- [47] Ballestín-Fuertes, Javier, et al. "Role of wide bandgap materials in power electronics for smart grids applications." *Electronics* 10.6 (2021): 677.

- [48] EU reaches deal on higher renewable energy share by 2030, <Available:

https://www.reuters.com/business/sustainable-business/eu-reaches-deal-more-ambitiousrenewable-energy-targets-2030-2023-03-30/>

- [49] Cariou, Romain, et al. "III–V-on-silicon solar cells reaching 33% photoconversion efficiency in two-terminal configuration." *Nature Energy* 3.4 (2018): 326-333.

- [50] Bauhuis, G. J., et al. "Wafer reuse for repeated growth of III–V solar cells." *Progress in Photovoltaics: Research and Applications* 18.3 (2010): 155-159.

- [51] Dimroth, Frank, et al. "Comparison of direct growth and wafer bonding for the fabrication of GaInP/GaAs dual-junction solar cells on silicon." *IEEE Journal of Photovoltaics* 4.2 (2014): 620-625.

- [52] Haschke, Jan, et al. "Silicon heterojunction solar cells: Recent technological development and practical aspects-from lab to industry." *Solar Energy Materials and Solar Cells* 187 (2018): 140-153.

- [53] Sze, Simon M., Yiming Li, and Kwok K. Ng. Physics of semiconductor devices. John wiley & sons, 2021.

- [54] De Wolf, Stefaan, et al. "High-efficiency silicon heterojunction solar cells: A review." green 2.1 (2012): 7-24.

- [55] Liu, Dong, et al. "Lattice-mismatched semiconductor heterostructures." *arXiv preprint arXiv:1812.10225* (2018).

- [56] Alferov, Zh I. "The history and future of semiconductor heterostructures." Semiconductors 32 (1998): 1-14.

- [57] Black, A., et al. "Wafer fusion: materials issues and device results." *IEEE Journal of selected topics in quantum electronics* 3.3 (1997): 943-951.

- [58] Chung, Taek Ryong, et al. "Wafer direct bonding of compound semiconductors and silicon at room temperature by the surface activated bonding method." *Applied surface science* 117 (1997): 808-812.

- [59] Plößl, Andreas, and Gertrud Kräuter. "Wafer direct bonding: tailoring adhesion between brittle materials." *Materials Science and Engineering: R: Reports* 25.1-2 (1999): 1-88.

- [60] Wu, X. H., et al. "Dislocation generation in GaN heteroepitaxy." *Journal of crystal growth* 189 (1998): 231-243.

- [61] Chen, Y., and J. Washburn. "Structural transition in large-lattice-mismatch heteroepitaxy." *Physical review letters* 77.19 (1996): 4046.

- [62] Moriceau, Hubert, et al. "Overview of recent direct wafer bonding advances and applications." *Advances in Natural Sciences: Nanoscience and Nanotechnology* 1.4 (2010): 043004.

- [63] Ventosa, C., et al. "Hydrophilic low-temperature direct wafer bonding." *Journal of Applied Physics* 104.12 (2008): 123524.

- [64] Ventosa, C., et al. "Prebonding thermal treatment in direct si–si hydrophilic wafer bonding." *Journal of The Electrochemical Society* 156.11 (2009): H818.

- [65] Horng, Ray-Hua, et al. "AlGaInP/mirror/Si light-emitting diodes with vertical electrodes by wafer bonding." *Applied physics letters* 82.23 (2003): 4011-4013.

- [66] Lian, Chuanxin, et al. "DC characteristics of AlGaAs/GaAs/GaN HBTs formed by direct wafer fusion." *IEEE electron device letters* 28.1 (2006): 8-10.

- [67] Estrada, Sarah, et al. "Wafer-fused n-AlGaAs/p-GaAs/n-GaN heterojunction bipolar transistor with uid-GaAs base-collector setback." *MRS Online Proceedings Library* (OPL) 798 (2003).

- [68] Zhang, Leining, Jichen Dong, and Feng Ding. "Strategies, status, and challenges in wafer scale single crystalline two-dimensional materials synthesis." *Chemical reviews* 121.11 (2021): 6321-6372.

- [69] Geim, Andre K., and Irina V. Grigorieva. "Van der Waals heterostructures." *Nature* 499.7459 (2013): 419-425.

- [70] Gong, Yongji, et al. "Vertical and in-plane heterostructures from WS 2/MoS 2 monolayers." *Nature materials* 13.12 (2014): 1135-1142.

- [71] Dong, Renhao, Tao Zhang, and Xinliang Feng. "Interface-assisted synthesis of 2D materials: trend and challenges." Chemical reviews 118.13 (2018): 6189-6235.

- [72] Bhimanapati, Ganesh R., et al. "Recent advances in two-dimensional materials beyond graphene." *ACS nano* 9.12 (2015): 11509-11539.

- [73] Werner, F., A. Cosceev, and J. Schmidt. "Interface recombination parameters of atomic-layer-deposited Al2O3 on crystalline silicon." *Journal of Applied Physics* 111.7 (2012): 073710.

- [74] Dingemans, G., et al. "Influence of the oxidant on the chemical and field-effect passivation of Si by ALD Al2O3." *Electrochemical and Solid-State Letters* 14.1 (2010): H1.

- [75] Zhang, Liangliang, et al. "EOT Scaling of TiO2/Al2O3 on Germanium pMOSFETs and Impact of Gate Metal Selection." *IEEE electron device letters* 34.6 (2013): 732-734.

- [76] Zhang, Yumin, Cheng Cai, and P. Paul Ruden. "AlGaN/GaN heterojunction bipolar transistor structures-design considerations." *Journal of Applied Physics* 88.2 (2000): 1067-1072.

- [77] Pavlidis, Dimitris. "HBT vs. PHEMT vs. MESFET: What's best and why." *International Conference on Compound Semiconductor Manufacturing Technology*. 1999.

- [78] Ashburn, Peter. SiGe heterojunction bipolar transistors. John Wiley & Sons, 2004.

- [79] Hassan, Muhammad, et al. "A wideband CMOS/GaAs HBT envelope tracking power amplifier for 4G LTE mobile terminal applications." *IEEE Transactions on Microwave Theory and Techniques* 60.5 (2012): 1321-1330.

- [80] Giammello, Vittorio, Egidio Ragonese, and Giuseppe Palmisano. "A transformer-coupling current-reuse SiGe HBT power amplifier for 77-GHz automotive radar." *IEEE transactions on microwave theory and techniques* 60.6 (2012): 1676-1683.

- [81] Periodic Table, Royal Society of Chemistry, <Available: https://www.rsc.org/periodic-table/element/14/silicon>

- [82] Pearton, S. J., et al. "A review of Ga2O3 materials, processing, and devices." *Applied Physics Reviews* 5.1 (2018): 011301.

# Chapter 2

# Fabrication and Characterization of AlGaAs/GaAs/C DHBT by Nanomembrane Grafting

#### 2.1. Introduction

Diamond(C) is an Ultra-Wide Band Gap (UWBG) material that has superior electrical and thermal properties, which make it suitable for applications of high-power, high-frequency, high-temperature, and high-voltages [1-3]. Its breakdown voltage is three times as high as that of gallium nitride, while the thermal conductivities are thirteen times that of silicon [4]. Its carrier mobility surpasses those of other III-V compound materials except for the electron mobility of GaAs [5]. Owing to these characteristics, the figure of merits of diamonds are highest among those of the semiconductor materials that have been used for high-power applications, as shown in Table 1.1. Schottky diodes and FETs have been demonstrated with high breakdown voltages at high temperatures [6-9]. However, electronic devices with outstanding performance that utilize diamonds are mostly unipolar devices, due to the challenges associated with achieving n-type doping in intrinsic diamonds. For n-type donors such as nitrogen and phosphorous, the ionization

energy levels are too high for effective activations [10-11]. Although bipolar PIN junction diodes with limited performance have been developed and published [12-13], high DC gain bipolar transistors, including BJTs and HBTs, have not yet been achieved. To circumvent the difficulty of efficiently doping diamonds with n-type dopants, a novel approach—the semiconductor grafting technique—has been employed to fabricate HBTs, using p-type doped diamonds as collectors [3]. Since the technique for growing n-type doped gallium arsenide with high electron mobility is welldeveloped, n-type GaAs nanomembranes can be grafted onto p-type diamonds using a few cycles of ultra-thin oxide layers between them [14]. By forming an n-GaAs/p-diamond heterojunction with ultra-thin oxides in between, PN junction diodes are achieved with high quality on the interface [3]. In the previous research, p-AlGaAs/n-GaAs/p-diamond HBTs were designed and fabricated by using the grafted p-AlGaAs/n-GaAs nanomembranes on p-diamond substrates. However, transistor performances could not be obtained despite the successful demonstration of emitter-base and base-collector diodes in the devices. One reason for the isolation of the emitterbase and base-collector junctions is the presence of residual AlAs layers that were not fully wetetched after the release of the p-AlGaAs/n-GaAs nanomembrane layers. To overcome this challenge, the new grafting technique called "double flip transfer" has been developed and utilized to fabricate p-AlGaAs/n-GaAs/p-diamond HBTs. The other reason for the previous batch not having a DC HBT was high electron affinity (~0.3eV), which increased the discontinuity in the valence band, as shown in Figure 2.1. For the diamond used in this work, the surface electron affinity was adjusted to 80-100 meV through chemical cleaning and atomic layer deposition (ALD), significantly reducing the valence band energy barrier and facilitating hole collection in the reverse-biased collector. The newly fabricated HBTs utilizing diamond as a collector are presented, showing the high DC gain of  $\sim 2000$ .

Figure 2.1 The band diagram of p-AlGaAs/n-GaAs/p-C DHBT.

#### 2.2 Materials

#### Diamond

The p- layer and p+ layer of diamond were grown on a single crystal diamond substrate, as shown in Figure 2.2. The resistivity of p+ layer was measured to be  $8.9 \times 10^{-2} \Omega \cdot m$ . After growing the p- layer, the surface had visually obvious defects of pits and scratches, as featured in Figure 2.3(a). Then, the surface of the diamond sample was treated by using Chemical Mechanical Polishing (CMP) for 120 minutes in order to make the surface smooth enough for transfer printing. The image after the CMP process is featured in Figure 2.3(b). Even though some scratches became less obvious, there were still mechanical defects left on the surface.

**Figure 2.2** The schematic diagram of the diamond sample utilized as a collector of p-AlGaAs/n-GaAs/p-C DHBT.

Figure 2.3 (a) The diamond sample before the CMP process. (b) The diamond sample after 120 minutes of CMP.

**Figure 2.4** (a) The diamond sample after the CMP process. (b) The diamond sample taken in the ALD chamber.

### p-GaAs/p-AlGaAs/n-GaAs naonomembrane

From the previous p-AlGaAs/n-GaAs/p-diamond DHBT, the conventional structure of GaAs/AlGaAs/GaAs nanomembranes (Figure 2.5(a)) was used. The additional measurement suggested that an additional AlAs layer exists between nanomembranes and the diamond surface [15]. The residual AlAs layer hampers electrons diffused from an emitter to be collected toward a collector because the hole mobility in p-GaAs is relatively low. To avoid this issue in the fabrication of the work, the nanomembrane samples of the inverted structure p-GaAs/p-AlGaAs/n-GaAs were grown through Metal Organic Chemical Vapor Deposition(MOCVD), as shown in Figure 2.8(b). In this structure, the base layer is on the top layer of the sample, and it directly contacts the p-diamond surface. In this way, there is no concern about extra AlAs layers between nanomembranes and the diamond surface. Furthermore, the thickness of a base region can be adjusted by dry etching before proceeding with releasing nanomembranes. The SIMS data is presented in Figure 2.6.

**Figure 2.5** The schematic diagram of the samples of (a) conventional p-GaAs/p-AlGaAs/n-GaAs/GaAs substrate (b) inverted n-GaAs/p-AlGaAs/p-GaAs/GaAs substrate.

Figure 2.6 The SIMS data of the sample of p-GaAs/p-AlGaAs/n-GaAs/GaAs substrate.

### 2.3 Methods of Fabrication

### a. Preparation of nanomembranes

The nanomembrane wafers were diced into 4cm by 4cm. Because the base layers were exposed to the air, unlike the conventional structure of nanomembranes (Figure 2.8(a)), the thickness of a base layer can be determined by etching the surface of the samples. For this batch, 20nm of the base layer was etched to make the base layer 25nm thick through an ICP etcher with a condition of RIE (60W), ICP (500W), BCl<sub>3</sub> (10sccm), Ar (5sccm), and 15mTorr for 14 seconds. Then, they were coated with S1813, followed by hole patterning through an MJB3 mask aligner with the condition of 5.5 mW/cm<sup>2</sup> for 30 seconds. The samples were developed in MF321 solution for one minute and, successively, etched by an ICP etcher for 210 seconds with the same

condition as the first etch. The sample with holes was placed into a 1:20 HF solution and left there for two hours.

### b. Double-flip transfer

After the wet-etch process was completed, the samples were taken out of the HF solutions and directly put into DI water in a Teflon dish. Because the nanomembranes had been fully undercut, they would immediately float up on the surface of DI water. As the lattice parameter of GaAs is smaller than that of AlGaAs, the emitter side of the nanomembranes experiences compressive strains due to its thick GaAs layers (300nm) [16]. Thus, the emitter side of the floating nanomembrane is always facing down, as drawn in Figure 2.6. Then, a Teflon plate was brought close to the nanomembrane on DI water. Because of the hydrophobic nature of Teflon plates, the water surface makes a curve on the boundary, as described in Figure 2.6. Thus the nanomembrane rolled inside as the Teflon plate approached, and the base side was attached to the Teflon plate. This is the first flip of the double-flip transfer. Finally, the plate with the nanomembrane onto was taken out of DI water, then a square-shaped chunk of PDMS stamped the nanomembrane. Then, the PDMS with the nanomembrane was ready to conduct transfer printing on external substrates. In the meantime, the diamond sample was cleaned by rubbing with Q-tips in IPA, acetone, and DI water. After that, the nanomembrane was printed on the diamond substrates.

Figure 2.7 The schematic diagram of the double-flip transfer.

**Figure 2.8** (a) After nanomembranes are undercut, the nanomembranes immediately float up on the surface of DI water. At this point, n+GaAs (base layer) does already face down to the DI water. (b) After scooping with PDMS described in **Figure 2.10**, the p+GaAs layer is directly contacting the PDMS, so as for n+GaAs to be directly contacting the diamond sample.

### c. Annealing and O<sub>2</sub> plasma treatment

Rapid Thermal Annealing at 350°C for 5 minutes was conducted on the transferred p-AlGaAs/n-GaAs/p-diamond sample in order to make a chemical bonding between the diamond and the nanomembrane. Then, the sample was treated with O<sub>2</sub> plasma of 100W for 20 seconds. Then, the sample became hydrophilic enough for proper photoresist coating.

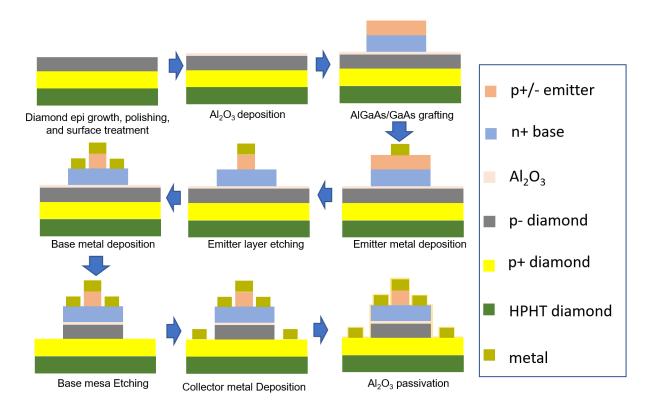

### d. Lithography and metallization

The negative photoresist, AZ5214, was coated on the diamond surface, using spinning of 2500rpm for 30 seconds, followed by baking the sample for 3 minutes at 95°C. Then, the sample was exposed under the emitter pattern for 2.2 seconds of 5.5 mW/cm² UV light, followed by baking it at 112°C for 90 seconds. Then, the sample was exposed UV light of 5.5 mW/cm² without a mask for 25 seconds. The properly UV-exposed sample was brought into AZ917 developer to develop for 30 seconds. After confirming that the emitter pattern was developed properly and

clearly, then the sample was metallized with a metal stack of Ti/Pt/Au (15nm/50nm/100nm). The process was followed by a dry etch process, which is the most critical step in the entire process. Because the window of the etch process is less than 25nm, the thickness of etch was measured by AFM after every cycle of the dry-etch process. After the entire etch process, surface conductivity on the nanomembranes was measured. It was confirmed by the high electric currents that n+ GaAs was exposed. Then, a base metal stack of Pd/Ge/Au (30nm/40nm/100nm) was deposited on the sample. The process was followed by covering photoresists (S1827, 4000rpm, and 30 seconds) with base-mesa patterns, and the sample was exposed to UV-light of 5.5 mW/cm<sup>2</sup> for 60seconds and developed in MF-321 for 90 seconds. Then, the patterned sample was dry-etched to remove nanomembranes not covered by the photoresist. Under the same photoresist pattern, the diamond was etched, using a 790 ICP etcher with the condition (RIE 250W, ICP 0W, CF<sub>4</sub> 90sccm, O<sub>2</sub> 2sccm and 50mT) until the p-layer of the diamond was fully etched and the p+ layer was exposed. Because there is a huge amount of difference in the resistivity between the p-layer and the p+layer on the surface, surface conductivity on the diamond was used as the criterion to confirm whether the p+ layer was exposed or not. After two etches for 6 minutes in total, the p+ layer of the diamond was fully exposed to the air, and the surface current was measured to be  $\sim 10^{-3} A$ . Then, the collector was metallized with a metal stack of Ti/Pt/Au (50nm/50nm/100nm). The process was directly followed by RTA of 350°C for 15 seconds. The fabrication was finalized by passivating the entire sample depositing ALD layers of 80 cycles of Al<sub>2</sub>O<sub>3</sub>.

Figure 2.9 The process flow of p+AlGaAs/n-GaAs/p-diamond DHBT.

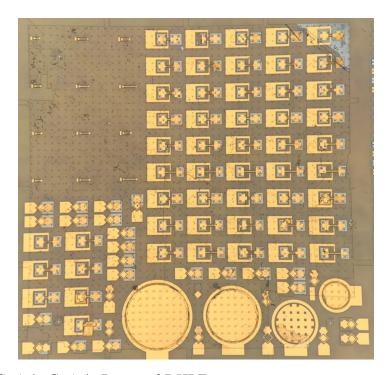

Figure 2.10 p-AlGaAs/n-GaAs/p-Diamond DHBT.

### 2.4 Results

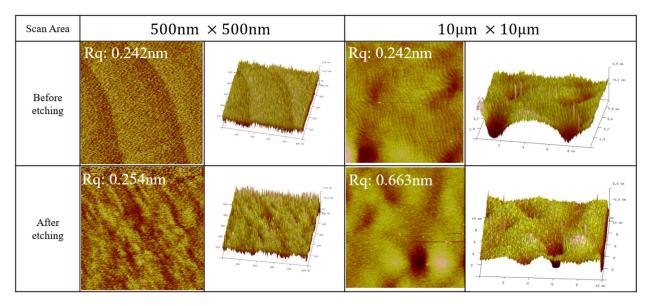

# a. AFM of p-GaAs/p-AlGaAs/n-GaAs nanomembranes

The double-flip transfer technique requires the n+ GaAs base layer to be exposed on the top surface of the nanomembrane wafers. One advantage of this fabrication process is the ability to adjust the base layer's thickness by dry-etching the nanomembrane samples before undercutting the sacrificial layers. Since the base layers directly contact the substrates, it is crucial to ensure that dry etching does not degrade the surface roughness. Plasma etching can create dangling bonds on a semiconductor surface, which can act as recombination centers [18]. The surface roughness of the samples before and after dry etching was measured using AFM, as shown in Figure 2.10. The results indicated that the surface quality did decrease, but it was still acceptable for transfer-printing without causing significant degradation to the final devices' performance.

**Figure 2.11** The AFM results of the top surface (a base layer) of nanomembranes before undercut.

### b. CTLM of p-GaAs/p-AlGaAs/n-GaAs nanomembranes

The conductivity of n-GaAs base layers must be low enough to ensure fast switching speed and low thermal loss in bipolar transistors. To measure the surface conductivity of the nanomembranes, a CTLM pattern was deposited on the bare nanomembrane samples, as illustrated in Figure 2.11. Since the base layer thickness can be adjusted before fabrication, the conductivity was measured for various base thicknesses (65nm, 45nm, and 35nm), as shown in Figure 2.12. The results suggest that there is no significant difference in surface conductivity between the different thicknesses, and the current is high enough for use as a base layer in HBTs.

Figure 2.12 The AFM results of the top surface (a base layer) of nanomembranes before the undercut.

Figure 2.13 The CTLM results of the samples with the base thickness of (a) 65nm, (b) 45nm, and (c) 35nm.

### c. Emitter-Base Diode IV characteristic of p-GaAs/p-AlGaAs/n-GaAs nanomembranes

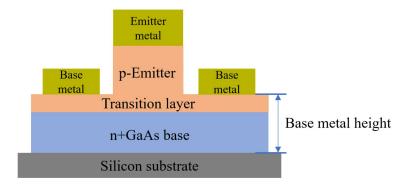

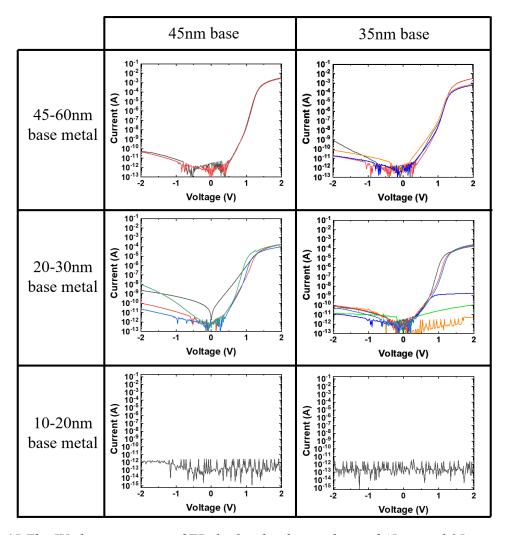

As there is a transition layer between the p-AlGaAs (emitter) and n-GaAs (base), shown in Figure 2.13, tests were conducted on silicon substrates to determine the optimal distance from the bottom of the base layer for depositing base metals. This was done to ensure the HBT will have the best emitter-base IV characteristics. The results and test settings are summarized in Figure 2.13 and 2.14. The results showed almost no current in cases where the base metal was metallized 10-20nm apart from the substrate. This could be due to the metal stack being in the depletion region between the n+GaAs base and the silicon substrate. The rectification was optimal when the base metal was deposited slightly above the base layer. Consequently, a 45nm base with metallization at points 45-60nm above the diamond surface was utilized for the actual DHBT fabrication.

Figure 2.14 The schematic diagram of EB diode transferred on silicon substrates.

Figure 2.15 The IV characteristics of EB diodes that have a base of 45nm and 35nm.

### c. AFM of p-diamond substrate

To increase the yield of grafting nanomembranes on substrates, the surface roughness should be low to ensure that the Van-der Waals force between the nanomembranes and the substrates is maximized. The AFM results of the measurements suggest that the surface of the diamond sample is smooth enough to proceed with effective grafting (Figure 2.15 and Figure 2.16).

Figure 2.16 The images of AFM on the diamond surface taken in the areas of 100μm by 100μm. The white squares of each figure represent the AFM scanning areas of 10μm by 10μm and the value below each square means the corresponding surface roughness. (a) The upper left side (b) The upper right side (c) The center, (d) The lower left, (e) The lower right side.

*Figure 2.17* The 3D visualization of the images featured in *Figure 2.5*. (a) The upper right side (b), The lower left side (c), and The lower right side.

### d. Engineering of the electron affinity of p-diamond substrate

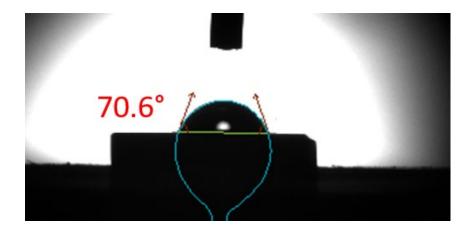

The diamond sample was sonicated in boiled acid (H<sub>2</sub>SO<sub>4</sub>:HNO<sub>3</sub> 3:1 at 100 °C, 20 minutes) and piranha solutions to clean the surface. The process was followed by ALD of pulsed H<sub>2</sub>O at 350 °C to suppress the electron affinity of the diamond sample (Figure 2.4). After treating the diamond, the contact angle of a water drop on the diamond surface was measured to determine the electron affinity, as shown in Figure 2.17. The measured angle of 70.6 degrees suggested that the electron affinity was tuned to 80meV – 100meV which is lower than that of the diamond surface of the prototype of AlGaAs/GaAs/C HBT (0.3eV) [3].

Figure 2.18 (a) The side view taken when the contact angle with a waterdrop on the diamond substrate in order to estimate the electron affinity of the diamond.

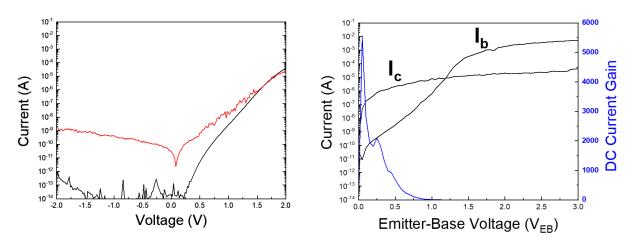

## e. IV characteristics of p+GaAs/p+AlGaAs/n-GaAs/p-diamond

The HBT performance was measured as shown in Figure 2.20. The IF of the emitter-base diode is 2.19, while that of the base-collector diode is 1.71. The  $I_{on}/I_{off}$  ratios of emitter-base and base-collector diode are  $5.96 \times 10^1$  and  $2.24 \times 10^4$  at  $\pm 1V$ , respectively. The DC gain was measured to be around ~2000 at the voltage region in which  $I_b$  is higher than  $10^{-10}A$ . This is the first successful HBT of p+GaAs/p+AlGaAs/n-GaAs/p-diamond that could be only possible by utilizing the semiconductor grafting techniques. The high  $I_{on}/I_{off}$  ratios and the low IF of the BC diode essentially prove that the semiconductor grafting technique indeed created epitaxy-like bipolar junctions between GaAs and C(diamond), which was not possible by the conventional epitaxy.

Figure 2.19 (a) A microscopic image of individual HBT (b) A filtered image of the same HBT.

Figure 2.20 (a) A microscopic image of individual HBT (b) A filtered image of the same HBT.

Figure 2.21 (a) Diode performance (Red – EB diode and Black – BC diode) (b) HBT performance (Offset  $V_{cb} = 0V$ )

### 2.5 Conclusion

The first DHBT of p-AlGaAs/n-GaAs/p-diamond has been demonstrated and tested with a record-high DC gain of around 2000 by the semiconductor grafting technique. To successfully fabricate the device, the electron affinity on the diamond substrate needed to be minimized to reduce the discontinuity in the valence band between the diamond substrate and the n+ GaAs layer. After the diamond was treated with chemical cleaning and depositing thin  $Al_2O_3$  layers on the surface, the electron affinity was estimated by measuring the contact angle of a waterdrop placed on the diamond surface. The measurement suggested that the electron affinity of the diamond is tuned to 70-100meV, which produced the discontinuity in the valence band of up to around 80meV, which is lower than that of the previous batch of diamond HBT ( $\sim 0.3 \text{eV}$ ) [3]. Then, the AFM was conducted to measure the surface roughness of both the diamond substrate (as a collector) and the n+ GaAs layer (as a base), which confirmed that they were smooth enough to form heterojunctions without significant defects (Figure 2.10 and 2.15). Then, the conductivity of base layers was measured by the CTLM method to ensure that the base layers contain a high concentration of ntype dopants. Then, the optimal base thickness and height of base metals from the substrate were determined by fabricating emitter-base junctions on a dummy substrate. This optimization was only made possible by the inverted nanomembrane structures whose base thickness can be adjusted by plasma etch before the fabrication. For the next step, the inverted structure of nanomembrane wafers was employed to produce the nanomembrane. In this structure, the base layer is exposed on the surface and the emitter layer is between the base layer and the sacrificial layer, unlike the conventional ones (Figure 2.5). In this way, the remaining AlAs sacrificial layer was not present on the base layer which must be kept in high quality without any extra layers for contacting the

diamond collector. To transfer print the nanomembrane of the inverted structure, the double-flip transfer was utilized as featured in Figure 2.6 and 2.7.

One of the fabricated DHBT showed the DC gain of up to 2000 (Table 2.1). However, the emitter-base diode performance demonstrated the low  $I_{on}/I_{off}$  ratio, and high IF factor, while the base-collector junction has relatively better diode performance. One of the reason for it is that the nanomembrane had been etched seven different times in order not to over-etch the nanomembrane. This essentially reduced the uniformity of etch, which made the fluctuation of emitter-base diode performance over the sample.

In the future, the device will be measured under high-speed, high-power, and high-temperature environments and its breakdown voltage to test if the device successfully reflects the characteristics of superior UWBG (diamond) and GaAs, including the carrier mobility of both materials and excessive critical field of the diamond material. Also, the yield needs to be higher by optimizing each step of the fabrication.

### 2.6 References

- [1] Wort, Chris JH, and Richard S. Balmer. "Diamond as an electronic material." *Materials today* 11.1-2 (2008): 22-28.

- [2] Pan, Lawrence S., and Don R. Kania, eds. *Diamond: Electronic Properties and Applications: Electronic Properties and Applications*. Vol. 294. Springer Science & Business Media, 1994.

- [3] Cho, Sang June, et al. "Fabrication of AlGaAs/GaAs/diamond heterojunctions for diamond-collector HBTs." *AIP Advances* 10.12 (2020): 125226.

- [4] Donato, Nazareno, et al. "Diamond power devices: state of the art, modelling, figures of merit and future perspective." *Journal of Physics D: Applied Physics* 53.9 (2019): 093001.

- [5] Pearton, S. J., et al. "A review of Ga2O3 materials, processing, and devices." *Applied Physics Reviews* 5.1 (2018): 011301.

- [6] Vescan, A. I. P. W. E., et al. "High temperature, high voltage operation of diamond Schottky diode." *Diamond and related materials* 7.2-5 (1998): 581-584.

- [7] Ueda, Kenji, Keita Kawamoto, and H. Asano. "High-temperature and high-voltage characteristics of Cu/diamond Schottky diodes." *Diamond and Related Materials* 57 (2015): 28-31.

- [8] Gluche, P. A. A. W. E., et al. "Diamond surface-channel FET structure with 200 V breakdown voltage." *IEEE Electron Device Letters* 18.11 (1997): 547-549.

- [9] Umezawa, Hitoshi, Takeshi Matsumoto, and Shin-Ichi Shikata. "Diamond metal—semiconductor field-effect transistor with breakdown voltage over 1.5 kV." *IEEE Electron Device Letters* 35.11 (2014): 1112-1114.

- [10] Nesladek, Milos. "Conventional n-type doping in diamond: state of the art and recent progress." *Semiconductor Science and Technology* 20.2 (2005): R19.

- [11] Koizumi, Satoshi, and Mariko Suzuki. "n-Type doping of diamond." *physica status solidi* (a) 203.13 (2006): 3358-3366.

- [12] Suzuki, Mariko, et al. "Electrical characterization of diamond Pi N diodes for high voltage applications." *physica status solidi (a)* 210.10 (2013): 2035-2039.

- [13] Saremi, Mehdi, et al. "Analysis of the reverse IV characteristics of diamond-based PIN diodes." *Applied Physics Letters* 111.4 (2017): 043507.

- [14] Liu, Dong, et al. "Lattice-mismatched semiconductor heterostructures." *arXiv preprint arXiv:1812.10225* (2018).

- [15] Kim, Jisoo. "Study on Heterostructure Semiconductor Devices Using Grafting Technique,"

University of Wisconsin-Madison, Ph.D. dissertation.

- [16] Wasilewski, Z. R., et al. "Composition of AlGaAs." *Journal of applied physics* 81.4 (1997): 1683-1694.

- [17] Stanton, Morgan M., et al. "Super-hydrophobic, highly adhesive, polydimethylsiloxane (PDMS) surfaces." *Journal of colloid and interface science* 367.1 (2012): 502-508.

- [18] Shul, R. J., et al. "Investigation of plasma etch induced damage in compound semiconductor devices." *Journal of Vacuum Science & Technology A: Vacuum, Surfaces, and Films* 12.4 (1994): 1351-1355.

# Chapter 3

# Fabrication and Characterization of AlGaAs/GaAs/GaAsP/GaN DHBT by Nanomembrane Grafting

### 3.1 Introduction