# Mechanisms Towards Energy-Efficient Dynamic Hardware Specialization

by

Chen-Han Ho

# A dissertation submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

(Computer Sciences)

## at the

## UNIVERSITY OF WISCONSIN-MADISON

#### 2014

Date of final oral examination: 10/30/2014

The dissertation is approved by the following members of the Final Oral Committee: Gurindar Sohi, Professor, Computer Science Mark Hill, Professor, Computer Science David Wood, Professor, Computer Science Nam Sung Kim, Associate Professor, Computer Science Karu Sankaralingam, Associate Professor, Computer Science

© Copyright by Chen-Han Ho 2014 All Rights Reserved

#### ACKNOWLEDGMENTS

First I would like thank my advisor Karu Sankaralingam, who had continuously supported my study and research. Without your patience, tutelage, enthusiasm and knowledge this work would have never been written. Thank you, Karu.

Besides my advisor, I would like to thank the rest of my graduation committee members: Dr. Gurindar Sohi, Dr. Mark Hill, Dr. David Wood, and Dr. Nam Sung Kim. Guri pushed me to think critically and to revisit the insights in past ideas when formulating new solutions. Mark gave me many inspiring comments, which are not only for research but also for the life and career; his teaching and mentoring style was one of my pursuits. David was a great listener (with year-round warm and smiling face), and he found many new possibility to very specific things in my research. I especially thank to Nam for encouraging me after an exhaustive preliminary exam.

I thank the CS and ECE faculty for so many wonderful courses, with special thanks to Dr. Mary Vernon and Dr. Susan Horwitz, who taught me patiently and sparked my interests in different areas. A special acknowledgement goes to Dr. Azadeh Davoodi for her teaching, mentoring and support; I greatly appreciate her recognition in my first few years in Madison. I would also like to thank Dr. Doug Burger at Microsoft Research, who is an alumnus of UW-Madison, and Dr. Hadi Esmaeilzadeh at Georgia Tech for the support on Neural Processing Units.

Thanks to the Vertical group. In particular I have received significant help and learned many skills from my collaborator Dr. Venkatraman Gvindaraju. Thanks to the DySER prototyping team, Jesse, Chris, Ryan, Zach, Preeti, and Ranjini, who all did a great work and made DySER real. Amit, Shuou, Matt, Emily, Raghu, Jai, Jin, Newsha, Vinay, and Vijay: thank you for your feedback and support. Thanks to Ziliang for the great help on writing in English. Thanks to Tony for all the fun discussions and cultural knowledge. Special thanks to Marc de Kruijf, for being more than supportive and for showing me how to write and think with ease and elegance.

Thanks to everyone in the computer architecture group. Srinath and Gagan: thank you for many stimulating discussions. Jason and Marc: thank you for all the valuable feedbacks. Nilay and Joel: thank you for the discussions and help on the simulator. Rathijit, Somayeh, Hamid, Shoaib, Srinath, Gagan, Hongil, Lena, and Jayneel: thank you and it is my pleasure to be one of the group.

Many thanks to the architecture alumni, with special thanks to Dr. Kevin Moore for his mentoring and support. Thank you Jichuan for all the favors and advices. Dan: I did use the SPARC machine for good, not evil; you may not know but I learned many from your work. Min, Luke, Derek, Polina, and Arka: thank you and I appreciate your help.

Thanks to Oracle Labs and Lawrence Livermore Laboratory for the internships. Special thanks to Erik Schlanger, my supervisor at Oracle Labs, for his kind help and many career advices. I would also like to thank Greg Wright at Qualcomm, who gave insightful comments to this work in different aspects.

Thanks to the faculty of National Taiwan University, with special thanks to Dr. Hsu-Chun Yen, Dr. Wanjiun Liao, and Dr. Farn Wang, who never hesitate to provide help and support. Without you I could never be prepared to be in a PhD program.

Finally, I would like to thank my family. You may not know what this work is about but you are always my strongest support.

Contents iii

List of Tables vi

List of Figures vii

Abstract ix

- **1** Introduction 1

- 1.1 Building Specialized Hardware 2

- 1.2 Dynamically Specialized Execution 3

- 1.3 Contributions 5

- 1.4 Dissertation Organization 7

- 2 Hardware Specialization and Dynamically Specialized Execution (DySE) 8

- 2.1 Hardware Specialization, Background and Examples 8

- 2.2 Dynamically Specialized Execution 15

- 2.3 Manual and Compiler-Assisted DySE 21

- 2.4 Chapter Summary 26

- 3 Dynamically Specialized Execution Resources (DySER) 27

- 3.1 DySER Design Goals and Overview 27

- 3.2 DySER Internal Microarchitecture 29

- 3.3 Configuring DySER 33

- 3.4 Integrating DySER 35

- 3.5 Chapter Summary 43

## 4 SPARC-DySER Prototype 44

- 4.1 SPARC-DySER Integration 44

- 4.2 Incorporating DySER into OpenSPARC 47

## 4.3 Summary and Lessons Learned 49

## 5 Memory Access Dataflow (MAD) 50

- 5.1 MAD Design Goals 50

- 5.2 Memory Access Dataflow Overview 53

- 5.3 MAD Microarchitecture 59

- 5.4 Complex Scenarios 65

- 5.5 Integration 68

- 5.6 Chapter Summary 70

## 6 Evaluation Methodology 71

- 6.1 Architectural Models 71

- 6.2 Benchmarks 74

- 6.3 Measurements and Metrics 75

## 7 Evaluation 79

- 7.1 DySER with Host General Purpose Processor as The Access Engine 79

- 7.2 DySER with MAD 88

- 7.3 MAD Driving Other Execute Accelerators 93

- 7.4 MAD Executing Access-Only Benchmarks 97

- 7.5 Chapter Summary 98

## 8 Related Work 100

- 8.1 DySER and Execute Architectures 100

- 8.2 MAD and Access Architectures 103

- 8.3 Chapter Summary 105

## 9 Conclusions and Future Work 106

- 9.1 Contributions and Conclusions 106

- 9.2 Future Work 107

- 9.3 Reflections 108

- A The Encoding of MAD ISA 112

- A.1 Dataflow Graph Node 112

- A.2 ECA Rules 113

- **B** The Set/Reset Protocol 114

Bibliography 117

## LIST OF TABLES

| 4.1 | OpenSPARC RTL modifications (comments included)                                                                                                                          | 45  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.2 | A stylized listing of the DySER instructions                                                                                                                             | 46  |

| 4.3 | Design of the DySER instruction extensions for OpenSPARC                                                                                                                 | 46  |

| 4.4 | Summary of the performance evaluation works                                                                                                                              | 49  |

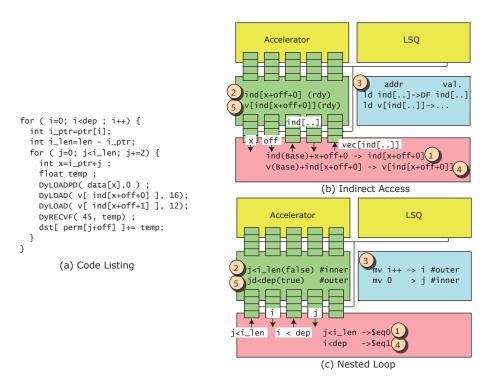

| 5.1 | Dataflow patterns: Exec Comp.: Execute component, Acc. I/F: Accelerator interface instructions in the access component code, SP: Stack pointer, Off.: Offset, Base: Base |     |

|     | address                                                                                                                                                                  | 55  |

| 6.1 | General purpose host processor models                                                                                                                                    | 72  |

| 6.2 | Architectural models                                                                                                                                                     | 72  |

| 6.3 | Benchmarks in evaluation                                                                                                                                                 | 76  |

| 7.1 | Power breakdown of DySER's sub-modules                                                                                                                                   | 86  |

| 8.1 | Comparison to related work                                                                                                                                               | 104 |

| A.1 | The encoding of the dataflow graph                                                                                                                                       | 113 |

| A.2 | The encoding of the ECA rules                                                                                                                                            | 113 |

## LIST OF FIGURES

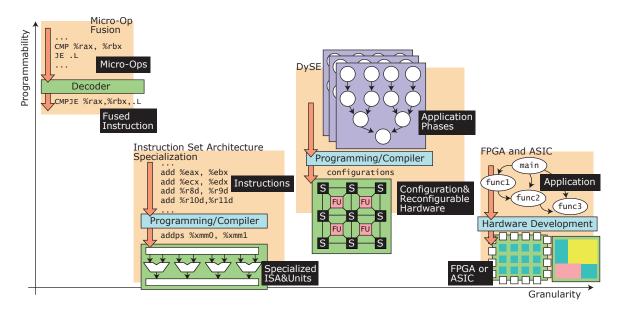

| 2.1  | Hardware Specialization Taxonomy                                                 | 9  |

|------|----------------------------------------------------------------------------------|----|

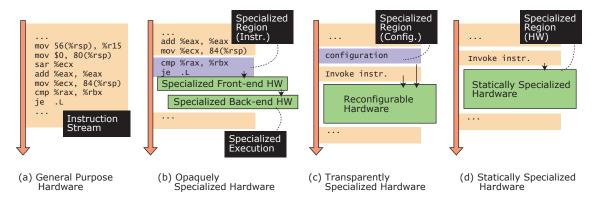

| 2.2  | Hardware specialization execution model                                          | 10 |

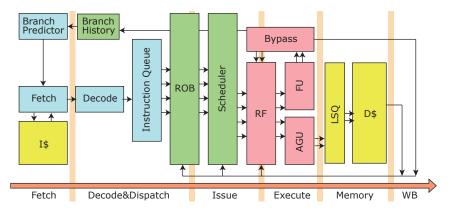

| 2.3  | An out-of-order general purpose processor pipeline                               | 13 |

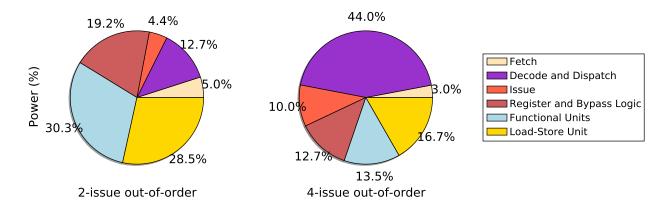

| 2.4  | Power breakdown of 2 and 4-issue out-of-order processor pipeline, modeling Intel |    |

|      | Silvermont and Sandy Bridge                                                      | 14 |

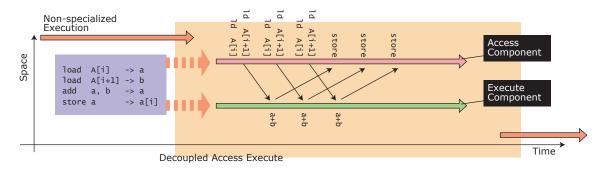

| 2.5  | Decoupled Access/Execute                                                         | 16 |

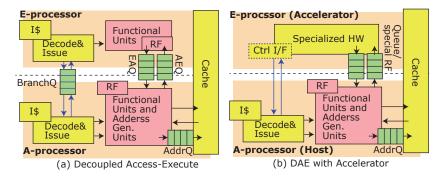

| 2.6  | Decoupled Access/Execute: microarchitecture                                      | 17 |

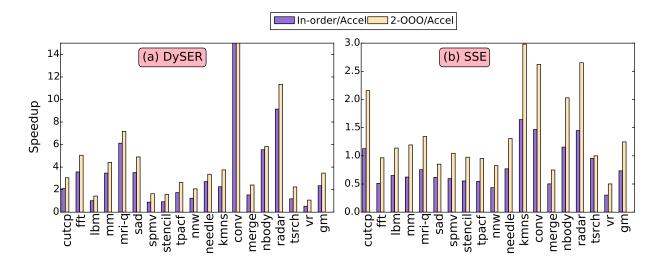

| 2.7  | Performance of 2-issue OOO vs. 1-issue in-order with accelerator                 |    |

|      | Speedups normalized to non-accelerated 2-OOO for both bars                       | 20 |

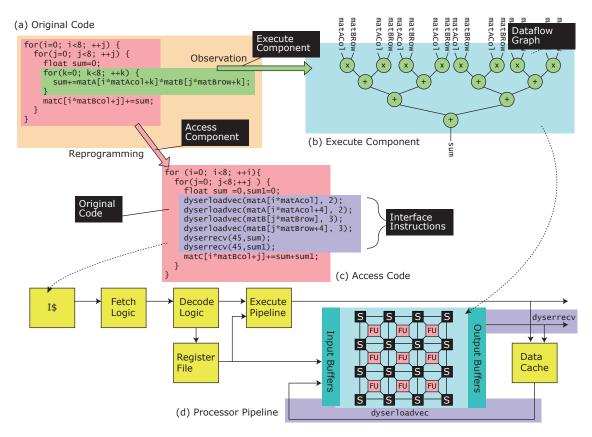

| 2.8  | Manual DySE programming                                                          | 22 |

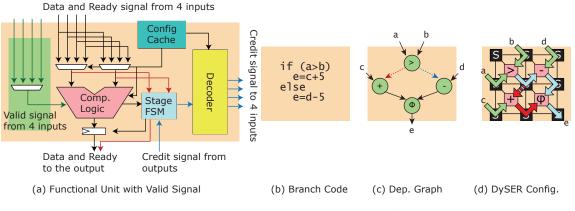

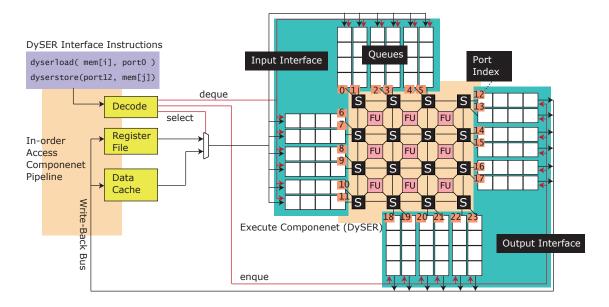

| 3.1  | Dynamically Specialized Execution Resources (DySER)                              | 28 |

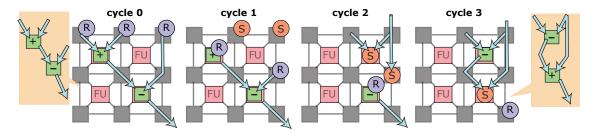

| 3.2  | DySER microarchitecture: the network of switches and functional Units            | 29 |

| 3.3  | DySER microarchitecture: switch                                                  | 30 |

| 3.4  | DySER microarchitecture: functional unit                                         | 31 |

| 3.5  | DySER microarchitecture: Phi-function                                            | 32 |

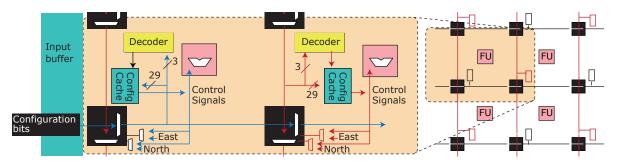

| 3.6  | DySER microarchitecture: configuration mode                                      | 33 |

| 3.7  | Fast config switching example                                                    | 34 |

| 3.8  | Fast config switching in a DySER switch                                          | 35 |

| 3.9  | Simple queue-based DySER interface                                               | 36 |

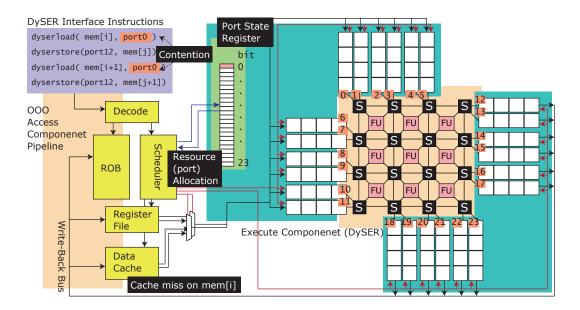

| 3.10 | OOO DySER interface                                                              | 37 |

| 3.11 | OOO DySER interface with speculative execution                                   | 38 |

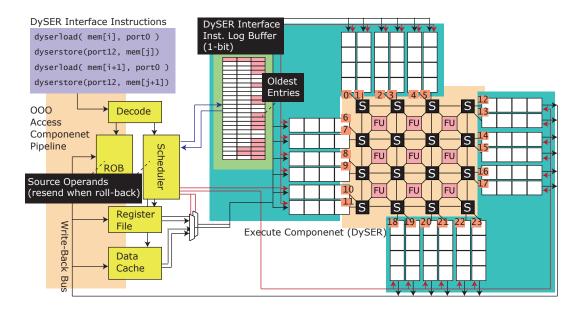

| 3.12 | OOO DySER interface: An alternative solution                                     | 40 |

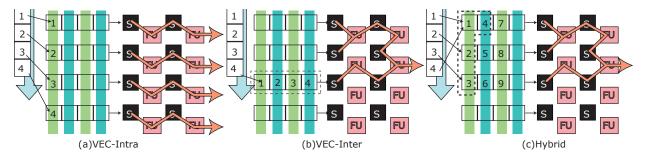

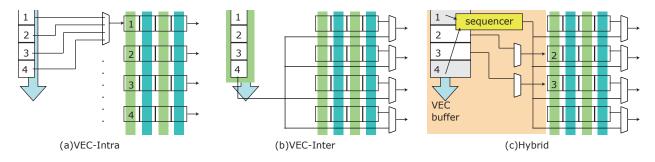

| 3.13 | Vector port mapping                                                              | 41 |

| 3.14 | Vector port mapping: microarchitecture                                           | 42 |

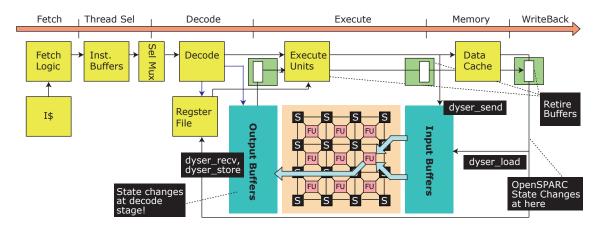

| 4.1  | SPARC-DySER integration                                                          | 48 |

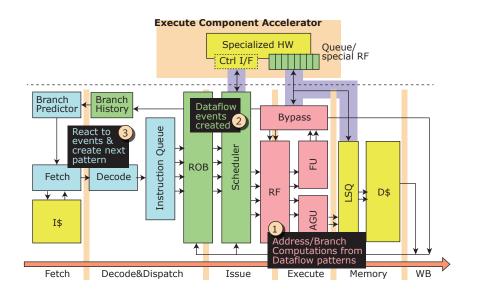

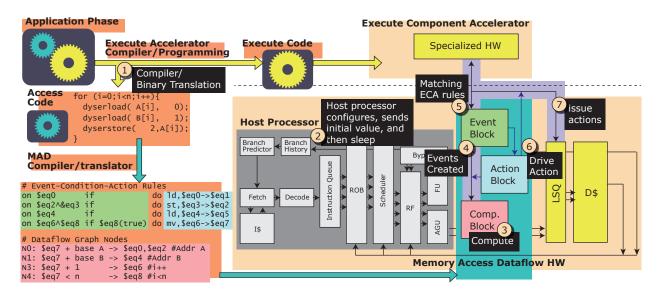

| 5.1  | The block diagram and the execution of an out-of-order host processor with an |    |

|------|-------------------------------------------------------------------------------|----|

|      | accelerator                                                                   | 51 |

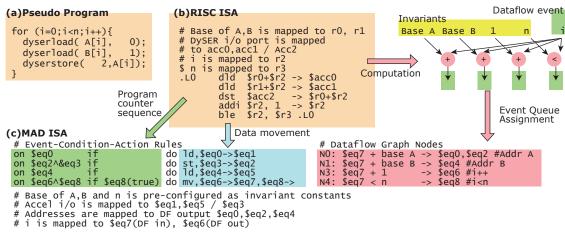

| 5.2  | The MAD ISA                                                                   | 54 |

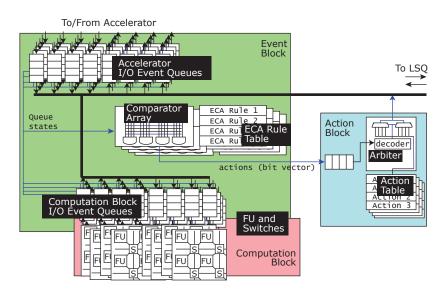

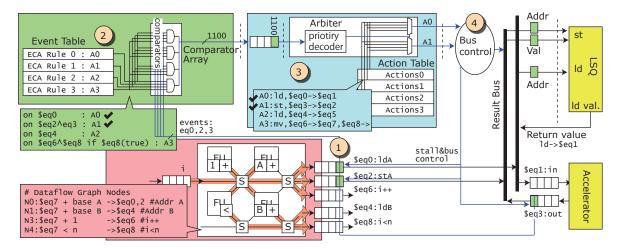

| 5.3  | An example execution of the MAD hardware                                      | 57 |

| 5.4  | MAD microarchitecture                                                         | 60 |

| 5.5  | Detailed MAD execution with a simple code                                     | 63 |

| 5.6  | MAD execution with a complex example                                          | 64 |

| 5.7  | The integration of accelerators and the MAD hardware                          | 67 |

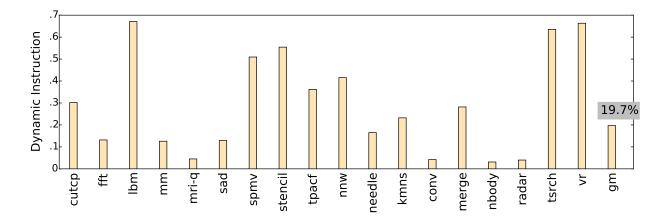

| 7.1  | The reduced dynamic instructions in percentages                               | 80 |

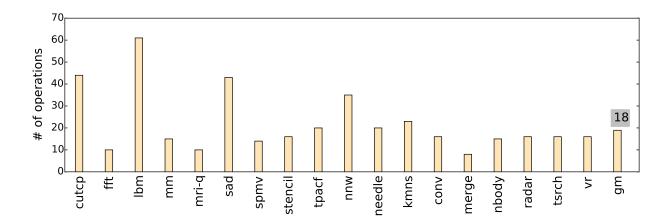

| 7.2  | Execute component size in operations                                          | 81 |

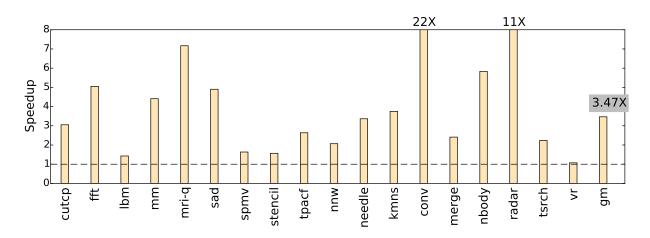

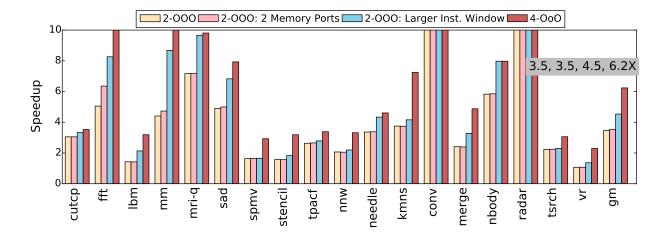

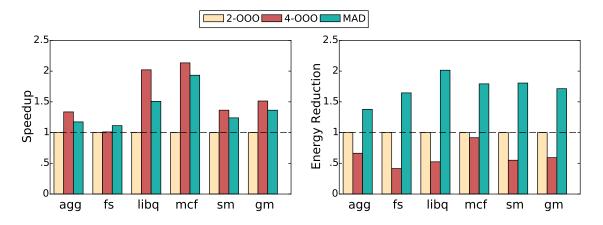

| 7.3  | Speedup over 2-OOO baseline                                                   | 81 |

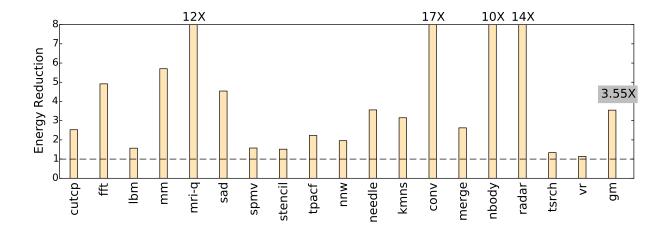

| 7.4  | Energy reduction over 2-OOO baseline                                          | 82 |

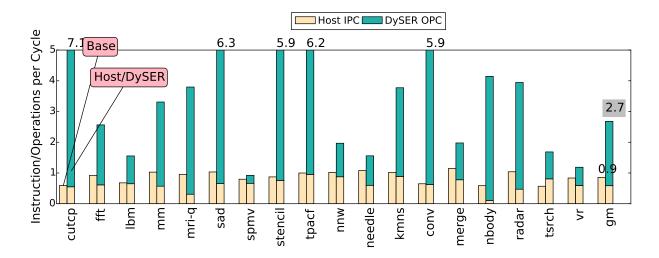

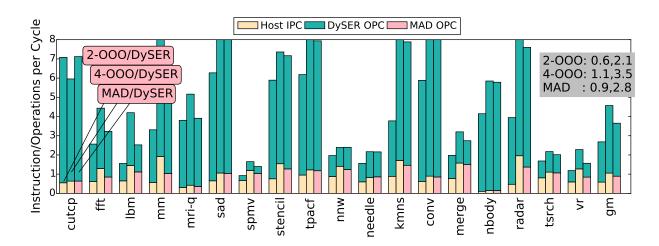

| 7.5  | Instruction and operation level parallelism                                   | 84 |

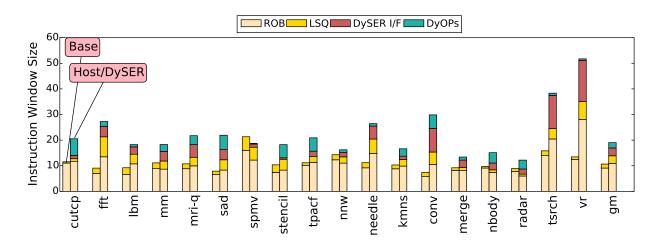

| 7.6  | Instruction window size                                                       | 84 |

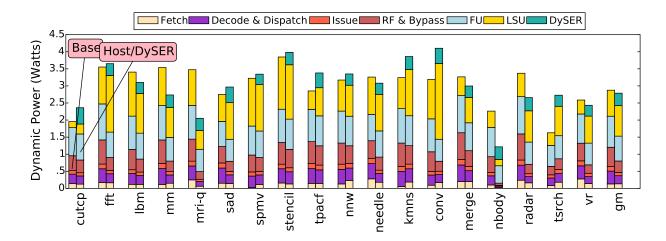

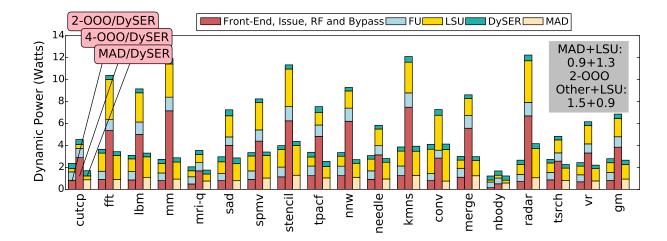

| 7.7  | Dynamic power                                                                 | 85 |

| 7.8  | DySER's sensitivity on different access hardware                              | 87 |

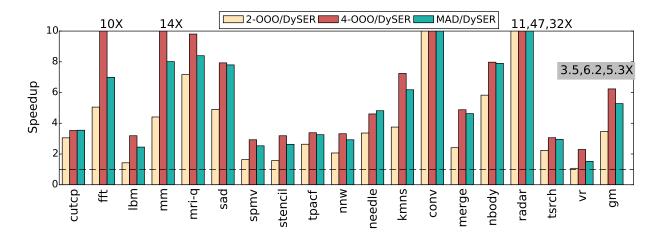

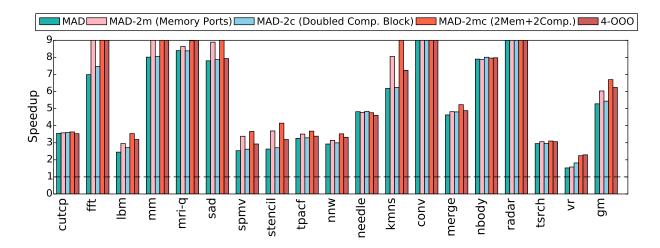

| 7.9  | Speedup over 2-OOO baseline                                                   | 88 |

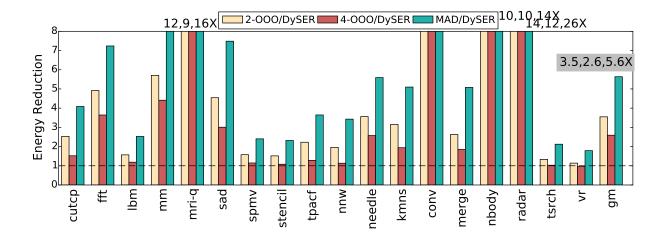

| 7.10 | Energy reduction over 2-OOO baseline                                          | 89 |

| 7.11 | Parallelism in MAD/DySER                                                      | 90 |

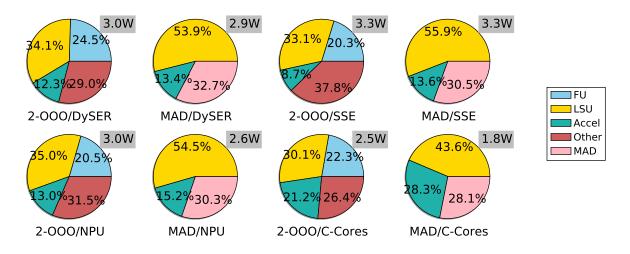

| 7.12 | Dynamic power                                                                 | 91 |

| 7.13 | MAD's sensitivity on hardware resources                                       | 92 |

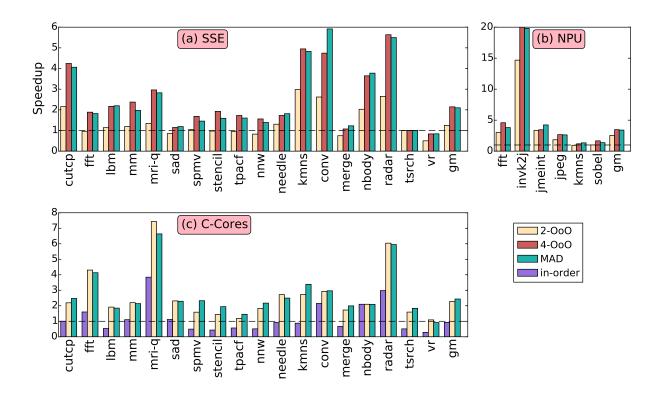

| 7.14 | Performance of MAD/Accelerators                                               | 94 |

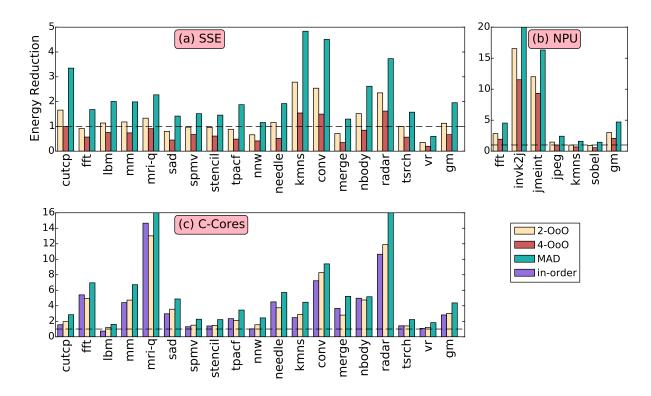

| 7.15 | Energy reduction of MAD/Accelerator                                           | 95 |

| 7.16 | Energy reduction of MAD/Accelerator                                           | 96 |

| 7.17 | MAD (Access-only) performance and energy                                      | 97 |

#### ABSTRACT

In the past few decades, Von Neumann superscalar processors have been the prevalent approach for general purpose processing. Hardware specialization, as a complementary technique, offers superior performance, power or energy efficiency on specific tasks. Today, with an increased focus on energy critical platforms such as datacenters and mobile devices, hardware specialization are becoming an important and widely used approach to improving the overall efficiency.

Our work is motivated by observing that in frequent program phases, using specialized hardware could eliminate the conventional "instruction processing" in a superscalar pipeline. To this end, we propose two supporting architectures, for both computation and data acquisition, under a hardware-software co-designed execution model– Dynamically Specialized Execution (DySE). This model leverages re-configurable hardware and decoupled access/execute for energy efficiency, generality and flexibility. The two architectures discussed in this dissertation are: Dynamically Specialized Execution Resources (DySER) and Memory Access Dataflow (MAD). Decoupling access and execute components in a program phase enables different optimization opportunities in hardware. DySER, the supporting architecture for the execute component, is a circuit-switched functional unit fabric that can be viewed as a long-latency, multi-input and asynchronous unit. MAD, on the other hand, is an event-driven dataflow memory access engine. It efficiently performs two primitive tasks found in a superscalar processor: (1) computations that generate recurring address patterns/branches; (2) event-condition evaluations that trigger resulting data movements. By turning off the host, using MAD to drive the accelerators delivers energy improvement compared to an out-of-order host processor.

This dissertation has the following findings: First, we prove that DySER is a viable approach by building a SPARC-DySER prototype, which integrates DySER into OpenSPARC. In the evaluation of DySER, we observe 80% saving in dynamic instruction count,  $3.47 \times$  speedup and  $3.55 \times$  energy reduction over a power-efficient 2-issue out-of-order processor; DySER increases the parallelism for such speedup through its hardware, vector interface, and decoupled access/execute. Second, we support DySER with MAD and increase the overall speedup and energy reduction over the same base to  $5.3 \times$  and  $5.6 \times$ , respectively. MAD can also drive other execute accelerators or perform access-only codes for energy-efficiency. Compared to a 2-issue superscalar host, MAD increases the parallelism and lowers the power consumption through its microarchitecture, which benefits from the exposure of computation, dataflow events and actions in the MAD ISA.

#### 1 INTRODUCTION

In the past few decades, process scaling has offered doubled transistors on a chip every generation as Moore's Law predicts. The performance of processors has consequently increased with constant power density by leveraging these smaller and faster transistors that consume less power. Conventionally, computer architects pipeline the microarchitecture for a faster clock frequency, and spend the raised transistor budget on speculative execution and dynamic scheduling (e.g., branch predictors and out-of-order execution). However, these microprocessor design techniques eventually hit the Power Wall. The frequency scaling ends because of practical thermal limitations; moreover, the power density per unit area has been increased over generations because of the breakdown of Dennard Scaling [41]. As a result, the industry shifted to Chip Multiprocessors (CMPs) and mitigated this problem by offering better performance through thread-level parallelism. Fundamentally, the Power Wall still exists, and the evidence of the incapacity of the traditional core architecture design has been discovered recently. Azizi et al. [14] show that microprocessor design techniques like changing issue width, improving prediction accuracy, etc. cannot provide significant improvements in energy efficiency as the . Specifically, they show that a dual-issue out-of-order processor, under voltage and frequency scaling, is within 3% of the energy-delay metric of any other out-of-order processing design. Esmaeilzadeh et al. [44] show that power limitations of conventional microprocessor techniques will severely curtail the performance, and significant changes are required to match the historical annual cumulative performance growth of 30% to 40%.

In general, the dynamic power consumption of a CMOS circuit could be represented as follows:

$$P = ACV_{dd}^2 F$$

Where *P* is the dynamic power, *A* is the activity factor (the switching activity of the circuit), *C* is the capacitance of the circuit,  $V_{dd}$  is the supply voltage and *F* is the clock frequency. Among the above variables, the scaling on supply voltage *V* is not enough, and capacitance *C* and the frequency *F* are held constant for performance. Computer architects, consequently, turn to hardware specialization to lower the activity factor *A* [103, 45, 122, 57, 34, 47, 100, 88]. By

reducing the reliance on power hunger structure in a general purpose pipeline, hardware specialization decreases the overall switching activity yet provides similar or even improved performance. I begin this dissertation with a discussion on general-purpose hardware, from which I describe how hardware specialization improves energy efficiency. Next, I develop Dynamic Hardware Specialization (DySE) to address the demands found in the observations. I show how Dynamic Hardware Specialization and its supporting architectures tackle the issues in energy efficiency. I then briefly outline my contributions in this work and summarize this chapter with an overview of this dissertation.

# 1.1 Building Specialized Hardware

General purpose hardware, typically, executes an application in the following steps. First, the execution pipeline fetches the application as instructions from the instruction cache sequentially. Second, these instructions are decoded, where each of the decoded instructions carries a piece of information in the application. In a limited instruction window, the information from instructions is analyzed and scheduled to drive the execution units and storage inside the pipeline. The instruction window is either the same as the issuing width or is much larger in the case of out-of-order execution. To utilize the pipeline more aggressively, speculation is often used with out-of-order execution to schedule the speculated instructions and pay the potential recovery cost in mis-speculations. The above fetch, decode and issue stages are the front-end of the pipeline. Last, the back-end of the pipeline, which operates on the work of the application, is composed of the execution units and the data from storage. The execution units read from register file and data cache for operation, and write the resulting data values back. The controlling and forwarding signals of the execution units and storage are produced dynamically by the information from the front-end.

Specialization alters the general purpose hardware with specific optimizations. In the frontend, a specialization approach changes the general purpose execution model such that there is less dynamic scheduling (which saves power) in a given instruction window. For example, the Single-Instruction-Multiple-Data (SIMD) execution model operates on multiple data. Compared to using multiple instructions, SIMD effectively reduce the overall instruction scheduling. In the back-end, the execution units may be specialized for some sophisticated application. Depending on the granularity, the execution units may be organized to reduce the overhead in dynamically producing the controlling and forwarding signals. For example, C-Cores [122] lays out the execution units in a region of the pipeline as a single piece in hardware; the control of its execution units, data access and forwarding datapath are all statically routed and performed to save power. Another optimization in the back-end is to optimize the data acquisition mechanism. Specialized memory [90, 30], registers [108], and/or scratch pad memory [67, 40] are examples of this optimization. There are also proposals only focused on data acquisition such that they use a simple in-order Von Neumann pipeline with optimized memory and memory interface [77] to achieve energy efficiency.

# 1.2 Dynamically Specialized Execution

This dissertation seeks to provide a comprehensive hardware specialization which eliminates the per-instruction overheads in both the front-end and the back-end of a general purpose processor pipeline. This approach, called *Dynamically Specialized Execution (DySE)*, leverages an alternative execution model based on Decoupled Access/Execute [112] to effectively create a huge instruction window with "ultra-wide" instructions. In the DySE execution model, the application is abstracted as a sequence of ultra-wide instructions (through compiler or programming techniques), each representing an application phase. Before entering a specialized application phase, the host general purpose processors *dynamically* configure the hardware to specialize for these application phases. In an application phase, the code is divided into access (memory loads and stores) and execute components (mainly computations), where the two components are executed on different hardware substrates. This decoupling thus allows different optimizing opportunities. By dynamically configuring and reusing of the configured phases, the specialized hardware substrate is able to target a variety of different applications.

Two supporting architectures are proposed under the DySE model, *Dynamically Specialized Execution Resources (DySER)* and *Memory Access Dataflow (MAD)*. They are hosted by a general

purpose processor pipeline and can be used separately or together to maximize the energy efficiency. First, DySER is proposed as a non-intrusive, multi-ported, long latency and asynchronous execution unit in the processor pipeline. It can be integrated into the host processor pipeline non-intrusively with instruction set extensions and interface buffers, and performs the execution component in an application phase. Second, MAD is motivated from the fact that driving specialized execution units, such as DySER, with host general purpose processor pipeline incurs significant overhead. In an application phase that executes with a specialized execution hardware substrate, the host general processor's role is merely delivering data from the cache to the substrate. As a result, a light-weight memory access dataflow engine, MAD, can be employed to access the cache and move the data between cache and the specialized hardware.

The design goals of DySE, DySER and MAD are as follows:

- Energy efficiency: The DySE model is proposed to remove the overheads in general purpose hardware. It aims at energy efficiency such that using DySER and MAD brings power efficiency (removing the overheads) with improved performance. DySE achieves power efficiency by decoupling the access and execute code, thus creating an extremely large instruction window without general purpose structures. DySER and MAD then perform the execution and data acquisition with their efficient dataflow microarchitecture. On the performance side, MAD and DySER extract instruction and data level parallelism in the access and execute code, utilizing a vectorized memory interface.

- Area efficiency and programmability: While Application-Specific Integrated Circuits (ASICs) can be built for different applications or application phases, DySE dynamically specializes the application phases on DySER and MAD and achieves area efficiency. To this end, DySER and MAD are designed for reconfigurability. In the DySE model, compiler or programming techniques can be used to identify the profitable application phases and create the configuration bits. This model removes the dynamic energy overhead of using hardware to analyze applications and phases at runtime for constructing specialized datapath.

- Design complexity and flexibility: The DySE model and the supporting architectures are

designed as a viable and flexible approach. A compiler framework was also developed for decoupling the access and execute component and generating optimized configuration automatically. This access/execute decoupling reduces the hardware design complexity, offering a well-defined flexible interface between host processor, DySER and MAD. With this interface, the host processor can use DySER, MAD or both of them. When using DySER alone, the access code can be executed on the host processor so that it is responsible for both configuration and data delivery. When applying both MAD and DySER, the host processor can be turned off during the specialized application phase to save power. In the case that the application phase is mostly composed of data accesses (e.g. a linked-list traversal), MAD can also be used alone with no execution specialization.

# **1.3 Contributions**

This dissertation makes contributions by conceiving the Dynamically Specialized Execution model (DySE, Section 1.3.1) and the two supporting architectures, Dynamically Specialized Execution Resources (DySER, Section 1.3.2) and Memory Access Dataflow (MAD, Section 1.3.3). It studies the aspects of microarchitecture, architecture, the execution model, compiler and application to explore the benefits of dynamic specialization.

## 1.3.1 Dynamically Specialized Execution

The hardware specialization approaches can be roughly classified under two different building philosophies: specialization at fine granularity, focusing only on computation or execution units, or specialization at a coarse granularity that encapsulates the execution units, data access mechanism, and the control logic holistically. The first contribution of this work is the DySE model (Chapter 2), which captures both computation and memory access in application phases at a coarse-grained level but achieves fine-grain specialization efficiency by decoupling access and execute to enable efficient hardware optimization. Second, this dissertation supports DySE with a few observations about application phases and the energy efficiency of a general purpose superscalar pipeline. It develops the entire software/hardware stack and describes how to

decouple the access and execute components with compiler or programming techniques. This decoupled execution addresses the inefficiencies in a general purpose pipeline by leveraging specialized architectures.

## 1.3.2 Dynamically Specialized Execution Resources

This dissertation proposes the specialized hardware architecture for the execute component in the DySE model. It describes this hardware, Dynamically Specialized Execution Resources (DySER, Chapter 3), in terms of the architecture and microarchitecture details. DySER dynamically synthesizes specialized datapaths for computation operators in an application phase and relies on the host processor or MAD to deliver the data. To explain the latter, this dissertation discusses the integration of DySER with an out-of-order processor or MAD, as well as the microarchitectural interface and DySER's reconfigurability. It then presents a thorough analysis on Parboil [6], Throughput Kernels [110] and Rodinia [25] benchmarks to show the overall performance, power and energy efficiency (Chapter 7); this dissertation also conducts a series of microarchitectural analyses to reveal the tradeoffs and potential bottlenecks. DySE and DySER are joint works with my collaborator , Venkatraman Govindaraju [58].

To prove that DySER is a flexible and viable approach, this dissertation demonstrates SPARC-DySER, an OpenSPARC T1 processor integrated with DySER, with a FPGA prototype. It details the practical integration issues, and the lessons learned from bringing up a prototype. Chapter 4 gives a strong evidence that one can straightforwardly build DySER following its design specification and integrate it with a commercial processor.

#### 1.3.3 Memory Access Dataflow

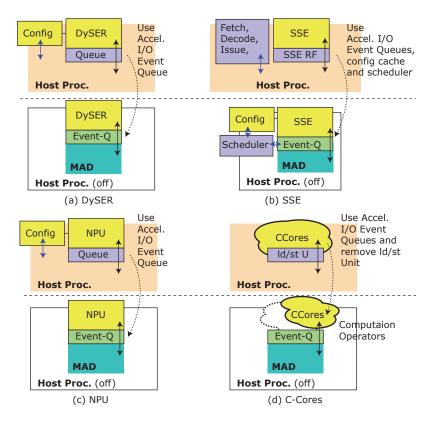

Last, this dissertation proposes the specialized hardware architecture for the access component in the DySE model, Memory Access Dataflow (MAD, Chapter 5). MAD is the first work to provide a unified interface for all accelerators and specialized hardwares that fit in DySE (or the Decoupled Access/Execute model). It introduces the event-action dataflow ISA to expose the data movement to the MAD hardware. This dissertation illustrates the execution flow of MAD, the architecture, microarchitecture, and the integration details of DySER and MAD. It also discusses the integration between MAD and three other accelerators, x86 Streaming SIMD Extensions (SSE) unit, Neural Processing Unit [45], and Conversation Cores [122].

# 1.4 Dissertation Organization

Chapter 2 discusses the motivation, background material, and related work of Dynamically Specialized Execution. Chapter 3 elaborates DySER's architecture and microarchitecture designs, and Chapter 4 integrates DySER into OpenSPARC T1. Chapter 5 develops the MAD architecture with supporting examples. Chapter 6 discusses the experimental setup and evaluation methodology. Chapter 7 first evaluates DySER with the host processor delivering the data; it then evaluates MAD with DySER, MAD with other accelerators, and a special case where MAD is used alone, without execute accelerators, for access-only application phases. I conclude this dissertation in Chapter 9 and summarize the key insights, findings, and future work.

The contents of Chapter 2, 3 and 7 inherit from my prior publications, HPCA2011 [57] and IEEE-MICRO2012 [59]; they overlap with the dissertation of Govindaraju [58], my collogue and the co-author of the above publications, but provide more detail and differ in evaluation. Regarding differences, Chapter 2 focus on hardware rationale and manually optimized data parallel benchmarks. Chapter 3 and 7 focuses on the microarchitecture and analyses that details the potential overheads of the microarchitecture design. The content of Chapter 4 is a follow-up work of published prototype at HPCA2012 [18]; this Chapter discusses the integration and design choices in-depth. Last, the MAD architecture described in Chapter 5 and its evaluation differ from the prior work [28] with a more developed design.

# 2 HARDWARE SPECIALIZATION AND DYNAMICALLY SPECIALIZED EXECUTION (DYSE)

This chapter discusses the background of hardware specialization and proposes the Dynamically Specialized Execution (DySE) model. Section 2.1 discusses different execution models and classifies the common specialization approaches based on programmability and granularity. It then investigates a traditional out-of-order (OOO) superscalar processor to understand how specialized hardware, with the above differences, can save power and increase the energy efficiency of an OOO processor pipeline. Through the above observation, Section 2.2 develops the DySE model as an alternative execution model based on decoupled access/execute and two supporting architectures, Dynamically Specialized Execution Resources (DySER) and Memory Access Dataflow (MAD). Section 2.3 then describes how to program for DySE and discusses the efforts in automating the transformation, from a conventional program to the codes and configurations that can be executed with DySE supporting architectures.

# 2.1 Hardware Specialization, Background and Examples

Today, the general propose processor design is dominated by Von Neumann superscalar processors. The idea of hardware specialization, however, is used extensively to support the general propose processors in improving performance, reducing power, or both. From a hardware viewpoint, these specializations can be characterized in two axises:

• **Programmability:** Specialized hardware can either be programmable or completely static like Application-Specific Integrated Circuits (ASICs). Among the programmable specializations, they can be pure-dynamic which reads instruction in-flight as superscalar processors do, or are synthesized by compiler or programming techniques before invoking the specialized hardware. Examples of the former include CCA [36], VEAL [31] and PipeRench [54]; the latter includes Field-Programming Gate Array (FPGA) based accelerators, GARP [68] and Chimaera [126]. The trade-off between different programmability is often the power efficiency; more dynamism in hardware in general consumes more power.

Figure 2.1: Hardware Specialization Taxonomy

• **Granularity:** Specialized hardware offloads work from a general purpose processor; the specialization granularity depends on the effective instructions in the work they offload. A fine-grain specialized example is Micro-Op Fusion, where a few micro-ops are bundled together and be executed in a specialized datapath. In contrast, coarse-grain specialization may effectively offload hundreds of instructions at one time such as in Graphics Processing Units. In this dissertation, *we do not consider an approach that differs from general purpose Von Neumann pipeline but "specializes" arbitrary applications, since they are essentially general purpose.* For instance, dataflow machines like RAW [119], TRIPS [109], and WaveScalar [117] are not considered as hardware specialization approaches.

Figure 2.1 presents the taxonomy of hardware specialization. The leftmost block illustrates Micro-Op fusion, which has the highest programmability. In the execution, the hardware (decoder) dynamically analyses a collection of instructions and produces fused instructions. No static programming or compiling effort is required before using the fused datapath, and the hardware can be used in any program that contains the target instruction sequence. Although their granularity limits the overall benefit, they can be very efficient in implementation and no modification is needed in the software stack.

Figure 2.2: Hardware specialization execution model

Instruction set architecture extension specialization is illustrated at the next column; the examples are multimedia SSE [4] ISA extensions and cryptographic hardware accelerators [3, 1, 111]. In these cases, the specialized hardware are not programmable and executes pre-defined instruction extensions. Compiler or programming model changes have to be made in order to leverage the specialized hardware.

At the far right, FPGA and ASIC based accelerators [86, 23, 123] have the coarsest granularity and can offload a large code region or the entire application in hardware. The trade-offs here are the communication overhead, custom memory/storage design and software changes. Compared to ASICs, FPGAs are more programmable but less power efficient in hardware microarchitecture.

# 2.1.1 Employing Specialized Hardware in Different Execution Models

Orthogonal to the granularity and programmability, specialized hardwares are often integrated in a general purpose system with some alternation in the original execution model. Figure 2.2 compares a general purpose execution model and specialized execution models:

- Model (a), General Purpose Hardware: In the general purpose execution, the pipeline processes instruction streams sequentially through pipeline stages. The instructions are dynamically analyzed and assigned to execution units in the pipeline.

- Model (b), Opaquely Specialized Hardware: The first set of examples of the specialized hardware execution model includes a specialized front-end to analyze the instructions and program the specialized hardware dynamically. The specialized front-end constructs the

specialized region in-flight and controls back-end units for execution. This model matins the homogeneity in the software at the cost of a hardware front-end, which may consume much power when the back-end units are large and difficult to program. Micro-Op fusion and CCA [36] belong to this model.

- Model (c), Transparently Specialized Hardware: The second set of examples relies on the software to generate configurations for the specialized hardware. Analogous to the instructions, the configurations contain the information to control the specialized hardware; previous models differ in the fact that the configurations in this model have little or no abstraction. No dynamic analysis (such as decode, instruction queuing, and reordering) of configurations is needed. During the execution, the host processor sends the configuration bits to set up the specialized hardware before starting the specialized region. This model preserves the capability of targeting different tasks and improves the power efficiency with configuration cost and compiler/programming changes. Chimaera [126] and DySE [57, 59] belongs to this model.

- Model (d), Statically Specialized Hardware: In the specialized execution model, a region in the instruction stream is offloaded onto the specialized hardware. Static hardware specialization like ISA extension specialization utilizes integrated instructions to offload the work from the host. These specialized instructions invoke pre-defined (before silicon) functions in the specialized unit that is not programmable. Compared to other approaches, this model is not opaquely specialized because programmer have to invoke them explicitly; but it is also not fully transparent in terms of the programmability. By sacrificing the programmability, statically specialized hardware offers the best power efficiency.

# 2.1.2 Improving Efficiency with Specialized Hardware

With a modified execution model, the host general purpose hardware can exploit specialized hardware to reduce overheads. Figure 2.3 is a block diagram of a hypothetical general purpose out-of-order pipeline. It resembles state-of-the-art out-of-order processor pipeline designs such

as Intel's Haswell [66]. Logically, this general purpose pipeline has six stages: *Fetch*, *Decode and Dispatch*, *Issue*, *Execute*, *Memory*, and *Write-back* stages. <sup>1</sup> In particular:

- Fetch: The fetch stage is guided by the program counter and branch predictor to fetch instructions from the instruction cache. Often, an entire cache line is read from the instruction cache to lower the memory access overhead; buffers are used to hold these instructions temporarily. The fetch logic then selects the desired instructions following the program order and delivers them to the next stage. Because the fetch width (i.e. the number of instructions that fetch stage delivers) may not perfectly match the number of instructions in a cache line, dynamic scheduling of instruction access, buffering, ordering and selection are needed. While opaquely specialized hardware (model (b)) can hardly specialize this stage , static specialized hardware and transparent specialized hardware (model (c) and (d)) reduce this dynamic scheduling by fusing the instructions.

- Decode and Dispatch: The decode and dispatch stage decodes the instruction, buffers them in the instruction queue, searches for available resources that could execute the instruction, and allocates entries in the scheduler in the next (issue) stage. This stage also resolves the register structural hazards by register renaming, which dynamically assign a local register to an entry in the physical register file. The scheduling, buffering, and the size of the physical register file determines the length of the instruction window of this pipeline. Specialized hardware units usually have dedicated resources such as execution units and datapaths; even with shared resources, the specialized execution model can reduce the overhead of general purpose dynamic scheduling in many cases. For instance, the SIMD accelerators may read data values from a shared register file; compared with a general purpose processor, they can still reduce the overhead of scheduling because now only a single SIMD instruction is needed for scheduling multiple computation operations.

- **Issue:** The issue stage selects the instructions to drive the execution unit, tracks the execution status, and wakes-up the dependent instructions in the decode and dispatch stages for resource allocation. A scheduler (variant designs could be called issue queue,

<sup>&</sup>lt;sup>1</sup>Each stage may be physically pipelined internally.

Figure 2.3: An out-of-order general purpose processor pipeline

reservation station, etc.) in this stage uses CAMs to match and wake up instructions and operands, uses arbiters to drive execution units, and uses buses to broadcast and distribute data. In addition, a reorder buffer (ROB) is accessed in parallel to hold the instructions in flight and maintain the program order. In the case of mis-speculation, exceptions and traps, a precise state can be restored by inspecting the ROB and flushing/re-executing the correct instructions. In static specialized hardware and transparent specialized hardware (model (c) and (d)) the operator scheduling is determined before execution by a dedicated datapath or configuration bits. In opaquely specialized hardware (model (a)), the specialized scheduler may have to cooperate with the general purpose scheduler in this stage.

- Execute: The execution stage comprises execution units (operators), datapath for operators, and bypass logic. Common execution units may include: integer and floating-point arithmetic units (ALUs), address generation units, multipliers and divider(s). When dependent instructions are scheduled in consecutive cycles, the data value can be forwarded through the bypass logic. In practice, the complexity of bypass logic scales quadratically with the number of execution units [69]. Specialized hardware units can significantly reduce the complexity in the bypass logic with a pre-determined static datapath. In addition, they may combine the bypass logic and execution units into fused execution units, thus enable circuit level optimization.

- Memory: The memory stage accesses the data cache and brings the operands into registers.

Figure 2.4: Power breakdown of 2 and 4-issue out-of-order processor pipeline, modeling Intel Silvermont and Sandy Bridge

It buffers the memory load and stores, performs memory disambiguation, and tracks the miss state by Miss Status Holding Registers (MSHR). Sophisticated mechanisms have been developed to tolerate memory latency [74, 27, 121] and reduce the complexity of the memory buffers [116] in a general purpose pipeline. Regarding specialized hardware, finegrained proposals utilize the well-developed general purpose pipeline to deliver data from the cache. Coarse-grained proposals could use specialized memory [90, 30], registers [108], or scratch pad memory [67, 40] to reduce the dynamism in this stage. However, changing the memory system is intrusive and often demands a different programming model.

• Write-back: The write-back stage writes the resulting data values from the execute and memory stages back to the register file. Also, the ROB commits and retires instructions in this stage if it is safe. Specialized hardware without a centralized register file may lower the switching activity of accessing the multi-ported SRAMs.

Figure 2.4 quantifies the power consumed in each stage of an efficient 2-issue and a 4-issue out-of-order core, which models Intel's Silvermont and Sandy Bridge respectively [7, 5]. The figure reports the power from the execution of data parallel workloads; the experimental setup, and details of workloads and models can be found in Chapter 6. Here, this result presents a first-order observation–even with a power efficient out-of-order core, one-third of the overall power still goes to the front-end, register and bypass logic of the pipeline, where this power is *not* used for computation or accessing memory. In a high-performance core, the design is

even unbalanced, and the power-hungry out-of-order structures consume over 50% of the total power.

# 2.2 Dynamically Specialized Execution

The Dynamically Specialized Execution model, as shown in the third column in Figure 2.1, leverages reconfigurable hardware to provide programmability with coarse granularity. It adopts the reconfigurable specialized hardware execution model such that the application phases are compiled/programmed into configurations and sent to specialized hardware before executing the phase. These phases communicate with each other through memory. Overall, the execution proceeds in three phases: (1) host processor executes non-specialized phase; (2) host processor configures the specialized hardware into a specialized phase; and (3) host processor invokes specialized hardware to execute the specialized application phase. To understand the execution inside a specialized phase, we first revisit the Decoupled Access/Execute model first proposed in ISCA1982 [112].

#### 2.2.1 Inside Specialized Application Phase: Decoupled Access/Execute

The Decoupled Access/Execute model (DAE) [112] was proposed to efficiently issue the instructions that are designated for access and execute. It hides the delay of the memory communication by decoupling these responsibilities. Figure 2.5 presents the basic concept of the DAE model with an example of specialized execution. Beginning from the left, an arrow represents the non-specialized execution of an application, and a purple box shows the application phase to be specialized <sup>2</sup>. When reaching the specialized application phase, the execution splits into two arrows, which represents the two decoupled components, the access component and the execute component. The access component is composed of loads, stores, and address calculations; the execute component is the computation— a + b in this example. The two decoupled components can be executed independently and communicate asynchronously; as a result, a pipeline is formed between the access and execute components. The access component loads data values

<sup>&</sup>lt;sup>2</sup>Originally, the DAE proposal exploits two instruction streams for general purpose execution; there is no transformation between non-specialized to specialized execution

Figure 2.5: Decoupled Access/Execute

by iteration, and sends them to the execute component for computation. Originally, DAE was proposed to tolerate the memory access latency with such a decoupled pipeline (at that time, there was no cache).

The DAE model resembles the data streaming model [15, 20] when the access component works on subsequent items that can be modeled in data streams; however, they differ in the fact that DAE's access component can perform random memory access and trigger a different parts of the execute component. Figure 2.6a presents the original design of the DAE microarchitecture. Two processors, the Execute processor (E-processor) and the Access processor (A-processor), executes two different instruction streams, where the two processors communicate through data (AEQ, EAQ) and control (BranchQ) queues. The A-processor is responsible for issuing the memory reads and writes in the access component, and the E-processor is responsible for computing with the operands sent from the A-processor. In addition, the A-processor could send control signals through branch queue to drive the E-processor to a different branch when it completed the computation. Overall, DAE physically provides two decoupled microarchitectures to execute the decoupled instruction stream, thus allowing the two components to be optimized separately. It contrasts with pre-fetching schemes [74, 27, 121] apropos of the modification (decoupling) in the main instruction stream <sup>3</sup>.

While originally the DAE model was proposed to mitigate the memory latency, this transformation concept influences superscalar processors [73] as well as many specialization pro-

<sup>&</sup>lt;sup>3</sup>Recent pre-fetch proposals often leverage spare cycles to pre-load the data into cache non-bindingly (the data may not be used), where DAE explicitly alters the instruction stream and decouples it into two components that are performed in different hardware units.

Figure 2.6: Decoupled Access/Execute: microarchitecture

posals [118, 92, 11]. Figure 2.6b describes a common DAE paradigm: an accelerator integrated into host processor, where the accelerator replaces the execute processor, and the host processor becomes the A-processor. This paradigm is widely used in various specialization proposals; if the accelerator is reconfigurable and fits in the Reconfigurable Specialized Hardware execution model (as described in Section 2.1.1), the host processor and accelerator can be viewed as using the DySE model as well. The profitability of DAE in the specialized phase (or the DySE model) largely depends on two characteristics: (1) the construction of a specialized phase, and (2) the phase behavior. In a prior work on DySE, "Energy Efficient Computing Through Compiler Assisted Dynamic Specialization" [58], Govindaraju conducted a series of analyses on the compiler assisted DySE to understand the effectiveness of such a model. The two major findings were:

- Across a wide variety of benchmarks, it is observed that the application phases of enough computation instructions (execute component) can be identified for specialization; and

- Most applications re-invoke the same phase multiple times before switching to another.

From the above, with efficient specialized hardware for execute and access components, the DySE model can be applied to a general purpose application and provide performance and energy efficiency on specific phases.

## 2.2.2 Supporting Architecture for Execute: DySER

To fully exploit the benefits of decoupled access/execute, two supporting architectures are conceived for each component. For the execute component, the hardware should address the

following design goals:

- It should be able to efficiently perform many computation operations, with some local branches but no memory loads or stores;

- It should be able to be programmed for different application phases; and

- It should be able to be interfaced with the access component, and be flexible or agnostic to the hardware implementation of the access component;

Dynamically Specialized Execution Resources (DySER, Chapter 3) is conceived to address the above design goals. First, DySER provides heterogeneous functional units for the primitive operators in an application phase. Between these function units, DySER leverages a circuitswitched mesh-like reconfigurable network to create datapaths. Although a packet-switched network allows dynamic resource allocation for data segments, it introduces more hardware overhead in decoding and forwarding data; DySER takes a radical approach that assigns every operation in an application phase to a dedicated functional unit, thus providing an opportunity to enable the circuited-switched network. In the network, dataflow is data-independent and follows a pre-configured datapath that is used many times before reconfiguration. This reuse avoids power-hungry structures like packet switching routers, centralized register files, and crossbars.

Second, while it is possible to create a common case array of frequently used functional units [57] for a phase, they have to be efficiently programmed for phases with different sizes. As a result, DySER utilizes the existing datapath to construct parallel configuration routes to the switches and functional units. The configuration of DySER is virtualized such that a phase with more primitive operations than available functional units can still be mapped to DySER.

Third, the configuration and data is delivered through a queue-based interface; DySER does not require any special front-end and all the control and data computation is driven by the readiness of the data in these queues. Via instructions extensions, host processor can send configuration to DySER, and the access hardware can also use exactly the same interface to send data and control. The primitive interface instructions are: (1) dyserload and dyserstore,

which loads data from memory to DySER and stores data from DySER output to memory; (2) dyserinit, which initializes DySER by sending the configuration bits.

## 2.2.3 Supporting Architecture for Access: MAD

Intuitively, one can use the host processor to drive DySER through the queue-based interface; in fact, many specialization proposals use a host processor and ISA extensions to control the accelerator and deliver data. In such a paradigm, the host processor is often one of the following:

- **Out-of-Order Processor:** In single-thread performance sensitive platforms, out-of-order (OOO) processors are often used as the host. However, because the dataflow between cache and accelerator in an application phase is usually dominated by a few access patterns, using an OOO processor becomes a less-desirable option. OOO's general purpose structures are power-hungry and tend to be an over-provisioned design for driving accelerators (as described in 2.1.2).

- In-order Processor: In-order processors are widely used in power critical platforms such as embedded systems. Some power-oriented specialization proposals [122] assume an in-order baseline so that the overall system offers best power efficiency. For other accelerators, an in-order integration may result in mediocre speedup even compared to a general purpose OOO processor. Figure 2.7 illustrates this issue with two different accelerators: DySER [57] and SSE [4] (details of the configuration and accelerator setting can be found in Chapter 6). The accelerators are modeled in the gem5 cycle-accurate simulator and executes the accelerated phases (kernels) of a mix of Parboil [6], Rodinia [25], and Throughput Kernel [110] Benchmarks. Compared to a 2-issue out-of-order with an accelerator, improvements from acceleration are severely reduced when using the in-order processor; this demonstrates that high-performance OOO processing capability is necessary for some accelerators. Our evaluation in Chapter 7 discusses the use of access component hardware with different performance in more depth.

- **In-order VLIW Processor:** One feasible approach of using in-order or low complexity processor to achieve high performance is the Very Long Instruction Word (VLIW) processors.

Figure 2.7: Performance of 2-issue OOO vs. 1-issue in-order with accelerator Speedups normalized to non-accelerated 2-OOO for both bars

VLIW processors rely on the compiler to perform much of the work done in the front-end of the pipeline. The instructions are pre-scheduled and bundled in the compiler, and thus there is no dependence checking, OOO execution, and dynamic scheduling/forwarding within a bundle. Considering a general purpose host, using VLIW is cumbersome because the applications (even without specialization) have to be recompiled over hardware generations; compilers for VLIW processor may be overly complex in order to target general purpose irregular programs and achieve high performance. For our purpose, always assuming a VLIW host for the access component under DySE is unrealistic.

Our goal is to build an in-core data delivery architecture non-intrusively, which can be efficiently reconfigured for application phases, efficiently move data between cache and accelerator, and be non-intrusively integrated with a variety of execute component accelerators. To this end, we propose Memory Access Dataflow (MAD, Chapter 5); MAD translates instructions into a low-level event-driven ISA, and executes the translated events and actions on a reconfigurable dynamic dataflow substrate. By examining the access component, it can be observed that: (1) The program follows few dataflow patterns to compute the address and control behavior; (2) The outcome of these few dataflow patterns creates recurring "events", such as values returning from cache; and (3) Based on these events, the program has a few "actions" to move the data between the accelerator and memory. These findings describe the fact that the access component of a specialized application phase program region is orchestrating a specialized dataflow memory movement for the computation component. An event-action/dataflow hybrid architecture can be the key towards efficient dataflow pattern computation, event triggering and action arbitration.

## 2.2.4 DySE Unprofitable Cases

As previously mentioned, the DySE model specializes profitable application phases–the frequent phases that have enough computation and few memory access patterns. For certain applications, however, they do not have such phases for DySE to specialize. In particular,

- Flat phase profile: For some applications, the phase profile is flat, and there are no prominent "frequent" phases. Specializing phases that are executed only one or two times results in no benefit, and may lower the performance because of the configuration cost.

- Irregular and control-intensive phases: While some applications may have frequent phases that have a reasonable compute to memory access ratio, they could be irregular and control-intensive such that it is not efficient to leverage DySER or MAD. Govindaraju et al. [60] have discovered some specific issues related to control-flow in legacy benchmarks, which limits the overall improvement from the DySE model.

These two cases, while they are not the target of this dissertation, may be solved with software techniques or different hardware designs. Supporting these phases in the DySE model is a planned future improvement.

# 2.3 Manual and Compiler-Assisted DySE

In the DySE model, application phases are transformed into decoupled access and execute components before running on the supporting architectures. Such transformation can be done manually by programming (manual DySE), or by compiler techniques (compiler assisted DySE). The transformation includes two steps: (1) phase analysis, which discovers the profitability of

Figure 2.8: Manual DySE programming

each piece of the code and schedules them on to two different components; and (2) configuration generation, which generates the configuration for the access and execute architecture. The manual DySE transformation works on high-level code and assigns access and execute code manually. The compiler assisted transformation, on the other hand, automatically analyzes the internal representation of the phase and partitions it into access and execute components. This section presents the manual DySE transformation with an example, and discusses how the compiler assisted DySE can achieve the same transformation performance with automatic analysis and optimization techniques.

## 2.3.1 Manual DySE by Example

As a flexible execution model, DySE can leverage different supporting architectures to specialize the application phase. Figure 2.8 shows an example transformation on Matrix-Multiply (mm in the Parboil benchmark suite). For explanation purposes, the access component is performed on

host processor instead of MAD to simplify the configuration generation step. The details of the MAD ISA are introduced with the microarchitecture of the MAD hardware in Chapter 5.

First, Figure 2.8a shows the original non-specialized code of Matrix-Multiply. In the example code, three nested for loops walk through two matrices, A and B, to perform multiplication. Each element in the column of matrix A is first multiplied by one element in the row of matrix B, and then the results are summed together into matrix C. Here, the most frequently executed computations are the multiplications and additions in the inner-most loop. Through observations, a parallel structure of multiplications and additions can be discovered, as shown in Figure 2.8b. In this dataflow graph, the loop with induction variable k is unrolled eight times, and the multiplications can be executed in parallel; the results of the multiplication operations are merged by a tree of additions. The extracted graph meets two expectations of an execute component: (1) it has no memory operations and can be turned into pure dataflow; and (2) it is profitable to be specialized because of the operational parallelism within. With the above characteristic, this graph can be mapped onto DySER with scheduling tools that generate configuration; the scheduling tool incorporates DySER's physical hardware layout for routing and functional unit assignment.

The graph extraction and transformation has been explored in the literature; Program Dependence Graph (PDG) [48] can be used to describe the graph and its transformations in formal. In a prior work, Govindaraju et al. [60] developed Decoupled Access/Execute Program Dependence Graph (AEPDG) for compiler assisted DySE transformations. In this dissertation, the extracted execute component graph is referred to as Execute-PDG, and the access component graph is referred to as Access-PDG.

After the execute component is extracted, the rest of the code is merely preparing the memory addresses and accessing cache. The access component can be constructed by the following memory access codes and interface instructions. Figure 2.8c shows the access component of Matrix-Multiply in stylized C-style codes. In the access codes, the two outer loops remain unchanged, and the inner loop is replaced with a series of interface instructions (as stylized function calls) and an aggregation of the results. In the example, two interface instructions are used: a parallel dyserloadPD and dyserrecy. The former is the parallel variant of the primitive

dyserload, which loads eight elements from a cacheline, and the latter is a register variant of dyserstore, which retrieves a data value from the execute component (on DySER) to a register. The argument of the interface instructions are (1) register or memory address, and (2) a DySER port. The DySER port number represents an input of the execute component dataflow graph, and is physically routed to an input of the functional units (in this case, a multiplier).

#### 2.3.2 Hardware Mechanisms to DySE

As many other specialization proposals, it is possible to completely offload the burden of identifying the profitable DySE phases to the hardware. Using the opaquely specialized hardware execution model (Section 2.1.1), we can build a front-ending for DySER to construct DySER configurations at run-time. Building such a front-end configuration engine, however, requires careful design such that this specialized front-end does not consume too much power when generating phase information and configuration. Two fundamental tasks have to be performed in the hardware in such case:

- **Phase identification:** Trace cache [105, 49] or the mechanisms in instruction reuse design [114] can be used for caching and analyzing the dynamic instruction from the host processor and create profitable phases.

- **Configuration generation:** Hardware supported binary translation or virtual machine [113] can be used for this purpose. In terms of the two supporting architecture in DySE, the DySER and MAD configuration may be generated with a greedy hardware translator that maps instructions to the functional units, switches, events or actions in their architecture.

CCA [36] and Chimaera [126] are two examples that leverage a specialized front-end to generate the configuration in hardware. In this dissertation, we do not use this approach mainly because of the overheads in power consumption.

#### 2.3.3 Compiler-Assisted DySE

Many efforts have been made to automate the DySE transformation. Although the design and implementation of compiler assisted DySE transformation are not the focus of this dissertation <sup>4</sup>, in this section we summarize the qualitative and quantitative findings from the implementation work, which includes the DySER Compiler published in PACT2013 [60], a spatial scheduler in PLDI2013 [95], and Govindaraju's dissertation [58].

**Breaking SIMD shackles:** Govindaraju et al. proposed a variant of Program Dependence Graph [48], called Access Execute Program Dependence Graph (AEPDG) to enable the compilation for DySER [60, 58]. The AEPDG is a PDG that is partitioned into two components: the access PDG and the execute PDG. After the front-end compilation, the compiler generates the control-flow graph (CFG) with standard scalar optimizations (Constant propagation, Loop Invariant Code Motion, and so forth.). Next, the compiler generates AEPDG from CFG and performs the DySE optimizations. These optimizations include: loop unrolling for PDG Cloning, strip mining for vector deepening, subgraph matching, execute PDG splitting, scheduling execute PDGs, unrolling for loop dependence, traditional loop vectorization, and load/store coalescing. Equipped with these optimizations, the compiler schedules the Execute-PDG onto DySER and inserts DySER interface instructions to the Access-PDG for the host processor.

The authors built a LLVM based compiler and compare the performance of the compiler (accelerated by DySER) with manually optimized programs and Intel's ICC (which generates SSE/AVX codes). With the flexibility in the DySE model, the compiler can employ many more optimizations and create significant parallelism for the underlying specialized hardware (DySER) than a conventional SIMD compiler. Overall, the compiler achieves a 1.8X speedup on DySER over conventional SIMD vectorization in simulation, and the compiler's performance is close to the ideal manually optimized code.

**Spatial Scheduling for DySER:** The DySER scheduling of the execute component, which is a graph mapping and spatial scheduling program, can be done in various ways from naive greedy

<sup>&</sup>lt;sup>4</sup>All evaluations in other sections use manual transformation

algorithms [57] to more sophisticated approaches. Nowatzki et al. [95] proposed a general scheduling framework based on integer linear programming that solves this spatial scheduling problem on DySER and other spatial architectures. In the DySE-specific analysis, this ILP-based scheduler outperforms both the automated greedy approach and manual transformation by 36% and 2% in latency, respectively. It also improves overall performance and throughput in many cases.

# 2.4 Chapter Summary

In order to enable an efficient specialization, the execution must be freed from the original execution model; otherwise, any optimization is highly restricted so that only minor performance or power efficiency gains can be achieved over the general purpose processor. This chapter discussed the Dynamically Specialized Execution (DySE) model based on a discussion of hardware specialization. It developed DySE's application phase specialization, decoupled access/execute, and introduced the supporting architectures. It then presented the Matrix-Multiply as an example of manual DySE programming. Last, it summarized the work in automating the DySE code generation from a traditional program.

In summary, the DySE model is a specialized execution model that modularly enables different supporting architectures. The flexibility in the model and interface heavily reduces the design complexity of the design and integration of the supporting architectures, as well as the compiler optimizations.

#### 3 DYNAMICALLY SPECIALIZED EXECUTION RESOURCES (DYSER)

The DySE execution model and transformation elaborated in Chapter 2 decouples an application phase into access and execute components, where the execute components are mapped onto the specialized hardware, DySER. Regrading power, DySER leverages static dataflow execution on a circuit-switched network to eliminate the excess dynamism in a superscalar out-of-order processor. This static dataflow, moreover, is dynamically reconfigurable between different application phases. The DySER network thus can efficiently offer operation and data level parallelism for performance with the functional units inside. This chapter discusses the hardware mechanisms that deliver performance, power efficiency, and programmability. It first outlines the design goals of DySER (Section 3.1) and gives an overview of the architecture of DySER. Next, it describes the internal microarchitecture of DySER (Section 3.2) and how to configure them with an efficient mechanism (Section 3.3). Third, Section 3.4 discusses the integration interface of DySER, and how DySER supports data level parallelism. Last, Section 3.5 summarizes this chapter.

# 3.1 DySER Design Goals and Overview

Dynamically Specialized Execution Resources (DySER) is proposed to perform the execute component in the DySE model. It executes the computations in a frequent application phase, represented by program dependence graphs (PDG) [48]. DySER supports the extracted execute component graph, Execute-PDG (described in Section 2.3.1), with an efficient fabric of functional units and a switch network. Specifically, DySER has several design goals:

- First, the microarchitecture of this fabric should eliminate the dynamic overheads of a general purpose processor, provided that a scheduled configuration is executed statically; during execution, DySER should exploit the pipeline and instruction (operation) level parallelism for similar or better performance as OOO processors;

- Second, DySE decouples the execute component of a specialized phase as a program dependence graph, which may have control-flow, and should efficiently support the

Figure 3.1: Dynamically Specialized Execution Resources (DySER)

control-flow within a phase;

- Third, DySER should be programmable to map different application phases;

- Forth, DySER should flexibly support large and small regions with hardware/software mechanisms;

- Fifth, the integration of DySER and the host processor should be flexible and non-intrusive, given the interface defined by the DySE model, and DySER should exploit the data level parallelism in the hardware for speedup over OOO.

These goals define the design of DySER; generally speaking, DySER leverages a reconfigurable circuit-switched network to remove the overhead of dynamic scheduling (goal 1). This network constructs routes that connect many functional units that can be activated in parallel for high performance (goal 2). Inside the network, DySER supports control flow with its functional units and the meta-bits (goal 3) and supports efficient configuration with the existing datapath in the network (goal 4). DySER is designed as a long latency, multi-ported execution unit that can be intuitively interfaced with queues and interface instructions (goal 5).

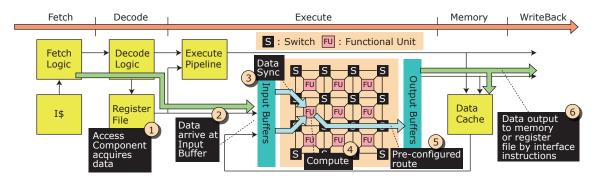

Figure 3.1 illustrates an overview of DySER. To simplify the explanation, the access component is performed on a host superscalar without specialization; DySER, in this case, logically resides in the execute stage. First in step 1, the access component executes interface instructions to load data from memory or the register file to DySER. In step 2, the data arrives at input buffers of DySER, where a hand-shake flow control protocol is implemented to notify the interconnect network in DySER to consume data. Next in step 3, through the protocol, the data

Figure 3.2: DySER microarchitecture: the network of switches and functional Units

move between switches along the preconfigured route, and they then arrive at the input of a functional unit. The data is buffered here until all inputs of this functional unit arrive; the inputs are then consumed by the functional units for computation (step 4). The result, following the preconfigured routes and passing the posterior switches and functional units, finally reaches the output buffers (step 5). Lastly, the access component executes another interface instruction to retrieve the result and move it to memory or its register.

Three major tasks in this figure are explained in the next few sections: (1) internal microarchitecture of the DySER network, which satisfies the goals 1 to 3 by design; (2) the configuration of this network, which satisfies the 4th goal with the reuse of DySER's internal microarchitecture; and (3) the integration of DySER, which fulfills the last goal via a non-intrusive interface.

# 3.2 **DySER Internal Microarchitecture**

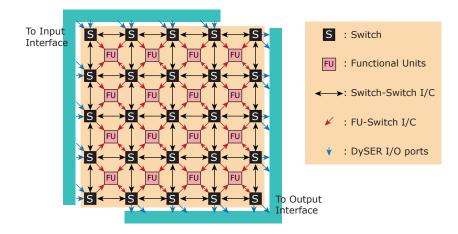

DySER satisfies the first goal with a network of switches and functional units that can map a program dependence graph and execute it statically; this network, after configuration, does not dynamically analyze input data as a packet, but performs static dataflow execution on pre-configured routes. Figure 3.2 presents the network topology of a 4x4 DySER, which has 4x4 functional units and 5x5 switches. For the simplicity of explanation, all the functional units have two inputs and one output. The DySER network is a mesh network composed by switches (the black boxes with "S"), where the network is augmented with functional units in the "hole"

Figure 3.3: DySER microarchitecture: switch

of the mesh (Red boxes and arrows). Compared to the FPGA-like network, DySER has smaller fanins and fanouts at each switch and functional unit; this is because an FPGA tile tends to have many more input and output signals than a node (i.e., an operation, which often has few input/output data values) in DySER. At the edge of the mesh network, input and output ports of the switches are connected to DySER's input and output interface. These ports are exposed to the software such that a programmer or a compiler can write a DySE application phase that leverages the ports to send/receive data. For a 4x4 DySER, each side of the network has eight inputs or eight outputs; thus, a total of 16 input ports and 16 output ports can be used.

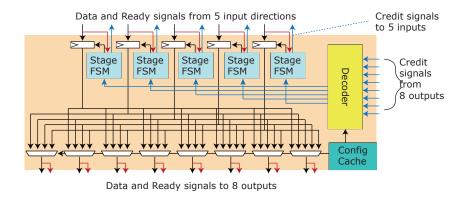

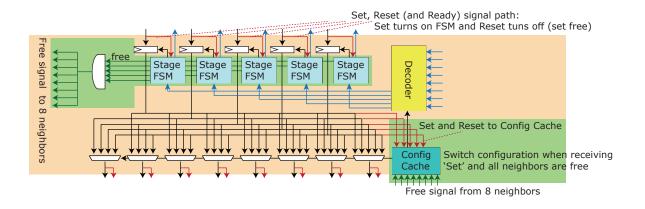

### 3.2.1 DySER Switch

The heart of the network is DySER switches, which route data values to functional units for computation. Figure 3.3 details the microarchitecture of a switch. The building blocks in a switch are multiplexers, flip-flop stages, a decoder and a configuration cache that stores the configuration. A DySER switch has five inputs (north, east, west, south, and northeast) and eight outputs (north, east, west, south, northeast, northwest, southeast, southwest)<sup>1</sup>. Flip-flop stages are used at each input direction to hold the data, and multiplexers are used at each output to select data from these stages. Controlling the flip-flop stages, the finite state machine (Stage FSM) is responsible for the flow-control along the configured routes. DySER implements a credit-base flow-control protocol in the stage FSM with two meta signals, a forward *ready* signal

<sup>&</sup>lt;sup>1</sup> In the case of multi-output function, the switches have to support more inputs from a functional unit.

Figure 3.4: DySER microarchitecture: functional unit

(red arrows) and a backward *credit* signal (blue arrows). After configuration, each stage on the configured route is initialized with a credit. Whenever a stage sees a ready data from the previous stage, it gives its credit to the previous stage and consumes the ready data. The stage is then turned into a zero credit state, until the subsequent stage passes its credit for the ready data. The credit signals, which come from the output (subsequent stages), are decoded and forwarded to the corresponding stage FSM. This handshake protocol enables pipelining and stalling in the network.

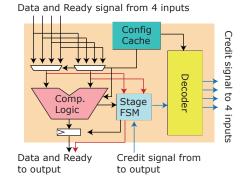

#### 3.2.2 DySER Functional Unit

Figure 3.4 presents the microarchitecture of a functional unit; the logics for supporting control flow is omitted in this figure and deferred to the next subsection. In a functional unit, there is a computation logic selecting input operands via multiplexers from 4 input directions (northeast, northwest, southeast and southwest), and output to the southwest neighbor switch. The stage FSM and flip-flop are also used in functional units; it in addition synchronizes the input data from different directions. The stage FSM in a functional unit controls the computation logic such that it only computes when both two of its operands are ready. When the computation finishes, the stage FSM then gives credit to both of the inputs and latches the result in the flip-flop stage. In the decoupled access/execute model, the inputs from the access component are not always synchronized (i.e., the input of a functional unit may come in at different cycles) and the synchronization inside DySER is necessary. This microarchitecture design has two advantages:

Figure 3.5: DySER microarchitecture: Phi-function

(1) It eliminates the need for a packet-switching router to synchronize the data; and (2) Stage FSM synchronization works with pipelining and stalling, thus the operand scheduling is agnostic to software (i.e., no operand scheduling has to be done by the programmer or compiler).