Topology, Modeling and Analysis of Bridge of Bridge

DC-AC and AC-DC Power Converters

By

Justin Kyle Reed

A dissertation submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

(Electrical Engineering)

at the

#### UNIVERSITY OF WISCONSIN-MADISON

2014

Date of final oral examination: 12/10/14

The dissertation is approved by the following members of the Final Oral Committee: Giri Venkataramanan, Professor, Electrical Engineering Thomas Jahns, Professor, Electrical Engineering Bulent Sarlioglu, Assistant Professor, Electrical Engineering (Adjunct) Yehui Han, Assistant Professor, Electrical Engineering Robert Lorenz, Professor, Mechanical Engineering

© Copyright by Justin Reed 2014

All Rights Reserved

The bridge of bridge converter (BoBC) topology is a recent addition to the family of power converters. Inherently modular and multilevel, the BoBC is also a flexible topology that employs "building blocks" for realizing power conversion throughout an extremely wide range of power, voltage, current and applications. However, its use has so far been extremely limited and its capabilities, limitations and fundamental behavior largely unexplored. This research therefore builds a generalized topological framework for the analysis and design of the BoBC, focusing on dc-ac and ac-dc power conversion. Using this framework, techniques for sizing converter components such as capacitors and switches are developed. Dynamic phasor modeling in dq coordinates suitable for multilevel converters of arbitrary size permits the use of time-invariant visualization and enables the use of the BoBC in high-performance applications such as motor drives. A case study laboratory-scale converter validates the predicted multilevel behavior, and computer simulations confirm model accuracy.

ii

I would like to express my sincere gratitude to a number of people, in my personal, academic, and professional circles, who have helped me throughout my research. First and foremost, I am grateful to my advisor, Prof. Giri Venkataramanan, for providing tremendous levels of support over the years. His mentoring, encouragement and persistence has shaped my own engineering problem-solving approach, as well as my career path. It has been a sincere privilege to study under his direction.

As a student of the power engineering research microcosm that is the Wisconsin Electric Machines and Power Electronics Consortium (WEMPEC), I have benefitted from plentiful others on an almost daily basis. Of course the faculty and sponsors play a crucial role throughout WEMPEC and their impact can't be understated. Friends and colleagues, including Patrick Flannery, Larry Juang, Phil Kollmeyer, James McFarland, Adam Shea, and many, many others, have assisted me in times of need. Perry Channegowda and Calvin Cherry were instrumental in the assembly of the experimental converter, which saved me countless hours and headaches. I would especially like to thank Dan Ludois for his many contributions and distractions, which were always welcomed. Behind the scenes, the WEMPEC support staff, including Helene Demont and Ray Marion, was always more than eager to help, for which I am very thankful.

Several WEMPEC visiting scholars had very specific and valuable contributions to my research. Francisco Martínez from the Technical University of Madrid helped with converter modeling and computer simulation, Prof. Dionisio Ramírez from the Polytechnic University of Madrid visited several times to assist with the experimental converter programming, and Carlos Soriano from the University of Colorado-Denver helped a tremendous amount with hardware assembly and debugging.

I would also like to extend thanks to my coworkers for their assistance. I could not have written this dissertation without them taking on additional responsibilities while I completed this degree.

Lastly I would like to thank my family – especially my wife Alicia – for their continued support and patience. My path has not exactly been a conventional one, and has often posed challenges. But knowing that those closest to you want you to succeed just as much as you do is very powerful. Thank you for helping push me towards the end, and for always having a bit of comic relief at the ready.

To Jasper

May you keep on smiling

vi

| Abstract          | i     |

|-------------------|-------|

| Acknowledgments   | iii   |

| Table of contents |       |

| List of figures   | xiii  |

| List of tables    | xxi   |

| Nomenclature      | xxiii |

| Chapter 1 | Introduction                           | 1  |

|-----------|----------------------------------------|----|

| 1.1       | Overview of dc-ac converter topologies | 1  |

|           | 1.1.1 Classical converter topologies   | 2  |

|           | 1.1.2 Z-source converter               | 3  |

|           | 1.1.3 Bridge of bridge converter       | 4  |

| 1.2       | Objectives                             | 11 |

| 1.3       | Chapter overview                       | 11 |

| Chapter 2 | Bridge of Bridge Topologies                                       | 14  |

|-----------|-------------------------------------------------------------------|-----|

| 2.1       | BoBC building blocks                                              | .14 |

| 2.2       | Evolution of the essential BoBC topological structure             | .17 |

| 2.3       | Q-cell types                                                      | .24 |

|           | 2.3.1 CSEB full bridge                                            | .26 |

|           | 2.3.2 CSEB semi-full bridge                                       | .28 |

|           | 2.3.3 CSEB half bridge                                            | .29 |

|           | 2.3.4 ISEB full bridge                                            | .30 |

|           | 2.3.5 ISEB semi-full bridge                                       | .31 |

|           | 2.3.6 ISEB half bridge                                            | .32 |

|           | 2.3.7 Q-cells for other energy storage types                      | .33 |

|           | 2.3.8 Summary of Q-cell terminal characteristics                  | .33 |

| 2.4       | CSEB vs. ISEB                                                     | .34 |

| 2.5       | Unidirectional vs. bidirectional energy storage                   | .35 |

| 2.6       | Summary                                                           | .36 |

| Chapter 3 | Steady-State Scalar Modeling and Design of Practice               | al  |

| BoBCs     | 38                                                                |     |

| 3.1       | CSEB average circuit model                                        | .39 |

| 3.2       | BoBC Design Using Steady-State Analytical Averaged CSEB Solutions | 41  |

|           | 3.2.1 Preliminary choice of CSEB type                             | .44 |

viii

|           | 3.2.2 Q-cell design: custom or standard                      | 45  |

|-----------|--------------------------------------------------------------|-----|

|           | 3.2.3 Simplified model                                       | 47  |

|           | 3.2.3.1 Bridge capacitor design                              | 50  |

|           | 3.2.3.2 Bridge switch sizing                                 | 56  |

|           | 3.2.1 Improved accuracy model                                | 62  |

| 3.3       | Frequency content of steady-state models                     | 70  |

| 3.4       | Scalar Higher Order Terms Suppression (SHOTS) Control        | 73  |

| 3.5       | Summary                                                      | 76  |

|           |                                                              |     |

| Chapter 4 | Dynamic Phasor Modeling                                      | 79  |

| 4.1       | General phasor circuit modeling                              | 79  |

| 4.2       | Phasor circuit model development                             | 82  |

|           | 4.2.1 Steady state dynamic phasor model solution             | 87  |

|           | 4.2.2 Change of design variables to dynamic phasor variables | 88  |

| 4.3       | Circuit and state block diagrams                             | 88  |

| 4.4       | Small signal dynamic phasor model                            | 90  |

| 4.5       | Simplified state block diagram                               | 94  |

| 4.6       | Dynamic Analysis of Bulk D/Q/DC model                        | 95  |

|           | 4.6.1 Eigenvalue locations                                   | 96  |

| 4.7       | Effect of SHOTS on transfer functions                        | 98  |

| 4.8       | Summary                                                      | 100 |

| Chapter 5 | Mu     | ltilevel Branch Modeling                 | 101 |

|-----------|--------|------------------------------------------|-----|

| 5.1       | Exten  | ding the scalar circuit model            | 101 |

| 5.2       | 2-Seri | 104                                      |     |

|           | 5.2.1  | DQ equivalent circuit                    | 104 |

|           | 5.2.2  | State block diagram                      | 105 |

|           | 5.2.3  | State space model                        | 106 |

|           | 5.2.4  | Steady state solution                    | 111 |

|           | 5.2.5  | Eigenvalue study                         | 112 |

| 5.3       | 3-Seri | es branch ( $n_s=3$ )                    | 113 |

|           | 5.3.1  | DQ equivalent circuit                    | 113 |

|           | 5.3.1  | State block diagram                      | 115 |

|           | 5.3.1  | State space model                        | 115 |

|           | 5.3.2  | Steady state solution                    | 120 |

|           | 5.3.3  | Eigenvalue study                         | 121 |

| 5.4       | Eigen  | value scaling trends                     | 123 |

| 5.5       | Summ   | ary                                      | 127 |

|           |        |                                          |     |

| Chapter 6 | Mo     | del Validation                           | 129 |

| 6.1       | Conve  | erter specifications and representations | 129 |

| 6.2       | Design | n of candidate power converter           | 131 |

|           | 6.2.1  | Calculation of design parameters         | 131 |

|           | 6.2.2  | Capacitor design                         | 133 |

X

|     | 6.2.3  | Switch design                      | 134 |

|-----|--------|------------------------------------|-----|

| 6.3 | Hardy  | ware description                   | 134 |

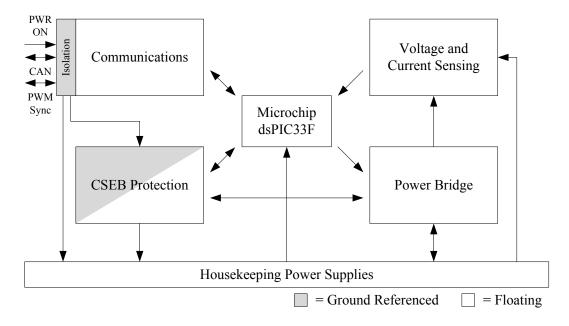

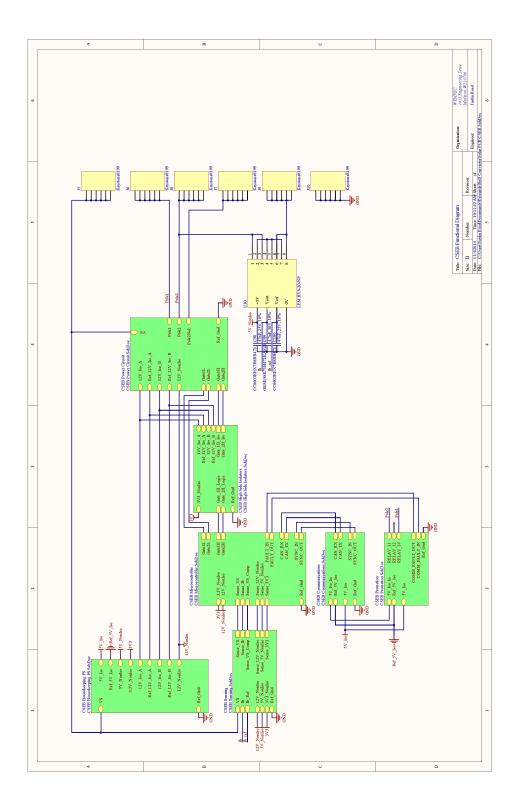

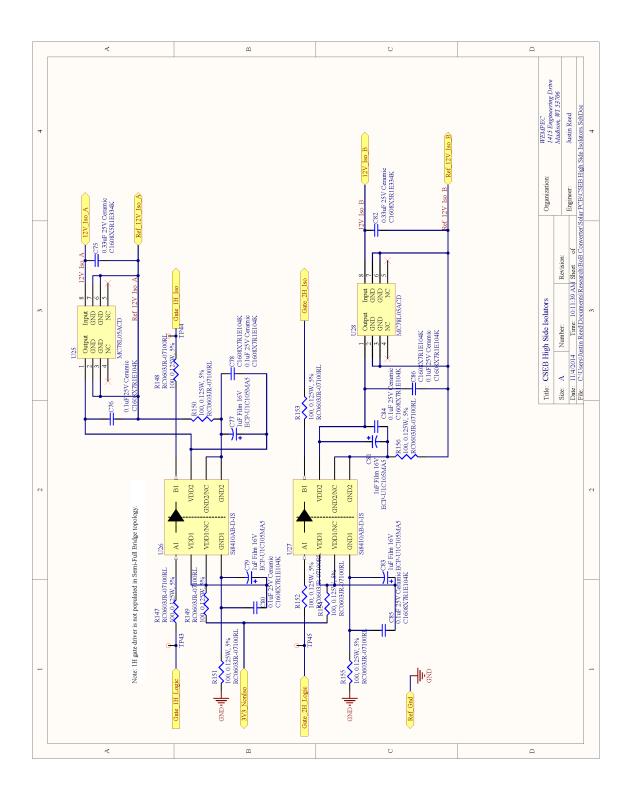

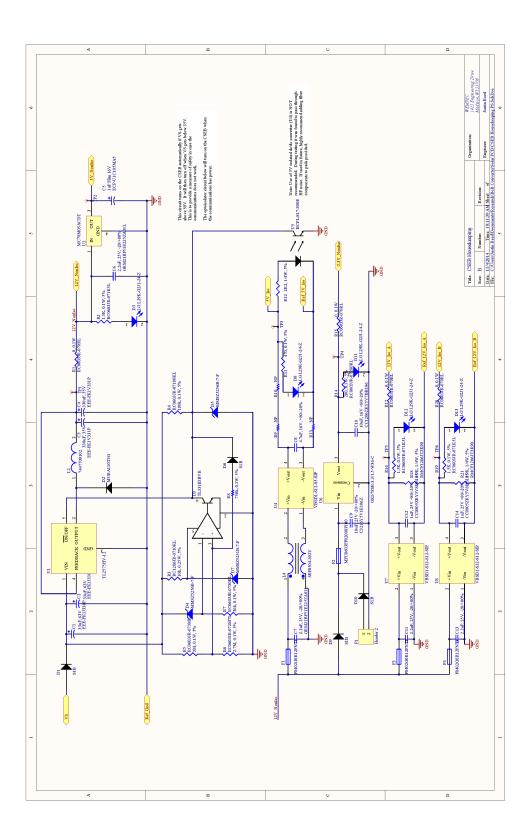

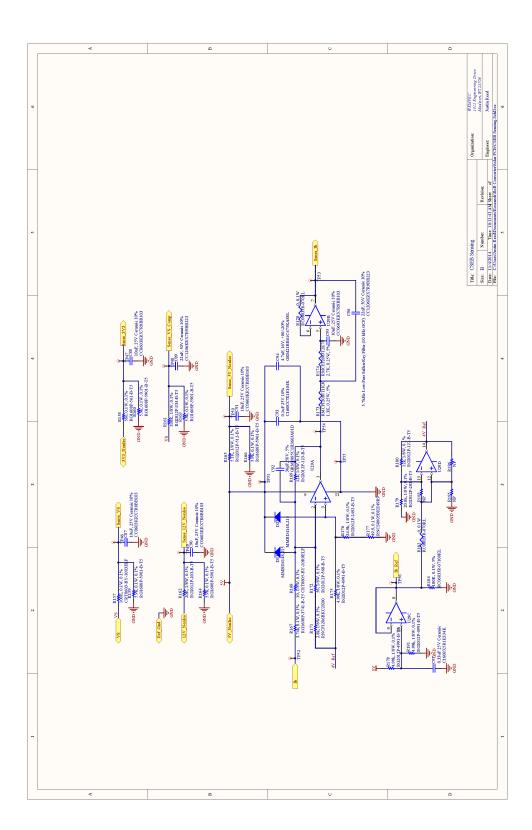

|     | 6.3.1  | CSEB design                        | 135 |

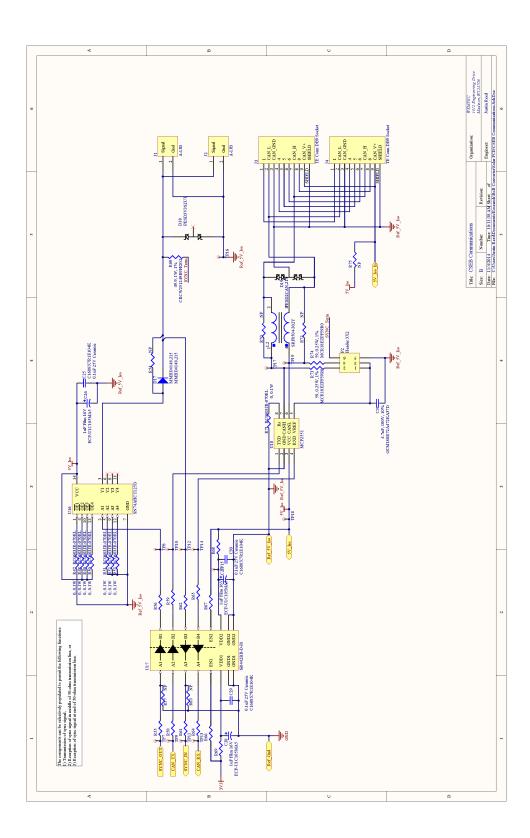

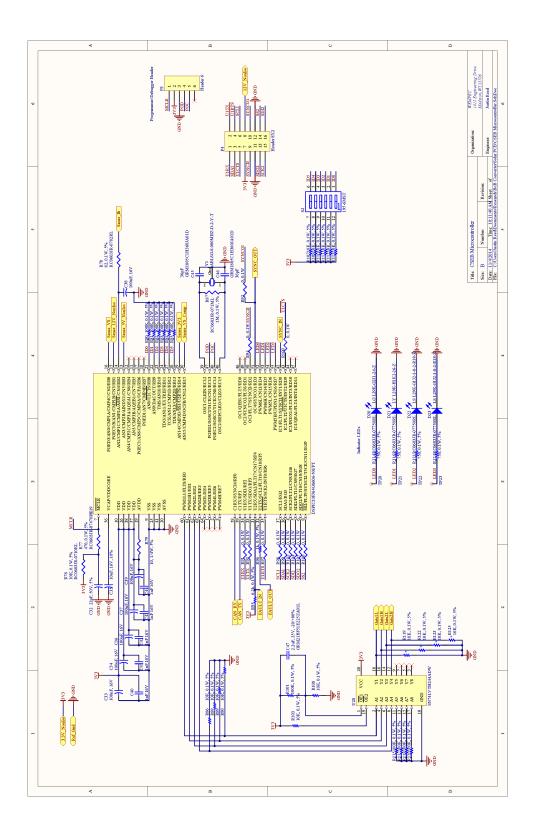

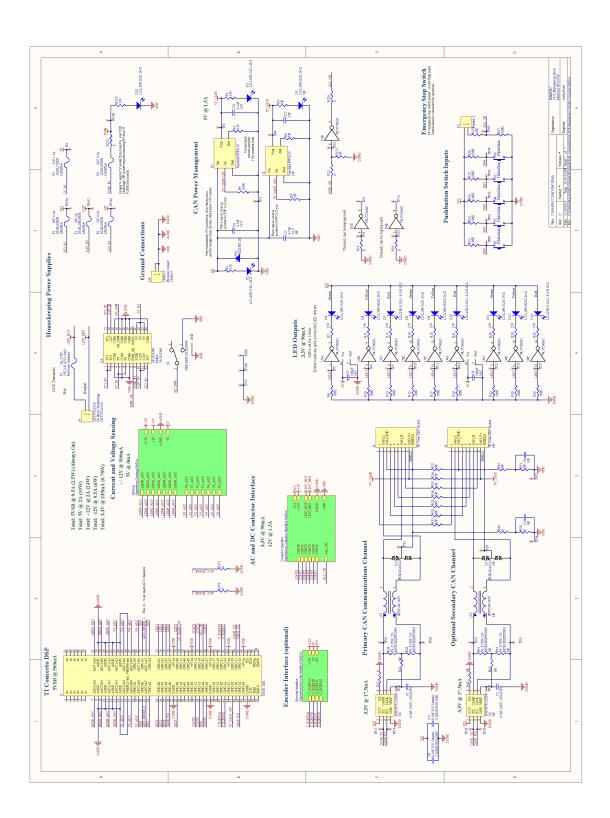

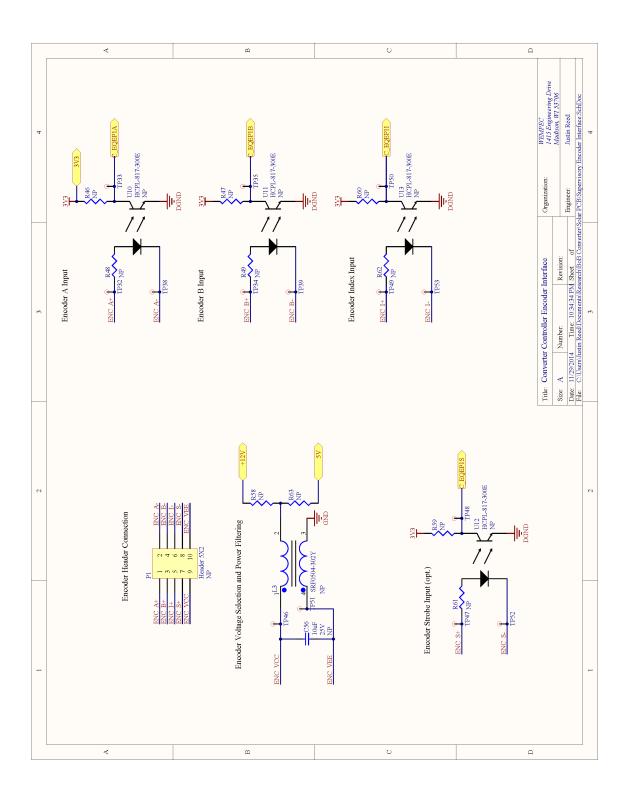

|     | 6.3.2  | Communications Platform            | 137 |

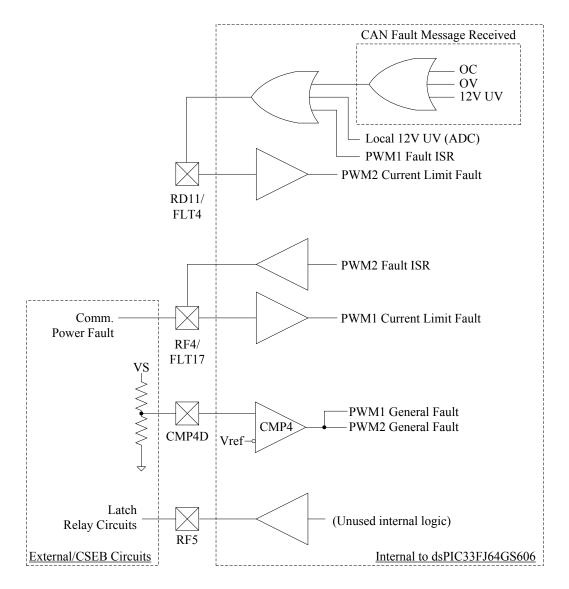

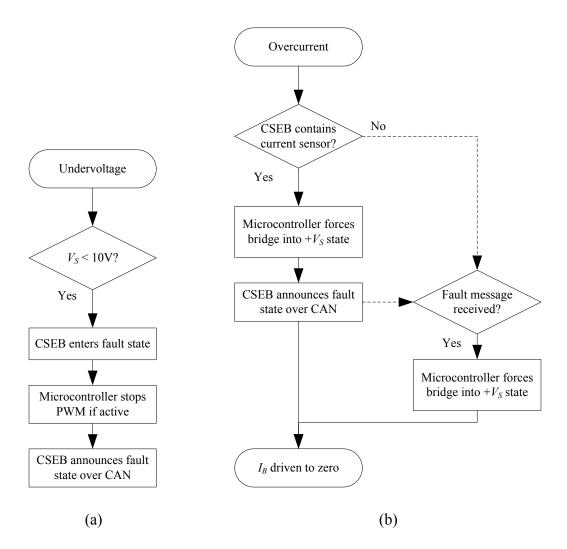

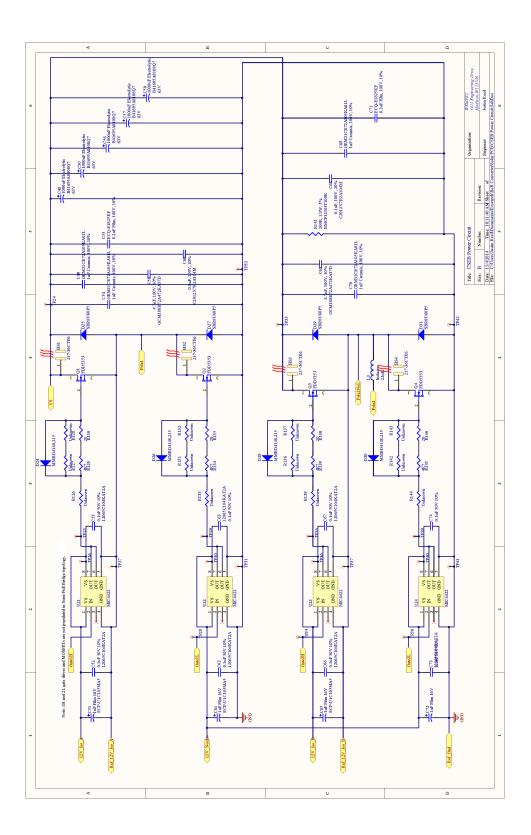

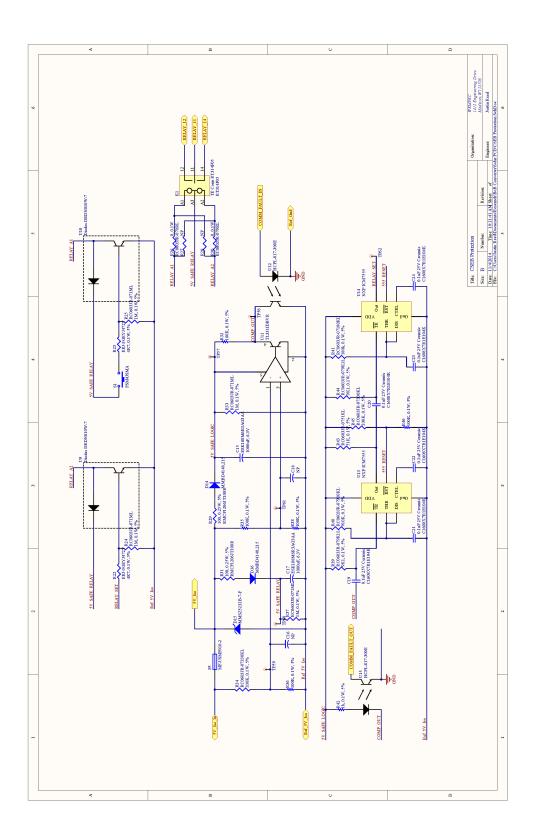

|     | 6.3.3  | CSEB protection                    | 143 |

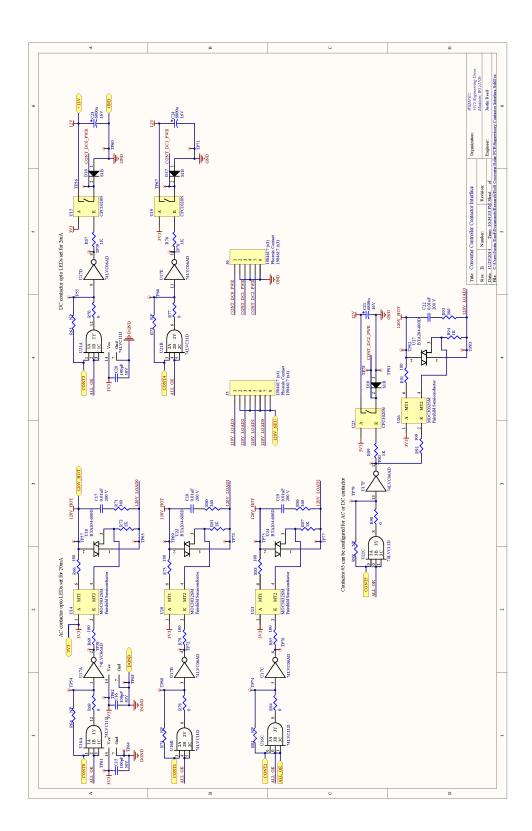

|     | 6.3.1  | Converter hardware structure       | 146 |

|     | 6.3.1  | Converter controller design        | 150 |

| 6.4 | Branc  | ch-level simulation platform       | 153 |

| 6.5 | Verifi | ication of models                  | 156 |

|     | 6.5.1  | Semi-full bridge topology          | 156 |

|     | 6.5.2  | Capacitor sizing                   | 158 |

|     | 6.5.3  | Scalar circuit model               | 164 |

|     | 6.5.4  | Waveforms                          | 165 |

|     | 6.5.5  | Operating point analysis           | 167 |

|     | 6.5.6  | Eigenvalue verification            | 169 |

|     | 6.5.7  | Multilevel eigenvalue verification | 172 |

| 6.6 | Sumn   | nary                               | 175 |

# Chapter 7 Conclusions and Future Work...... 177

| 7.1 | Contributions of this research | 178 |

|-----|--------------------------------|-----|

| 7.2 | Discussion of results          |     |

| 7.3 | Future work                    |     |

| Chapter  | 8 Appendices                      | 186   |

|----------|-----------------------------------|-------|

| А        | RMS Currents for HB CSEB          | . 186 |

| В        | RMS currents for FB and SFB CSEBs | . 191 |

| С        | Simulation initialization script  | . 196 |

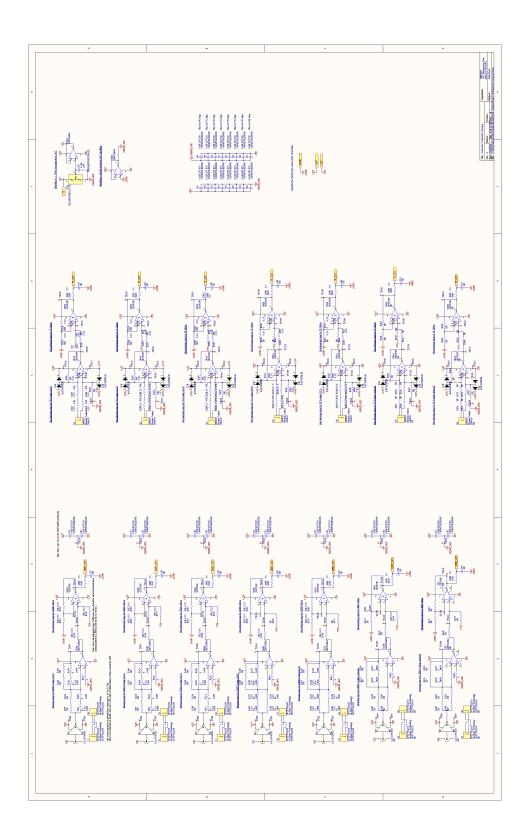

| D        | CSEB Schematics                   | . 197 |

| E        | Converter Controller Schematics   | . 206 |

| Bibliogr | aphy                              | 211   |

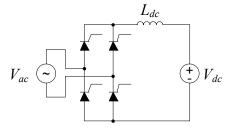

| Fig. 1-1. Current source converter topology for single phase ac-dc power conversion realized with thyristors.                                                               | 3  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

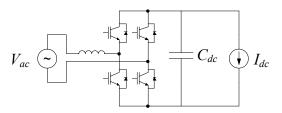

| Fig. 1-2. Voltage source converter topology for single phase ac-dc power conversion realized with IGBTs                                                                     | 3  |

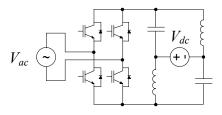

| Fig. 1-3. Z-source converter topology for single phase ac-dc power conversion with current-stiff ac bus.                                                                    | 4  |

| Fig. 1-4. Generalized dc-ac BoBC topology for single phase ac-dc power conversion.                                                                                          | 4  |

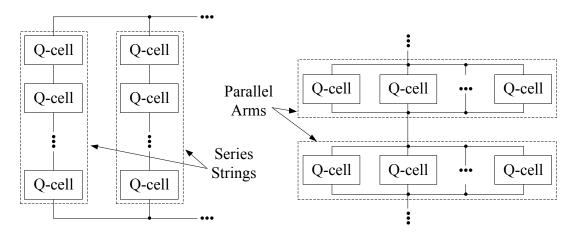

| Fig. 2-1. Example branches consisting of series string and parallel arm configurations of Q-cells for realizing increased voltage blocking and/or current carrying capacity | 15 |

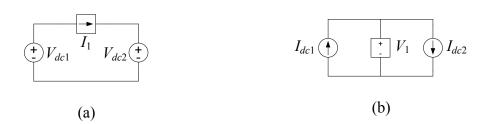

| Fig. 2-2. Primitive Case example A of power flow control using (a) a controllable current source $I_1$ , or (b) a controllable voltage source $V_1$ .                       | 18 |

| Fig. 2-3. Primitive Case example B of power flow control using a controllable current-stiff source $I_1$ .                                                                  | 19 |

| Fig. 2-4. Primitive Case example C of power flow control using a controllable current-stiff source $I_1$ .                                                                  | 19 |

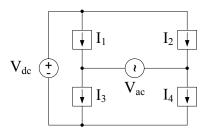

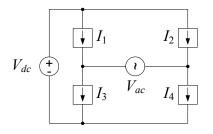

| Fig. 2-5. Case example D with BoBC formed by controllable current-stiff sources $I_1 - I_4$ .                                                                               | 21 |

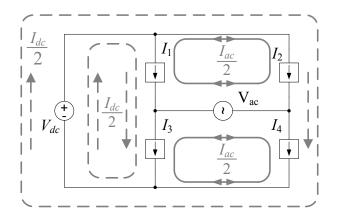

| Fig. 2-6. Current flow in example dc-ac BoBC                                                                                                                                | 22 |

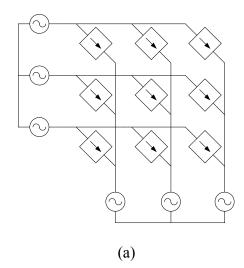

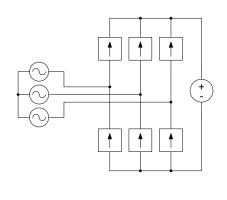

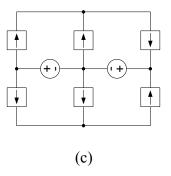

| Fig. 2-7. Several potential BoBC topologies. (a) 3-phase matrix converter,<br>(b) 3-phase ac to dc converter, (c) dc-dc converter with ac<br>link                           | 24 |

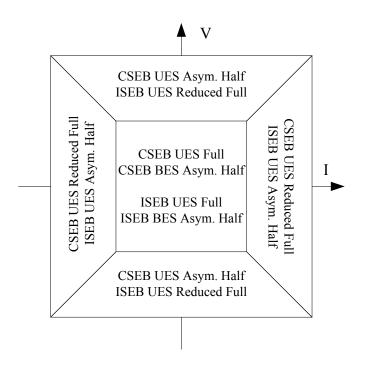

| Fig. 2-8. Bridge terminal voltage and current characteristics of CSEB and ISEB Q-cell types.                                                                                        | 25 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Fig. 2-9. CSEB full bridge circuit with ideal SPDT switches.                                                                                                                        | 26 |

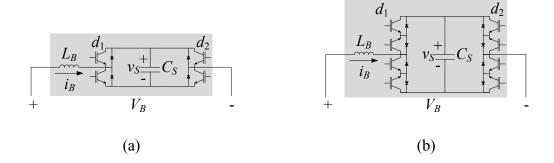

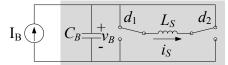

| Fig. 2-10. CSEB full bridge circuit with SPDT switches realized using IGBT switches for (a) UES and (b) BES.                                                                        | 26 |

| Fig. 2-11. An equivalent CSEB full bridge circuit with an alternative SPDT switch realization for BES                                                                               | 27 |

| Fig. 2-12. CSEB semi-full bridge circuit IGBT realization for (a) UES and (b) BES.                                                                                                  | 28 |

| Fig. 2-13. CSEB HB circuit with an ideal SPDT switch.                                                                                                                               | 29 |

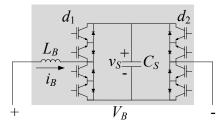

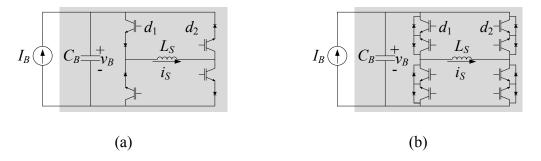

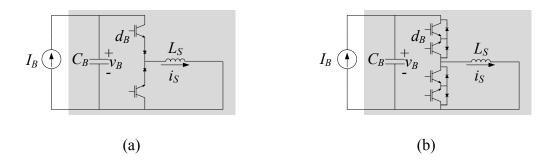

| Fig. 2-14. CSEB HB with IGBT switches for (a) UES, and (b) BES                                                                                                                      | 29 |

| Fig. 2-15. ISEB full bridge circuit with an ideal SPDT switch.                                                                                                                      | 30 |

| Fig. 2-16. ISEB full bridge with IGBT switches for (a) UES, and (b) BES                                                                                                             | 30 |

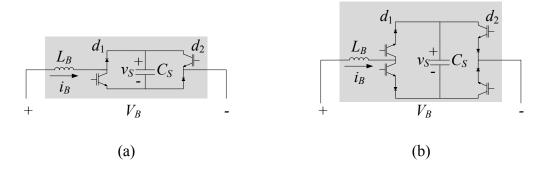

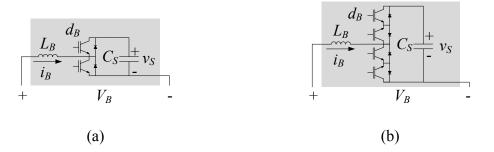

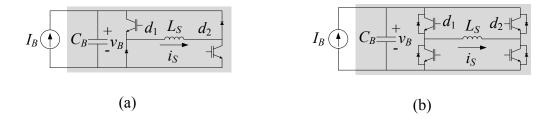

| Fig. 2-17. ISEB SFB circuit IGBT realization for (a) UES and (b) BES                                                                                                                | 31 |

| Fig. 2-18. ISEB HB with ideal SPDT switches.                                                                                                                                        | 32 |

| Fig. 2-19. ISEB half bridge circuit IGBT realization for (a) UES and (b) BES.                                                                                                       | 32 |

| Fig. 2-20. Idealized electromechanical flywheel full bridge using dc machine.                                                                                                       | 33 |

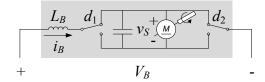

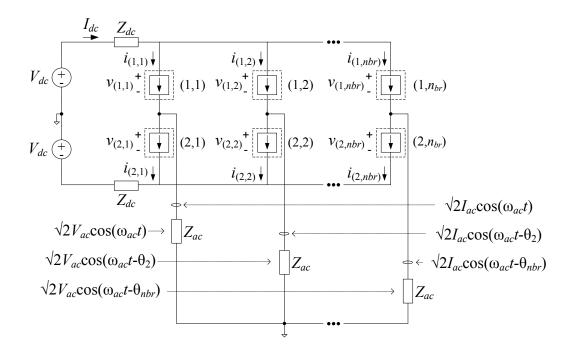

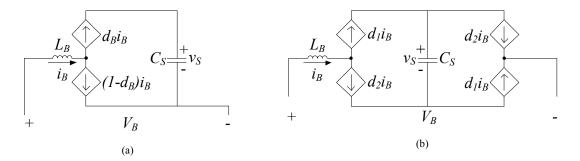

| Fig. 3-1. Averaged CSEB model of (a) one Q-cell and (b) a series-parallel branch of $n_s$ by $n_p$ Q-cells.                                                                         | 40 |

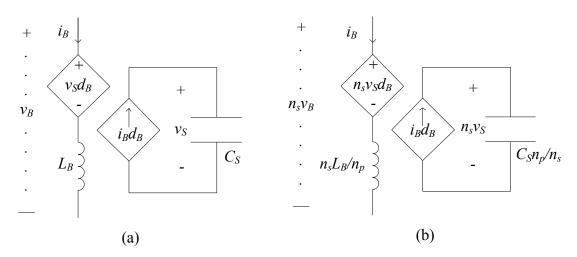

| Fig. 3-2. Example polyphase dc/ac BoBC. The ac phase shifts of $(k-1)2\pi/n_{br}$ are abbreviated as $\theta_k$ for brevity.                                                        | 44 |

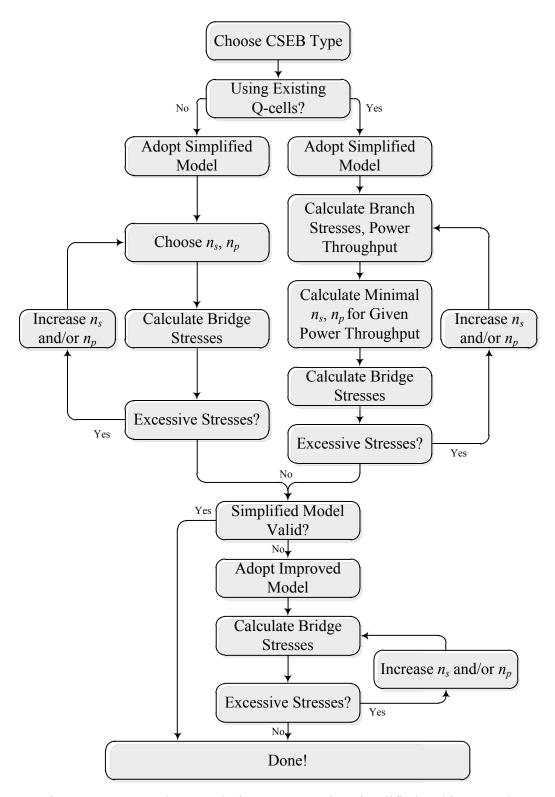

| Fig. 3-3. Suggested BoBC design process using simplified and improved average circuit models                                                                                        | 46 |

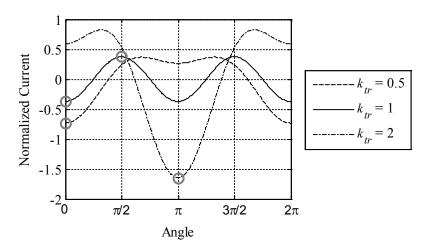

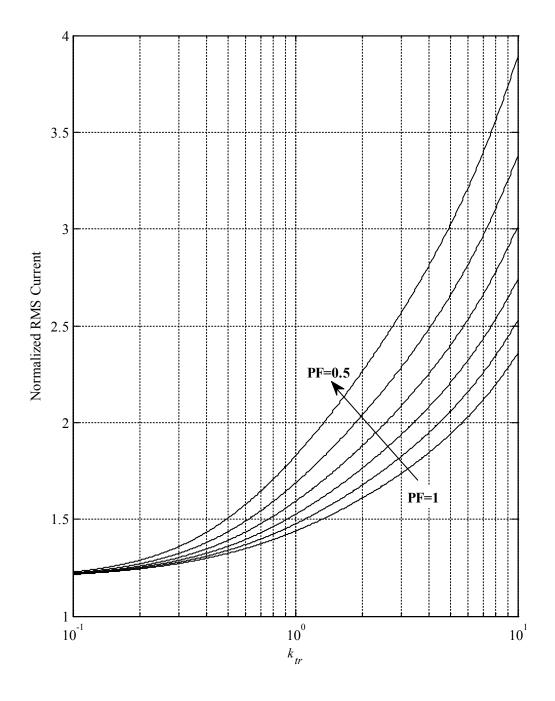

| Fig. 3-4. Variation of capacitor current vs. electrical angle for 3 values of transfer parameter $k_{tr}$ . The 4 circled locations indicate the occurrence of peak current values. | 52 |

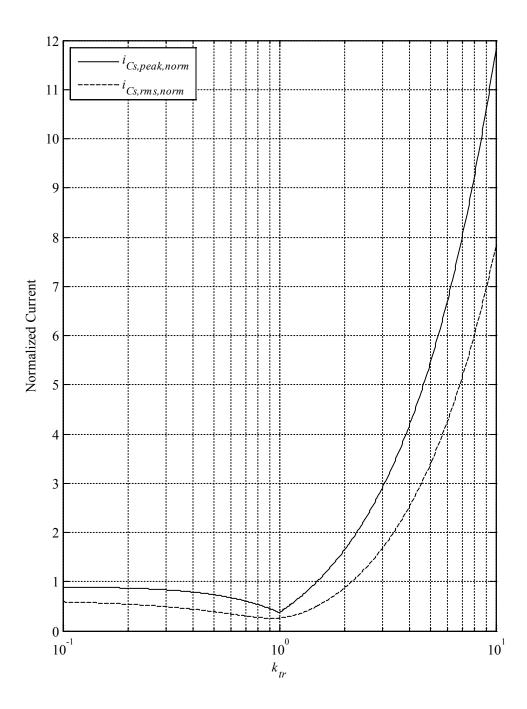

| Fig. 3-5. Variations of important storage capacitor sizing quantities at<br>unity power factor for different values of $k_{tr}$ , all normalized<br>to $I_{base}$ . This figure assumes $M = 0.9$ but other values may be<br>extracted by linearly scaling, e.g. $M = 0.3$ curves may be<br>found by multiplying the y-axis by $0.3/0.9=1/3$ | 53 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

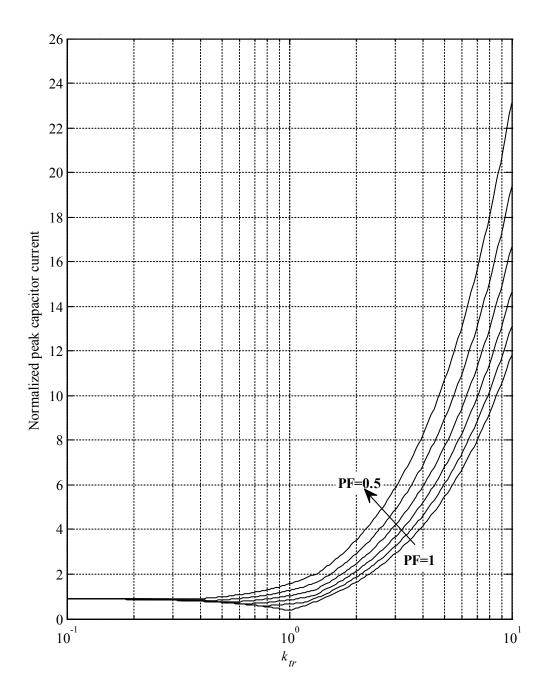

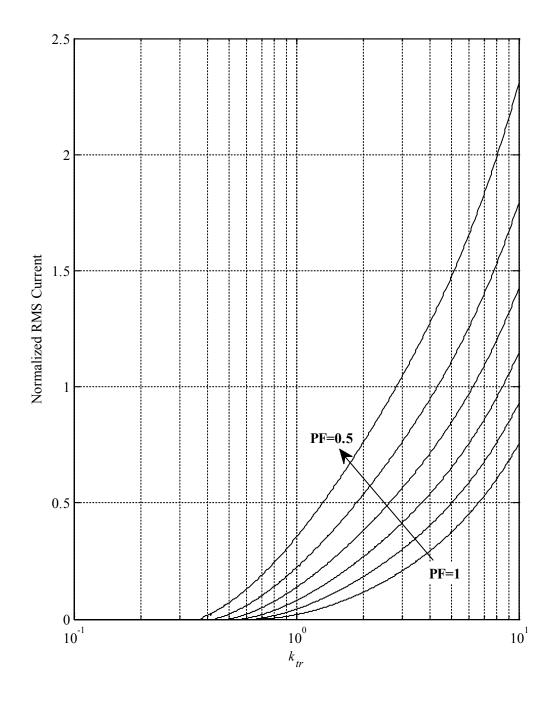

| Fig. 3-6. Variation of peak capacitor current $i_{Cs,peak,norm}$ values as a function of $k_{tr}$ , normalized to $I_{base}$ , and with linearly decreasing power factor. The minimum normalized current is 0.37 at $k_{tr} = 1$ and unity power factor.                                                                                     | 54 |

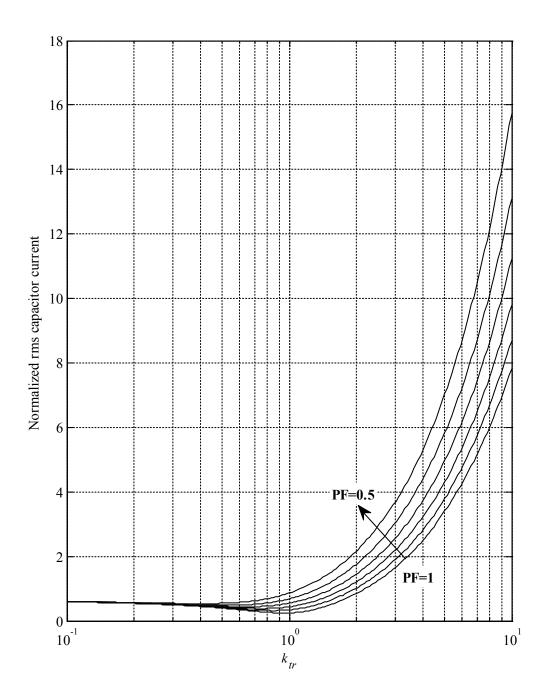

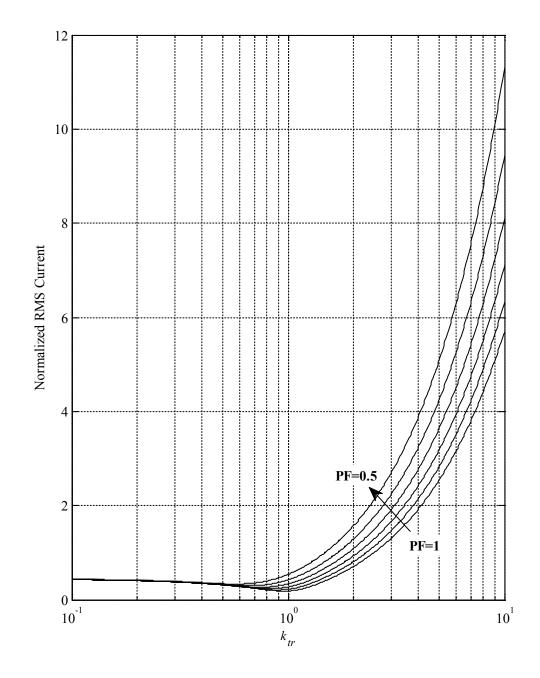

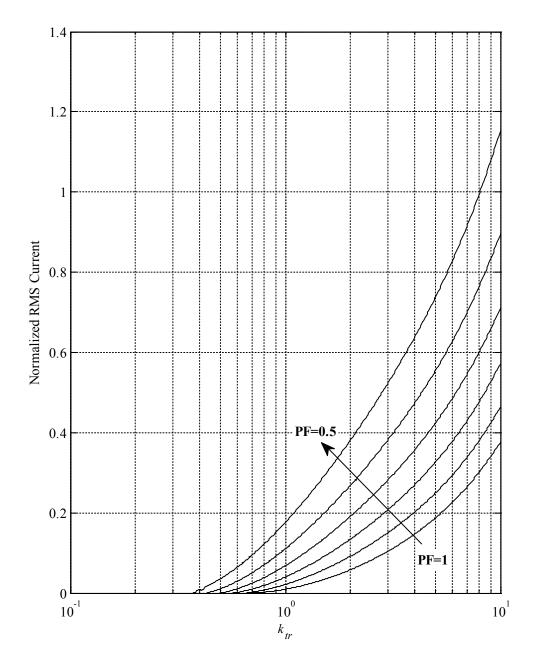

| Fig. 3-7. Variation of rms capacitor current $i_{Cs,rms,norm}$ values as a function of $k_{tr}$ , normalized to $I_{Cs,norm}$ , and with linearly decreasing power factor. The minimum normalized current is 0.26 at $k_{tr} = 0.93$ and unity power factor.                                                                                 | 55 |

| Fig. 3-8. Average model for calculating average voltages and currents of switches in the CSEB (a) asymmetrical half bridge and (b) full bridge and semi-full bridge                                                                                                                                                                          | 56 |

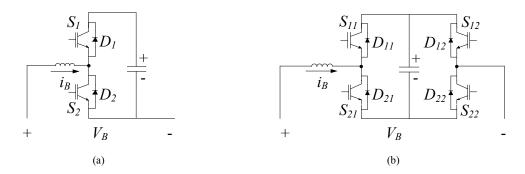

| Fig. 3-9. Switch and diode naming of (a) asymmetrical half bridge and (b) full bridge or semi-full bridge CSEBs.                                                                                                                                                                                                                             | 57 |

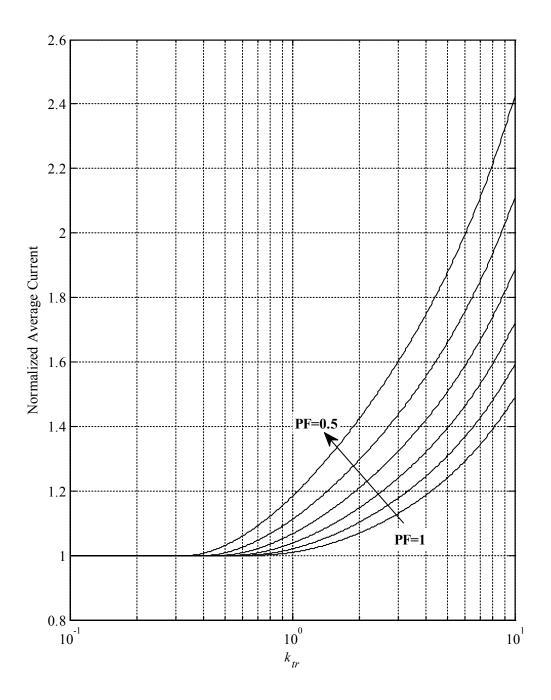

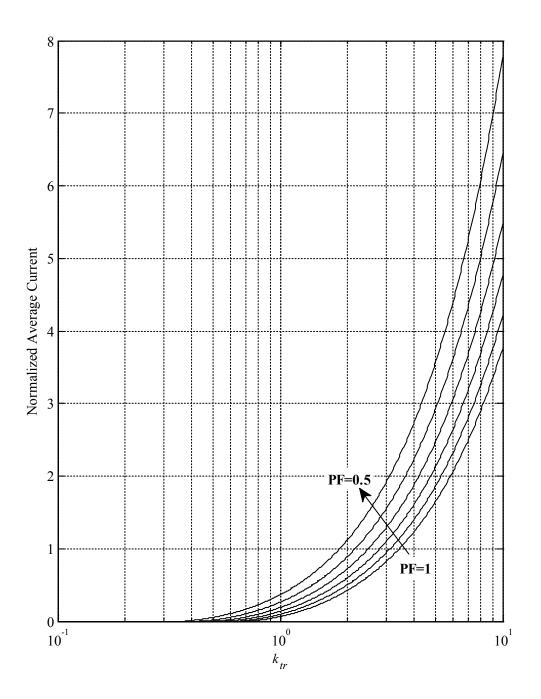

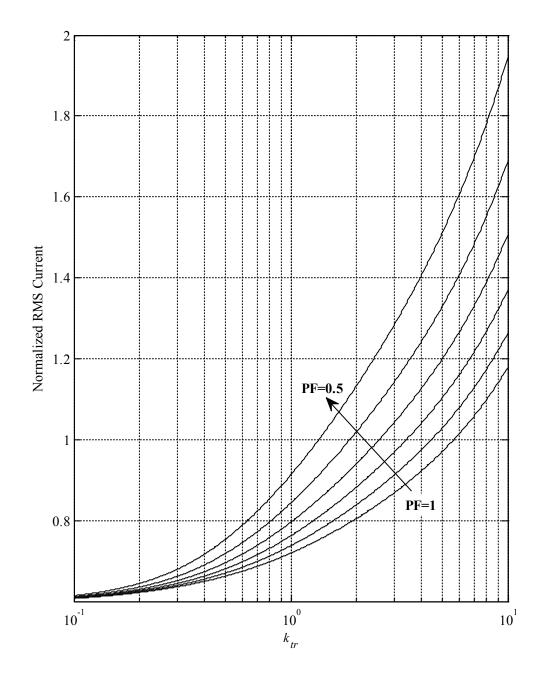

| Fig. 3-10. Variation of normalized average current through S1 or D1 as a function of $k_{tr}$ for $M = 0.9$ and varying power factor. The minimum value is approximately 0.11 at $k_{tr} = 0.86$ and unity power factor.                                                                                                                     | 59 |

| Fig. 3-11. Variation of normalized average current through S2 as a function of $k_{tr}$ for $M = 0.9$ and varying power factor. The minimum value is 1                                                                                                                                                                                       | 60 |

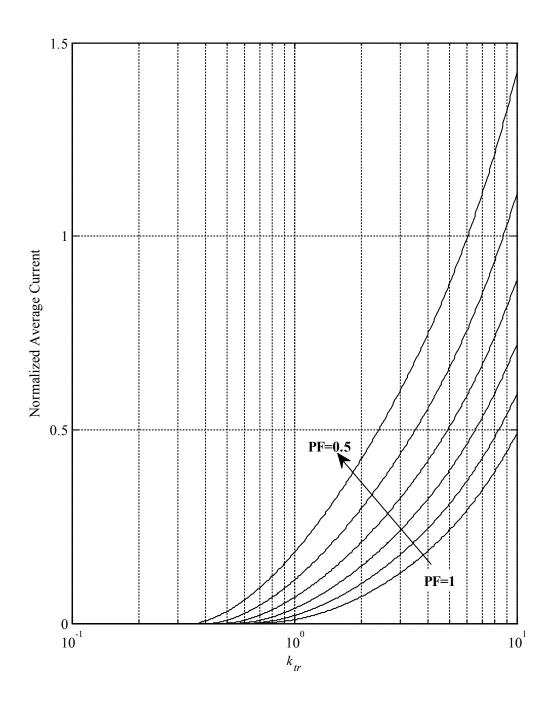

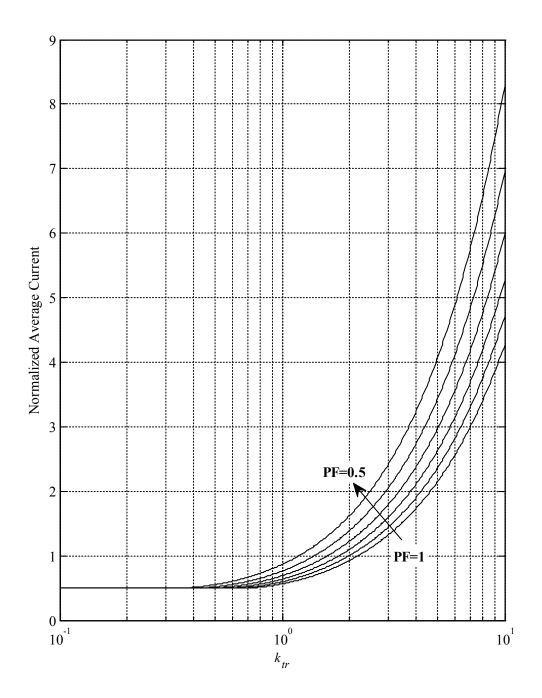

| Fig. 3-12. Variation of normalized average current through D2 as a function of $k_{tr}$ for $M = 0.9$ and varying power factor. The minimum value is 0, encountered at $k_{tr} = 0.707$ for unity power factor.                                                                                                                              | 61 |

| Fig. 3-13. Variation of normalized average current through S11 or S22 as a function of $k_{tr}$ for $M = 0.9$ and varying power factor. The minimum value is 0, encountered at $k_{tr} = 0.707$ for unity power factor.                                                                                                                      | 63 |

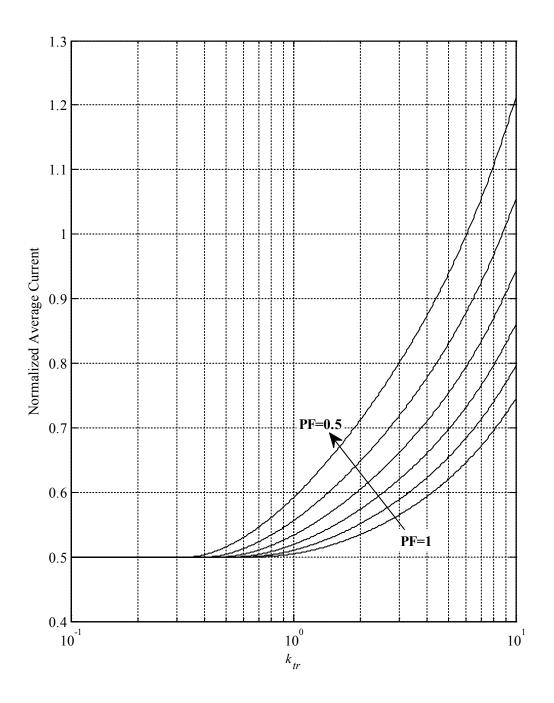

| Fig. 3-14. Variation of normalized average current through D11 or D22 as a function of $k_{tr}$ for $M = 0.9$ and varying power factor. The minimum value is 0.5.                                                                                                                                                                            | 64 |

|                                                                                                                                                                                                                                                                                                                                              |    |

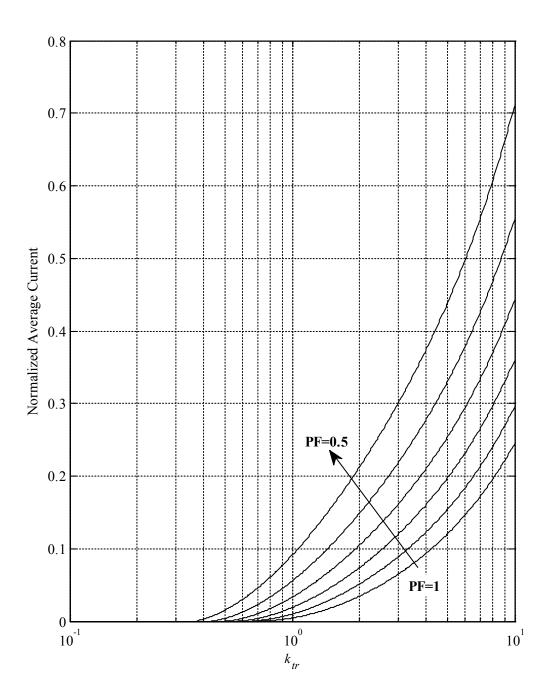

| Fig. 3-15. Variation of normalized average current through S21 or S12 as<br>a function of $k_{tr}$ for $M = 0.9$ and varying power factor. The<br>minimum value is 0.5.                                                                                                                        | 65 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Fig. 3-16. Variation of normalized average current through D21 or D12 as a function of $k_{tr}$ for $M = 0.9$ and varying power factor. The minimum value is 0, encountered at $k_{tr} = 0.707$ for unity power factor.                                                                        | 66 |

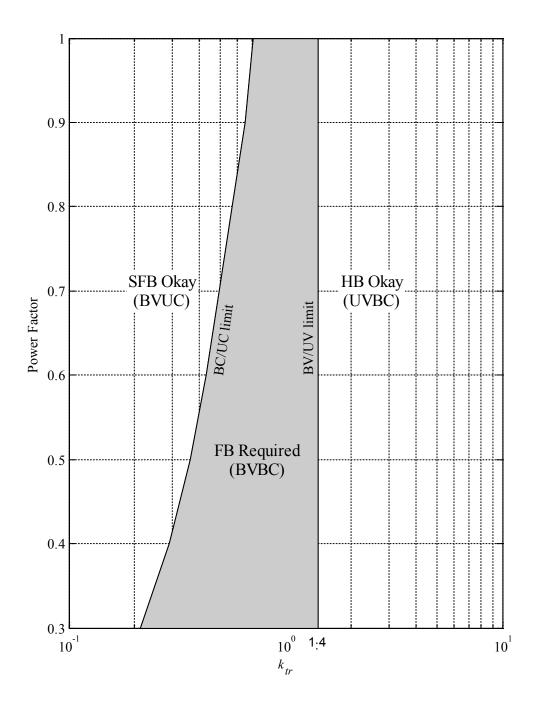

| Fig. 3-17. Map of suitability of 3 main CSEB designs based on $k_{tr}$ and power factor.                                                                                                                                                                                                       | 67 |

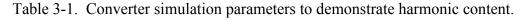

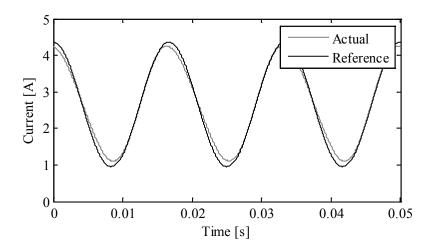

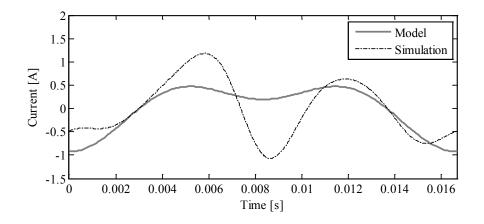

| Fig. 3-18. Actual vs. desired branch current for open loop operation of converter using parameters in Table 3-1. Significant undesired harmonics are observed in the actual waveform                                                                                                           | 73 |

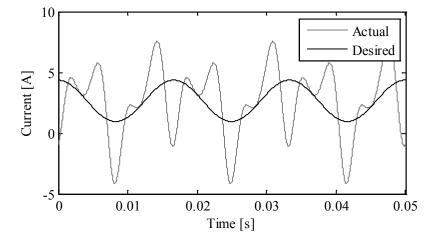

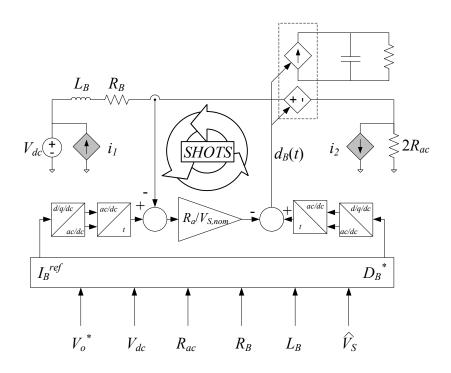

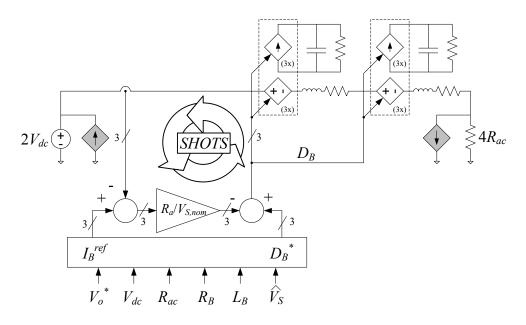

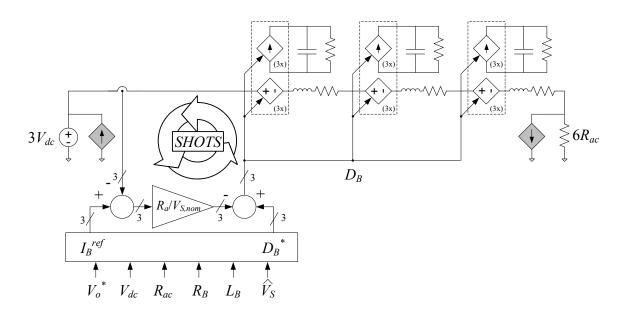

| Fig. 3-19. Structure of Scalar Higher Order Terms Suppression (SHOTS) control.                                                                                                                                                                                                                 | 74 |

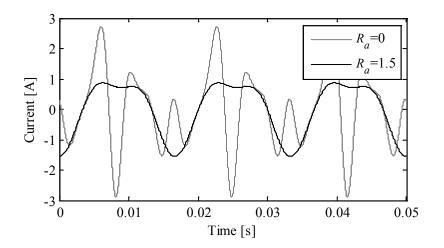

| Fig. 3-20. Branch current using SHOTS controller with $R_a = 0.15$                                                                                                                                                                                                                             | 75 |

| Fig. 3-21. Effect of SHOTS controller on capacitor current $i_{Cs}(t)$                                                                                                                                                                                                                         | 76 |

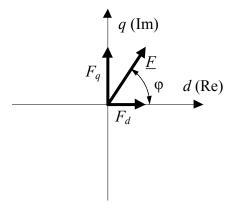

| Fig. 4-1. Arbitrary phasor $F$ , rotating counterclockwise at frequency $\omega$ in stationary reference frame. Equivalently, $F$ is viewed as stationary in the synchronous reference frame, which also rotates counterclockwise at $\omega$ .                                                | 81 |

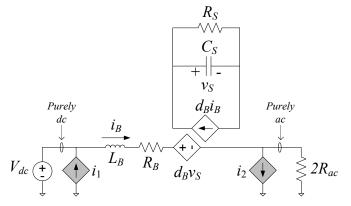

| Fig. 4-2. Scalar CSEB circuit model of an arbitrary bridge between $V_{dc}$ and the load resistance $R_{ac}$ . When branches are appropriately balanced, the load impedance is effectively doubled to $2R_{ac}$ , since each branch sources half of the load current as indicated in Fig. 3-2. | 83 |

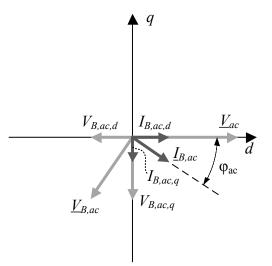

| Fig. 4-3. Phasor diagram of typical bridge voltage and current of circuit shown in Fig. 4-4. Currents are shown in dark gray and voltages are shown in light gray.                                                                                                                             | 85 |

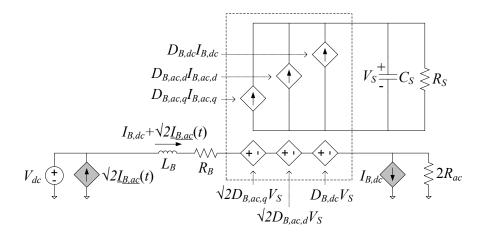

| Fig. 4-4. Dynamic phasor model of individual CSEB circuit, illustrating dc, ac direct and ac quadrature quantities explicitly                                                                                                                                                                  | 89 |

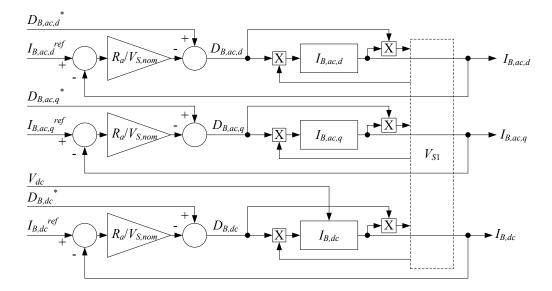

| Fig. 4-5. Actual closed loop current control implementation within individual CSEB                                                                                                                                                                                                             | 89 |

| Fig. 4-6. Effective closed loop current control implementation within individual CSEB.                                           | 90  |

|----------------------------------------------------------------------------------------------------------------------------------|-----|

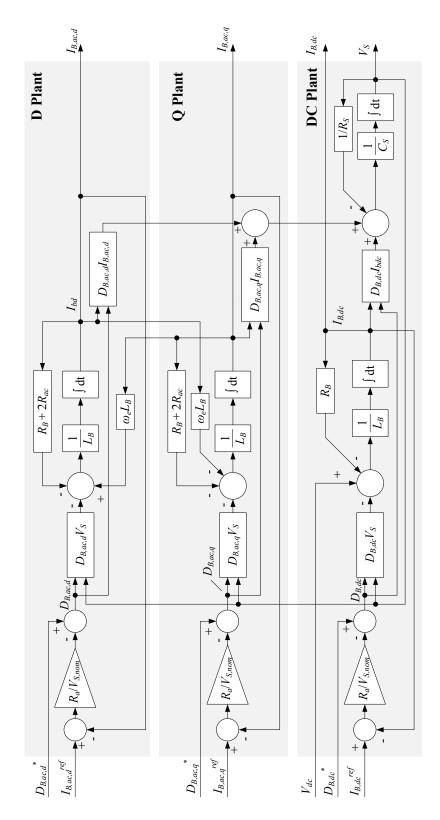

| Fig. 4-7. Full nonlinear state block diagram for SHOTS-enabled single bridge branch.                                             | 91  |

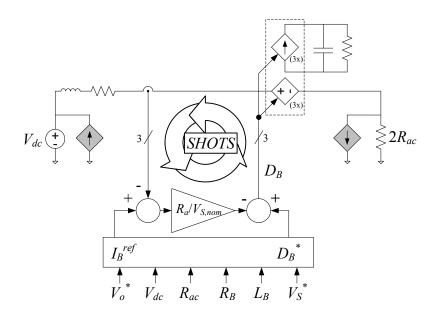

| Fig. 4-8. Simplified closed loop dynamic phasor model of individual CSEB.                                                        | 95  |

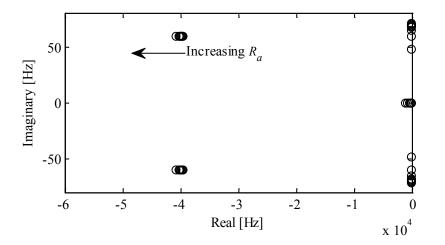

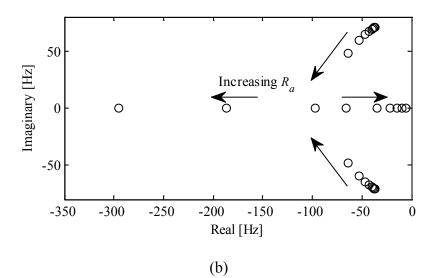

| Fig. 4-9. Eigenvalue migration over the range $0 \le R_a \le 0.15$ for all 4 eigenvalues.                                        | 96  |

| Fig. 4-10. Eigenvalue migration over the range $0 \le R_a \le 0.15$ showing close-up near imaginary axis                         | 97  |

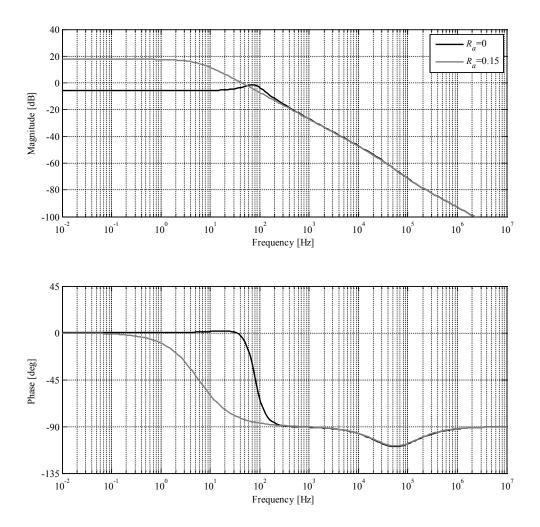

| Fig. 4-11. Transfer function of $V_S/d_{B,ac,d}$ comparing open loop dynamics with closed loop SHOTS controller dynamics         | 99  |

| Fig. 5-1. Dynamic phasor model of branch with $n_s=2$                                                                            | 103 |

| Fig. 5-2. Dynamic phasor model of branch with $n_s=3$                                                                            | 103 |

| Fig. 5-3. Open loop dynamic phasor model of $n_s=2$ branch circuit                                                               | 105 |

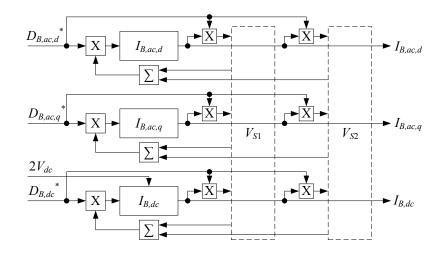

| Fig. 5-4. Simplified closed loop nonlinear state block diagram for $n_s=2$                                                       | 106 |

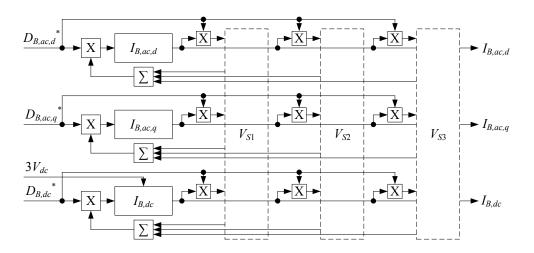

| Fig. 5-5. Simplified nonlinear state block diagram for $n_s=3$                                                                   | 114 |

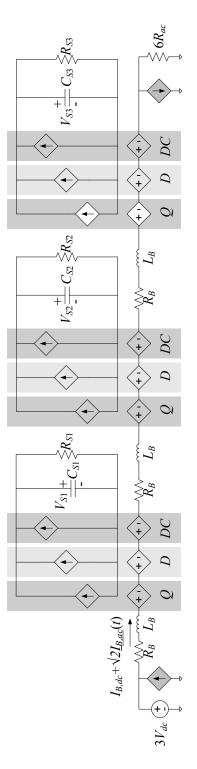

| Fig. 5-6. Open loop dynamic phasor model of $n_s$ =3 branch circuit                                                              | 116 |

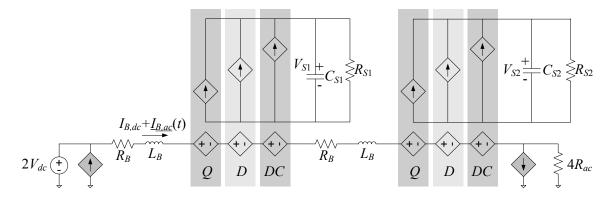

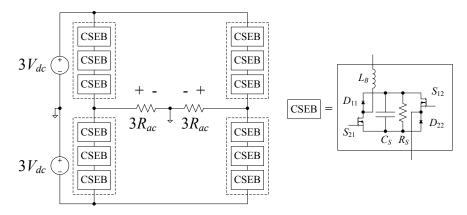

| Fig. 6-1. Topology of converter under investigation, showing DC→AC with single ac phase split across two grounded load resistors | 133 |

| Fig. 6-2. CSEB functional block diagram of experimental BoBC.                                                                    | 136 |

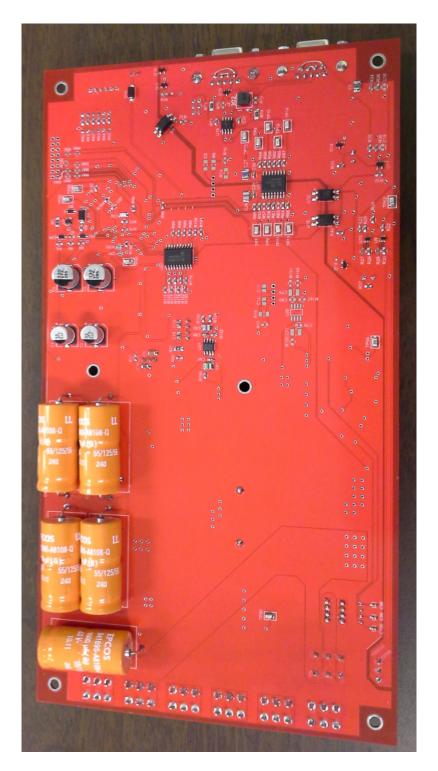

| Fig. 6-3. Top of populated CSEB PCB                                                                                              | 141 |

| Fig. 6-4. Bottom of populated CSEB PCB.                                                                                          | 142 |

| Fig. 6-5. Assignment of fault pins of CSEB microcontroller                                                                       | 147 |

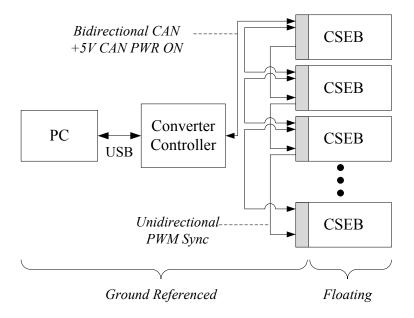

| Fig. 6-6. High level interconnection structure of BoBC highlighting communications                                               | 148 |

| Fig. 6-7. High level interconnection structure of BoBC highlighting communications                                               | 149 |

| Fig. 6-8. High level interconnection structure of BoBC highlighting communications capabilities.                                                                                                                                                    | 150 |

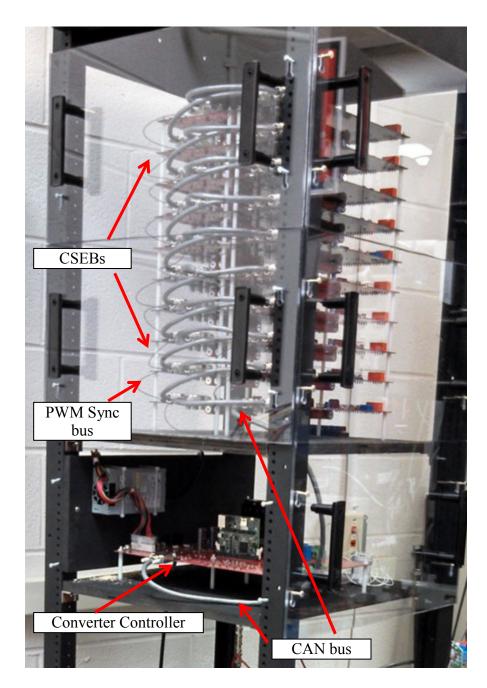

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Fig. 6-9. Hardware implementation of BoBC, showing high level interconnection.                                                                                                                                                                      | 151 |

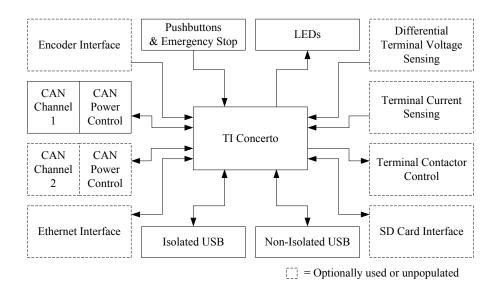

| Fig. 6-10. TI F28M35 Concerto microcontroller structure                                                                                                                                                                                             | 152 |

| Fig. 6-11. Converter Controller functional block diagram of experimental BoBC.                                                                                                                                                                      | 152 |

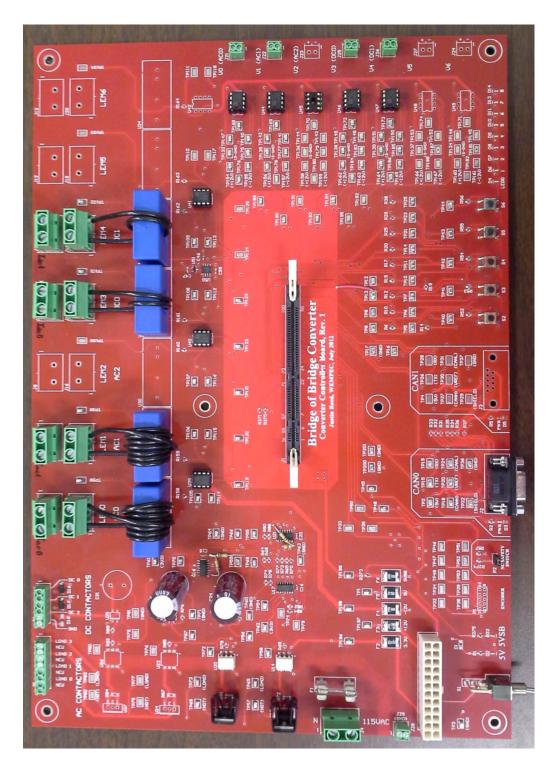

| Fig. 6-12. Texas Instruments Concerto F28M35 controlCARD, seated in<br>an evaluation board. Normally the controlCARD is seated in<br>the Converter Controller board to provide full control over<br>the BoBC components and communications platform | 153 |

| Fig. 6-13. Populated Converter Controller PCB                                                                                                                                                                                                       | 154 |

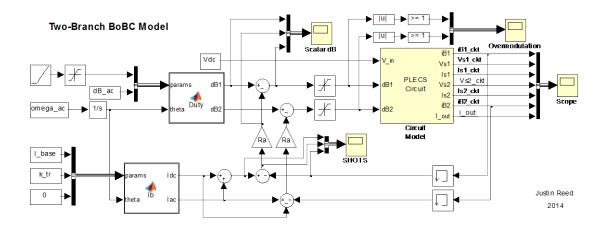

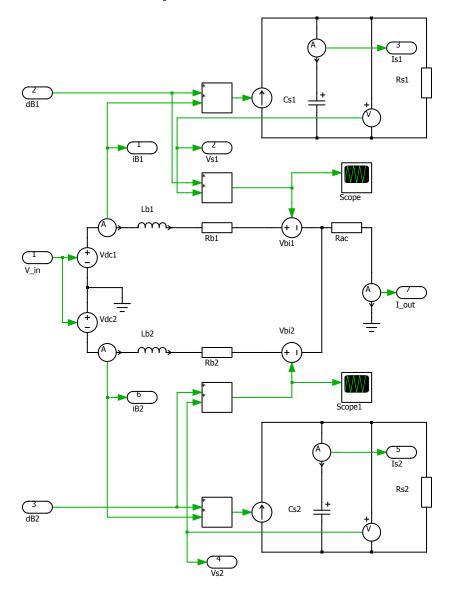

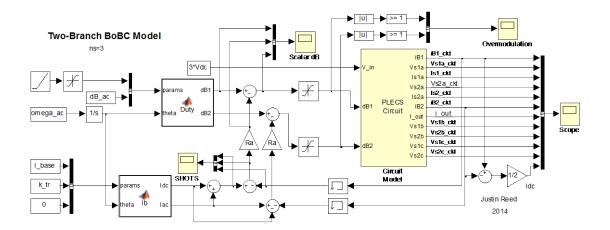

| Fig. 6-14. Simulink model of single BoBC branch, containing PLECS circuit model.                                                                                                                                                                    | 156 |

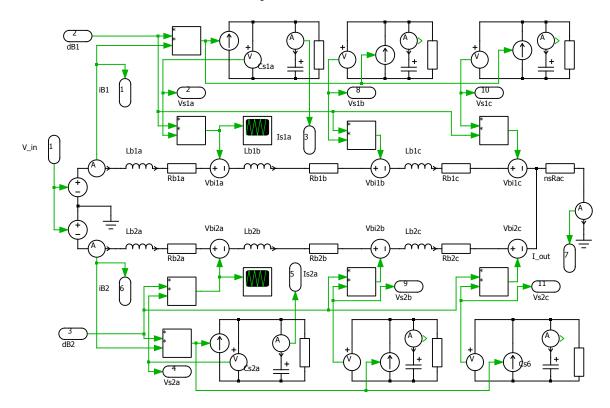

| Fig. 6-15. PLECS nonlinear circuit model within Simulink branch model.                                                                                                                                                                              | 157 |

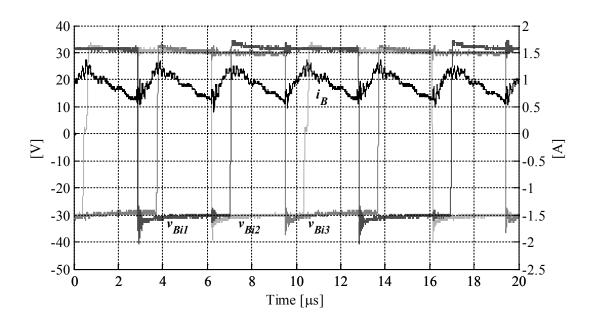

| Fig. 6-16. Experimental SFB waveforms showing bidirectional internal bridge voltages $v_{Bi}$ and unidirectional branch current $i_B$ for the operating point in Table 6-4.                                                                         | 158 |

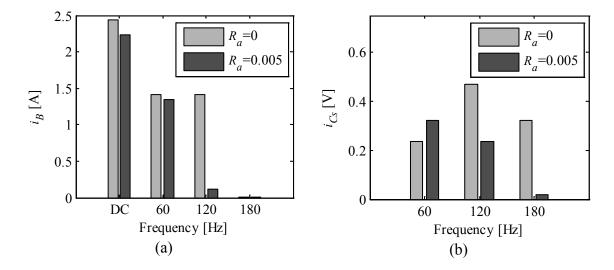

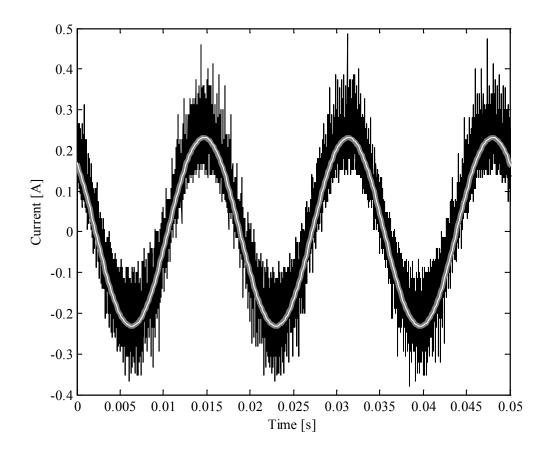

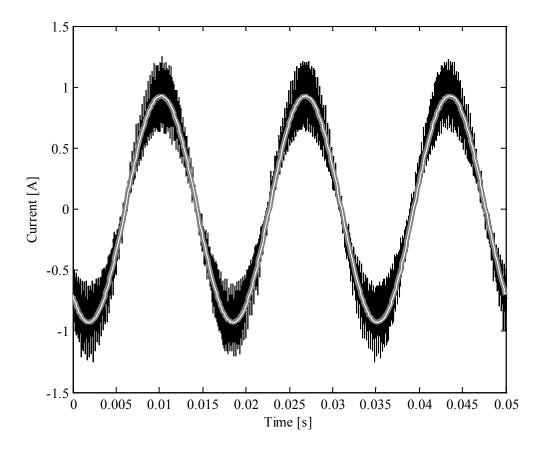

| Fig. 6-17. Effect of SHOTS control on (a) $i_B$ and (b) $i_{Cs}$ . Effective elimination of the undesirable 120 Hz $i_B$ and 180 Hz $v_S$ components is observed.                                                                                   | 160 |

| Fig. 6-18. Capacitor current mismatch between analytical predictions and simulation results for operating point in Table 6-5 without using SHOTS controller.                                                                                        | 161 |

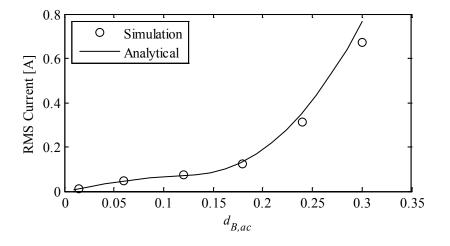

| Fig. 6-19. Validation of capacitor current model using simulations                                                                                                                                                                                  | 162 |

| Fig. 6-20. Capacitor current waveforms from circuit simulations (black) and analytical model (gray)                                                                                                                                                 | 163 |

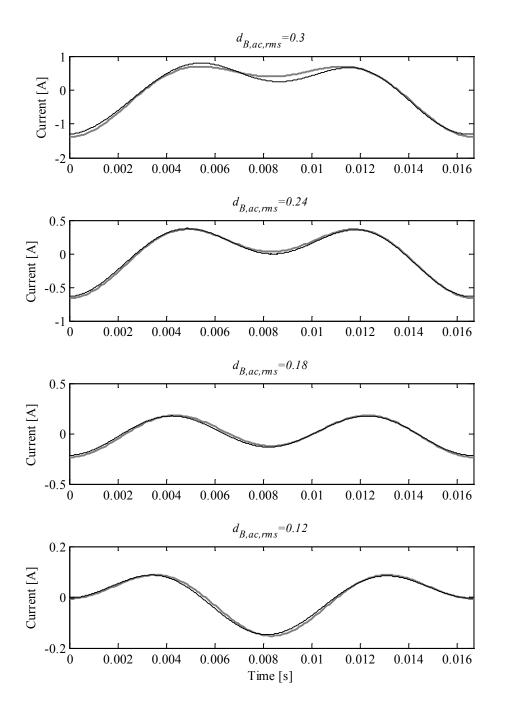

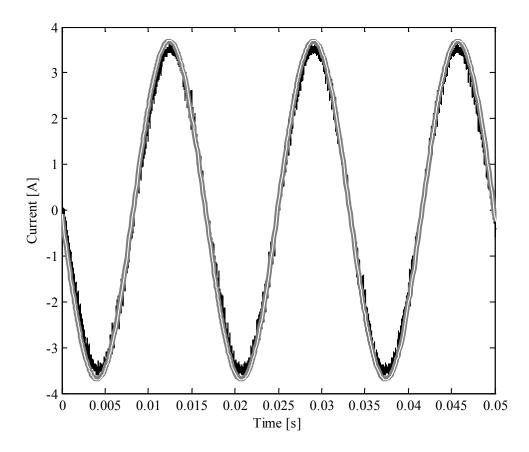

| Fig. 6-21. $I_{ac}$ output current waveforms for $d_{B,ac} = 0.015$ operating point from Table 6-8. Note that the analytical waveform is the thin white line directly on top of the thick gray line, denoting the simulation waveform.              |     |

| Fig. 6-22.  | $I_{ac}$ output current waveforms for $d_{B,ac} = 0.06$ operating point<br>from Table 6-8. Note that the analytical waveform is the thin<br>white line directly on top of the thick gray line, denoting the<br>simulation waveform. | 166 |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Fig. 6-23.  | $I_{ac}$ output current waveforms for $d_{B,ac} = 0.24$ operating point<br>from Table 6-8. Note that the analytical waveform is the thin<br>white line directly on top of the thick gray line, denoting the<br>simulation waveform. | 167 |

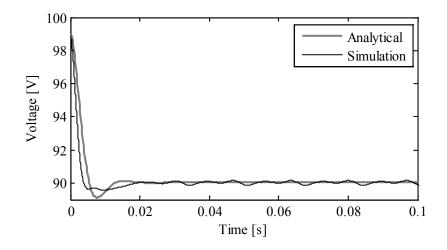

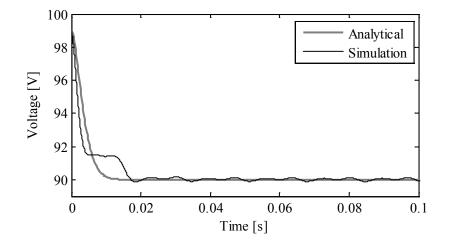

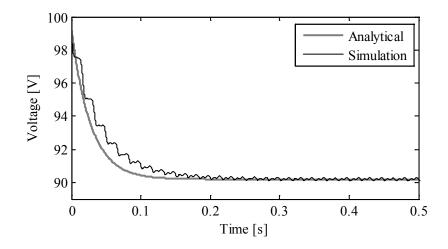

| Fig. 6-24.  | Underdamped transient response of nonlinear simulations and linear analytical model for $R_a = 0.003$ . LC eigenvalues lie at -47.1 +/- j64.6 Hz.                                                                                   | 170 |

| Fig. 6-25.  | Near-critically damped transient response of nonlinear simulations and linear analytical model for $R_a = 0.0105$ . LC eigenvalues lie at -74.2 +/- j29.9 Hz.                                                                       | 171 |

| Fig. 6-26.  | Overdamped transient response of nonlinear simulations and linear analytical model for $R_a = 0.15$ . LC eigenvalues lie at - 5.8 Hz and -1.1kHz.                                                                                   | 171 |

| Fig. 6-27.  | Simulink model of single BoBC branch with <i>n<sub>s</sub></i> =3, containing multilevel PLECS circuit model.                                                                                                                       | 172 |

| Fig. 6-28.  | PLECS nonlinear circuit model for $n_s$ =3 branch, contained within Simulink branch model.                                                                                                                                          | 173 |

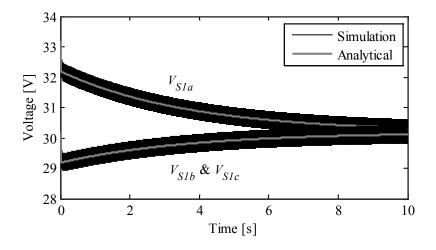

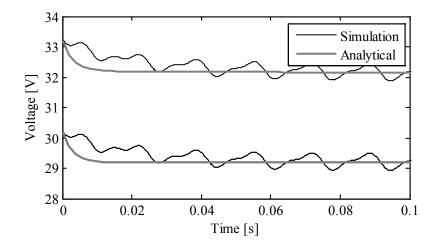

| Fig. 6-29.  | Transient response of all 3 capacitor voltages using nonlinear simulations and linear analytical model for $R_a = 0.15$                                                                                                             | 174 |

| Fig. 6-30.  | Close-up of transient response of all 3 capacitor voltages using nonlinear simulations and linear analytical model for $R_a = 0.15$                                                                                                 | 174 |

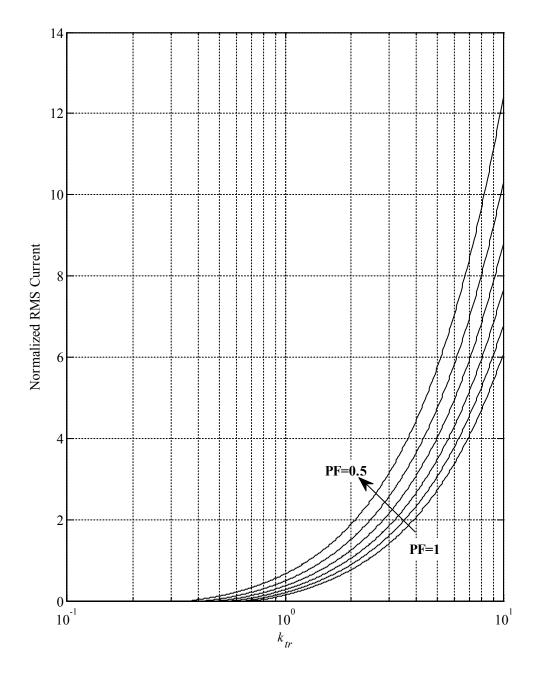

| Fig. 8-1. N | Normalized rms current through S1 for $M = 0.9$ and varying<br>power factor. The minimum value is approximately 0.18 at<br>$k_{tr} = 0.95$ and unity power factor                                                                   | 187 |

| Fig. 8-2. N | Normalized rms current through D1 for $M = 0.9$ and varying<br>power factor. The minimum value is approximately 0.18 at<br>$k_{tr} = 0.79$ and unity power factor                                                                   | 188 |

| Fig. 8-3. | Normalized rms current through S2 for $M = 0.9$ and varying<br>power factor. The minimum value is approximately 1.22 at<br>$k_{tr} = 0.10$ and unity power factor       | 189 |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Fig. 8-4. | Normalized rms current through D2 for $M = 0.9$ and varying<br>power factor. The minimum value is 0, encountered at $k_{tr} =$<br>0.707 for unity power factor          | 190 |

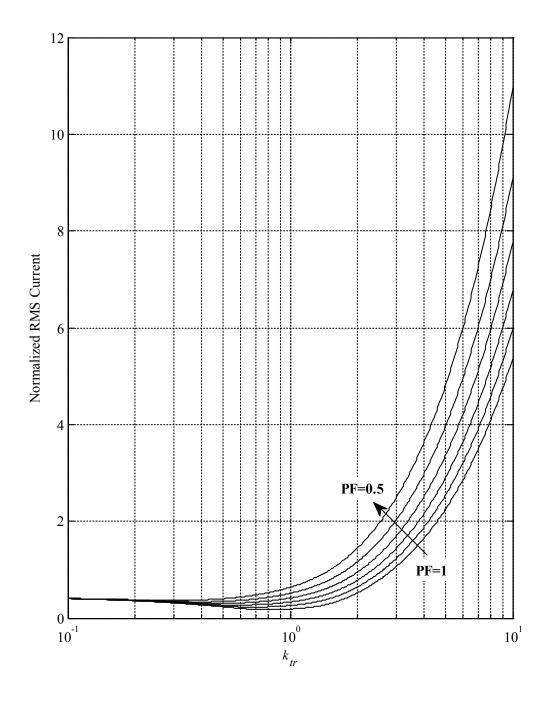

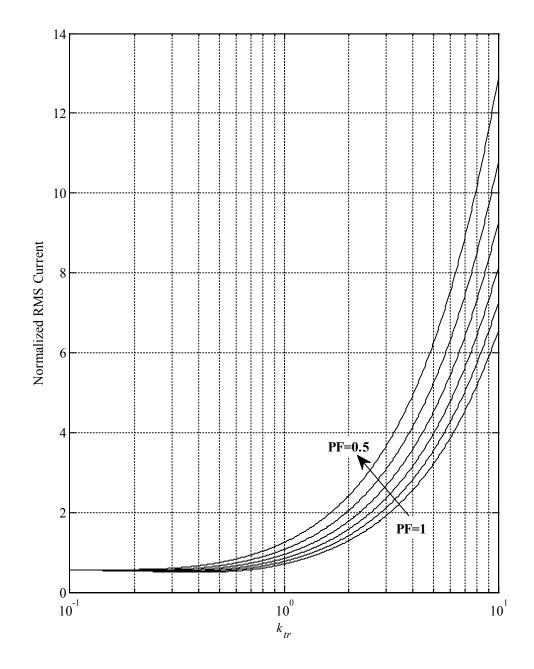

| Fig. 8-5. | Normalized rms current through S11 or S22 for $M = 0.9$ and<br>varying power factor. The minimum value is 0, encountered<br>at $k_{tr} = 0.707$ for unity power factor. | 192 |

| Fig. 8-6. | Normalized rms current through D11 or D22 for $M = 0.9$ and<br>varying power factor. The minimum value is 0.51 at $k_{tr} =$<br>0.39 for unity power factor             | 193 |

| Fig. 8-7. | Normalized rms current through S21 or S12 for $M = 0.9$ and<br>varying power factor. The minimum value is 0.61 at $k_{tr} = 0.1$<br>for unity power factor.             | 194 |

| Fig. 8-8. | Normalized rms current through D21 or D12 for $M = 0.9$ and<br>varying power factor. The minimum value is 0, encountered<br>at $k_{tr} = 0.707$ for unity power factor. | 195 |

| Table 2-1. ISEB and CSEB Q-cell terminal characteristics using UES or<br>BES. (R=Required, C=Capable, Blank=Impossible) | 34  |

|-------------------------------------------------------------------------------------------------------------------------|-----|

| Table 3-1. Converter simulation parameters to demonstrate harmonic content.                                             | 73  |

| Table 4-1. Converter parameters for dynamic analysis.                                                                   | 96  |

| Table 4-2. Eigenvalues at one operating point, with and without SHOTS controller.                                       | 96  |

| Table 5-1. Circuit parameter summary for $n_s=1$ through 3 for one<br>operating point.                                  | 102 |

| Table 5-2. Converter parameters for dynamic analysis of $n_s=2$                                                         | 113 |

| Table 5-3. Eigenvalues for $n_s=2$ , with and without SHOTS controller                                                  | 113 |

| Table 5-4. Converter parameters for dynamic analysis of $n_s=3$                                                         | 122 |

| Table 5-5. Eigenvalues for $n_s$ =3 at one operating point, with and without SHOTS controller.                          | 122 |

| Table 5-6. Summary of eigenvalue without SHOTS ( $R_a = 0$ )                                                            | 123 |

| Table 5-7. Summary of eigenvalues with SHOTS ( $R_a = 0.15$ )                                                           | 123 |

| Table 6-1. Converter design specifications (in rms where applicable)                                                    | 130 |

| Table 6-2. Design parameters for CSEBs within the converter                                                             | 130 |

| Table 6-3. CAN messages used in hardware.                                                                               | 140 |

| Table 6-4. DC operating point for validation of SFB BVUC characteristics.                                               | 157 |

| Table 6-5. | Converter simulation and analytical model parameters              | 160 |

|------------|-------------------------------------------------------------------|-----|

| Table 6-6. | Reduction in rms currents resulting from use of SHOTS controller. | 160 |

| Table 6-7. | Capacitor current model verification                              | 161 |

| Table 6-8. | Effect of $d_{B,ac}$ on $V_{S}$                                   | 164 |

| Table 6-9. | Effect of $d_{B,ac}$ on $V_{S}$                                   | 168 |

| Table 6-10 | Effect of $d_{B,dc}$ on $V_{S}$                                   | 168 |

xxii

xxiii

- AC Alternating Current

- ADC Analog to Digital Converter

- BoB Bridge of Bridge

- BoBC Bridge of Bridge Converter

- BJT Bipolar Junction Transistor

- BV Bidirectional Voltage

- BC Bidirectional Current

- BES Bidirectional Energy Storage

- CAN Controller Area Network

- CC Cross Coupling

- CSC Current Source Converter

- CSEB Capacitive Storage Embedded Bridge

- DC Direct Current

- ECC Energy Conservation Constraint

- EMI Electromagnetic Interference

- ESL Equivalent Series Inductance

- ESR Equivalent Series Resistance

- FB Full Bridge

## HB Half Bridge

- HEV Hybrid Electric Vehicle

- HVDC High Voltage Direct Current

- IGBT Insulated Gate Bipolar Transistor

- IGCT Integrated Gate-Commutated Thyristor

- IPC Interprocessor Communications

- ISEB Inductive Storage Embedded Bridge

- ISR Interrupt Service Routine

- KCL Kirchhoff's Current Law

- KVL Kirchhoff's Voltage Law

- LTI Linear Time-Invariant

- M2C Modular Multilevel Converter

- MERS Magnetic Energy Recovery Switch

- MMLC Modular Multilevel Converter

- M<sup>2</sup>LC Modular Multilevel Converter

- MOSFET Metal Oxide Semiconductor Field Effect Transistor

- OC Overcurrent

- OV Overvoltage

- PF Power Factor

- PM Permanent Magnet

- PSPWM Phase-Shifted PWM

- PV Photovoltaic

- PWM Pulse Width Modulation

- QC Q-cell

- SFB Semi-Full Bridge

- SHOTS Scalar Higher-Order Term Suppression

- SID Standard Identifier

- SMES Superconducting Magnetic Energy Storage

- SPDT Single Pole Double Throw

- SVM Space Vector Modulation

- UC Unidirectional Current

- UES Unidirectional Energy Storage

- UV Unidirectional Voltage, alt. Undervoltage

- VSC Voltage Source Converter

- ZSC Z-Source Converter

- $\theta$  Low frequency ac phase offset

- $\varphi_{ac}$  Power factor angle

- $\omega_{ac}$  Fundamental ac frequency, in rad/sec

- $C_S$  Bridge energy storage capacitor

- $d_B$  Bridge duty ratio

- $d_1, d_2$  Duty ratio of individual switches within full bridge CSEB

- *I<sub>ac</sub>* Terminal ac current, in rms

- $i_B$  Bridge current, in rms

- *I*<sub>base</sub> Base current for normalization

| $i_{Cs}$                | Capacitor current                                                      |

|-------------------------|------------------------------------------------------------------------|

| i <sub>D</sub>          | Diode current                                                          |

| I <sub>dc</sub>         | Terminal dc current                                                    |

| <i>is</i>               | Switch current                                                         |

| j                       | $\sqrt{-1}$                                                            |

| <i>k</i> <sub>arm</sub> | Parallel interleaving coefficient per arm                              |

| <i>k</i> <sub>str</sub> | Series interleaving coefficient per string                             |

| <i>k</i> <sub>tr</sub>  | Voltage transfer ratio                                                 |

| $L_B$                   | Bridge inductance                                                      |

| М                       | Modulation index                                                       |

| <i>n</i> <sub>br</sub>  | Number of branches connected to dc terminal                            |

| $n_p$                   | Number of parallel-connected strings per branch                        |

| ns                      | Number of series-connected Q-cells per string (or branch if $n_p=1$ )  |

| $P_{ac}$                | AC terminal power, in rms                                              |

| $P_{dc}$                | DC terminal power                                                      |

| $R_a$                   | "Active resistance" gain of SHOTS controller                           |

| $R_{ac}$                | AC load resistance                                                     |

| $R_B$                   | Resistance of bridge inductor                                          |

| R <sub>eff</sub>        | Effective resistance                                                   |

| $R_S$                   | Load resistance on energy-storage side of bridge, and/or bridge losses |

| $S_B$                   | Apparent power per unit bridge, in rms                                 |

| $V_{ac}$                | AC output voltage per unit bridge, in rms                              |

|                         |                                                                        |

| V <sub>ac,tot</sub>   | AD output voltage at converter terminals, in rms                 |

|-----------------------|------------------------------------------------------------------|

| $v_B$                 | External bridge voltage                                          |

| $v_{Bi}$              | Internal bridge voltage                                          |

| V <sub>dc</sub>       | DC input voltage per unit bridge                                 |

| V <sub>dc,tot</sub>   | DC input voltage at converter terminals                          |

| $V_L$                 | Bridge inductor voltage                                          |

| $V_S$                 | Bridge capacitor voltage                                         |

| V <sub>S,dc,tot</sub> | Sum total of series-connected CSEB capacitor voltages per branch |

| Z <sub>ac</sub>       | AC bus impedance                                                 |

|                       |                                                                  |

$Z_{dc}$  DC bus impedance

This chapter provides a general introduction to dc/ac converter topologies. Objectives of this work are outlined, and a brief synopsis of the individual chapters is provided.

## **1.1** Overview of dc-ac converter topologies

Of all types and forms of electrical power conversion, perhaps the most frequently required functionality is between direct current (dc) and alternating current (ac). Both forms of electricity are abundant in modern society and neither shows any sign of giving up ground. For example, the ac form has been utilized with great success particularly in rotating machinery, power transmission, and power distribution systems [1], whereas the dc form is naturally present in batteries, photovoltaic (PV) systems [2], and fuel cells [3]. Naturally, the integration of these and plentiful other energy exchange systems require dc-ac converters to deliver power from the source to the load.

With an obvious demand for dc-ac power conversion systems, a wide variety of both fundamentally and incrementally novel power converter topologies continue to be proposed in the literature. Unfortunately, using historically available commercial products as a measurement, the vast majority of fundamentally new dc-ac and ac-dc converter topologies have had limited success. In fact, only two basic solid state converter topologies have been commonly used – the current source converter (CSC) and the voltage source converter (VSC), commonly with two or at times a few more levels.

Two additional topologies have been recently proposed – the Z-source converter (ZSC) and the bridge of bridge converter (BoBC). While as of this writing, neither has seen significant commercial use, the publication record of the ZSC and BoBC indicates that they show the most promise and interest by academics and industry members alike, and so they are considered along with the CSC and VSC.

Fundamentally, all 4 topologies are capable of performing in multiphase ac systems of arbitrary phase number. Therefore, the 4 topologies are discussed in the context of a single-phase ac system with no loss of generality regarding multiphase use. Furthermore, all topologies are suitable for use in either unidirectional or bidirectional power flow applications with minimal or no modifications from the circuit diagrams shown. The discussion therefore makes no assumptions regarding power flow directionality.

## **1.1.1 Classical converter topologies**

Early switched mode dc-ac power conversion systems utilized the CSC topology [4, 5], characterized by a current source (inductor) on the dc bus, shown in Fig. 1-1. One reason for the phenomenal success of this topology was that its behavior was well-aligned with the strengths of the switching devices available at the time. That is, thyristors, thyratrons, mercury arc valves, and the like could be triggered into conduction but could not be actively turned off (commutated). Instead, the converters typically relied upon the ac waveform itself to force the devices into commutation by careful timing of switching events with respect to the ac current zero crossings.

Fig. 1-1. Current source converter topology for single phase ac-dc power conversion realized with thyristors.

Fig. 1-2. Voltage source converter topology for single phase ac-dc power conversion realized with IGBTs.

After the introduction of high power self-commutating switches, such as bipolar junction transistors (BJTs), the CSC largely fell out of popularity in preference for the VSC, which is characterized by a voltage source (capacitor) on the dc bus [6, 7]. By exchanging the bulky and lossy inductor with the capacitor, much more desirable cost, weight and efficiency traits are achieved. This topology is shown in Fig. 1-2, realized with modern insulated gate bipolar transistors (IGBTs). The VSC now dominates the commercial market of dc-ac converters, except at extremely high power levels where thyristor-based switches are still popular [8].

## **1.1.2 Z-source converter**

The ZSC is a more recent addition to the family of dc-ac topologies, primarily characterized by an impedance network on the dc bus [9]. By utilizing both capacitors

and inductors in the network, phenomena such as shoot-through in the VSC are given new functionality such as voltage boosting. It also provides additional flexibility in the use of current and voltage sources on the ac and dc sides. However, additional reactive elements are required, including two inductors that can contribute non-negligible cost to the system. In the literature, the ZSC has seen considerable analysis [10] and has been applied to a variety of areas including fuel cells [9] and hybrid electric vehicles (HEVs) [11] but is not yet known to have commercial applications.

Fig. 1-3. Z-source converter topology for single phase ac-dc power conversion with current-stiff ac bus.

Fig. 1-4. Generalized dc-ac BoBC topology for single phase ac-dc power conversion.

## 1.1.3 Bridge of bridge converter

The final dc-ac converter topology is the BoBC [12], also known by Marquardt as the modular multilevel converter (MMLC, M<sup>2</sup>LC or M2C) [13], the chainlink converter by Oates [14], and the magnetic energy recovery switch (MERS) by Shimada [15]. The

various converter names correspond to different implementations; the M2C is presented in the literature as using very specific *submodules*, and is often applied to HVDC conversion, while the MERS uses the same circuits for controlling resonant circuits. The BoBC concept, however, is not limited to any of these single applications; in fact it encompasses all such applications, because the BoBC concept is based purely on distributed, controlled energy sources for modulating power throughput.

The BoBC is shown in Fig. 1-4 and comprises 4 converter branches, in this case each behaving as a controllable current source, to modulate power throughput. This is a relatively new topology, having been introduced in 2003 [16], and its capabilities, limitations, dynamics and control are current research topics under active investigation [8, 12-14, 16-98]. The BoBC has several very desirable attributes, namely its minimal inductance requirements; the capability of full buck and boost operation, regardless of power flow direction, and without the use of a transformer; and it is naturally fault tolerant. Furthermore, the converter branches may consist of any number of smaller conversion units in series and/or parallel, providing a multilevel architecture with additional flexibility, fault tolerance, and further reduction of inductance requirements using interleaving techniques. The BoBC is therefore an attractive topology for a wide range of dc-ac converters across all power levels, frequencies, voltages, currents and applications. In very recent years, the BoBC has seen an explosion of popularity in the literature. However, nearly all such publications examine only a very small set of BoBC applications and topics, illustrating that the dc-ac BoBC has yet to be thoroughly explored from a generalized standpoint.

Among the BoBC literature for dc-ac applications, the dominant theme is on high voltage direct current (HVDC) power transmission converters [8, 13, 36, 39-41] and other high power applications using 3-phase ac [26, 29, 31, 42, 99]. Like the ZSC, the BoBC is not limited to use in dc-ac converters, having been applied to ac-ac power converters [20-23, 43-45, 100-102], ac series compensation [46, 103-111], ac shunt compensation [37, 46-49, 51, 112], electric machine drives [53, 58, 66-68], and a handful of specialized applications [8, 15, 44, 46, 69, 113-115]. The BoBC concept has also been extended to a unique ac-ac converter called the Hexverter [70], a detailed discussion of which is beyond the scope of this work.

A certain number of publications can be applied to a general BoBC topology and are therefore of direct interest to defining the objectives of this research. An excellent survey of the salient developments within the BoBC literature is [71], which includes topics such as converter models that incorporate various levels of detail, the use of Space Vector Modulation (SVM) [25, 26] versus staircase modulation [72] in high power converters and Pulse Width Modulation (PWM) in lower power converters, and control strategies of all BoBC types. A detailed analysis of BoBC system dynamics with a considerable amount of behavioral insight is provided in [60]. A separate work focuses on the frequency-domain analysis [73]. Huang et al discuss various distributed BoBC controller communications options in [74].

Just like any power converter, a wide variety of modeling approaches can be applied to the BoBC, including averaged bridge modeling [12, 41], state space using the abc frame [75][34], state space in dq0 frame [38, 76], and  $\alpha\beta$  modeling applied to motor

drives [66]. DQ0 modeling has also been applied to nonlinear control schemes representing specific frequencies [77].

Generally speaking, converter models are used to determine the sizing of the converter elements. A very instructive research for sizing of components and calculation of losses is that of Allebrod, Hamerski and Marquardt [13]. However, these calculations focus on HVDC converters for 3-phase ac and are therefore not applicable to the general BoBC topology. A related work by Bernet et al is [19]. Since the writing of the original version of this document, capacitor sizing was proposed [78], also by Bernet. Another design-oriented investigation, specific to ac drives, is [67].

Many works also cover much lower-level implementation topics, such as the various possible modulation schemes. For example, [80] is a survey of PWM methods to determine how many bridges to connect within a branch, to realize the desired voltage waveform, but leaves open the subject of which capacitors to switch high and low to provide capacitor charge balancing. Another survey is [99]. In the classical BoBC implementation in HVDC applications, staircase modulation is often used to leverage the very high numbers of levels and low switching frequencies of medium-voltage switches [72]. Using smaller, faster switches enables PWM methods, such as Phase-Shifted PWM (PSPWM) [81], an alternative PWM strategy [82], and reduced switching frequency modulation [83]. Different still is bang-bang/hysteretic control and modulation, discussed in [54, 85].

As will be shown later in this dissertation, a large number of control "handles" are provided within a BoBC that can be used to govern its behavior. As such, the BoBC can be an extremely complex device and achieving satisfactory control of its energy states and terminal quantities is of utmost importance. Furthermore, the BoBC plant is inherently nonlinear, which can lead to in-depth control system analyses. For example, interactions between multiple control schemes are investigated in [59]. A variety of works present nonlinear control schemes, for example [79, 86, 87] describe a nonlinear approach to encompass all aspects of current and voltage control, and [88] proposes a model predictive control methodology. Finally, control schemes can be leveraged to maximize certain effects such as minimizing bridge capacitance [90] or direct modulation of capacitor voltage ripple [61].

Particular attention has been paid to the problem of capacitor voltage balancing within the BoBC. Salient voltage balancing schemes include Marquardt's sorting algorithm [25], which selects bridge switching states depending on the polarity of branch current and each capacitor's relative value, e.g. the lowest capacitor voltages get increased and the highest voltages decreased. This scheme has been adopted by a number of researchers including Saeedifard and Iravani [91] and Bernet et al [18, 19, 32, 33]. Reference [32] highlights that only one bridge within a branch incurs PWM switching at a given time, with the other bridges locked in their respective switching states.

Akagi et al proposed a PWM-based balancing scheme [48, 49], which utilizes averaging over positive and negative portions of the branch current waveforms to affect the commanded bridge voltages of *all* bridges within each branch simultaneously, leading to high effective switching frequencies but requiring higher controller computational throughput. This method determines switch duty ratios based on commanded capacitor voltages, load voltages, branch voltages and reference quantities. Other control methods are also proposed in Akagi's work, based on other quantities such as branch currents and output currents. As proposed, these control methodologies require a centralized controller. A closely related version of the Phase-Shift PWM (PSPWM) scheme inherently balances capacitor voltages [92].

Angquist et al proposed the use of the common mode current, defined with respect to the dc supply side, to modulate capacitor voltages at the branch level [17]. An alternative method by the same authors was documented in [55, 56, 64], wherein the total branch capacitor voltage is estimated from the ac output current waveform rather than by measuring the voltages directly, and each individual capacitor voltage is controlled by comparing to this estimated total. Contrary to the method's naming, this system does comprise a closed loop control scheme. This research group has also proposed a modulation scheme that inherently balances the capacitor voltages [62]. Reference [89] proposes the use of physically different Voltage Correcting Modules to modulate the common mode current and Wang et al [93] propose a resonance-based approach to capacitor voltage control.

When mentioned, the vast majority of BoBC papers only present one or two fundamental bridge circuits. However, even though a large number of alternatives do exist, they are essentially absent from the literature. As of this writing, the few exceptions are: a fault tolerant bridge with a third switch [94], other fault tolerant designs [28], a 3level bridge [31], or a bridge using inductive energy storage [95]. Reed and Venkataramanan proposed a complementary variation to the two fundamental bridge circuits [76, 96], which will be described in Section 2.3.2.

Though these contributions have definite value and utility, as a whole they fall short of providing a complete and unified framework for the analysis and design of generalized BoBCs, particularly from the perspective of arbitrary ac phase numbers and buck/boost ratios. Another shortcoming of this body of literature is a clear understanding of the internal dynamics using an operating point model; despite their shortcomings, operating point models are well-understood and provide the design engineer with intuition regarding how design parameters can affect the converter dynamics. Nonlinear models and controls that can completely represent the converter, while sometimes useful, are inherently more complex and therefore tend to lack transparency, preventing the design engineer from truly understanding the underlying system.

To this end, the works of Ludois and Venkataramanan permit a more sophisticated understanding of the BoBC [41, 97, 98]. In fact, one salient point raised throughout their investigations is that a capacitor voltage control loop is not necessary because the BoBC behaves like a cascaded buck-boost converter, and the inner capacitor voltage is determined by the terminal duty ratios. While a very simple and powerful notion, these works did not investigate these behaviors beyond simple scalar converter modeling. Among other goals, this dissertation seeks to improve the understanding of BoBC dynamics and behavior by expanding on the modeling sophistication.

# 1.2 Objectives

The primary objective of this work is to present a generalized framework for modeling and analysis of dc-ac BoB power converters during PWM operation. This is divided into the following:

- 1. present and analyze the basic BoBC "building blocks,"

- 2. develop guidelines for the interconnection of building blocks,

- 3. propose a process for BoBC design,

- 4. propose a basic BoBC control methodology,

- 5. develop component stress models,

- 6. derive a low-frequency dynamic phasor model,

- 7. explore dynamic behavior of BoBC using phasor model,

- 8. extend modeling to converters with arbitrary numbers of levels,

- 9. demonstrate and validate the work for a single-phase dc-ac converter.

These objectives will be met using an appropriate combination of analytical, simulation and experimental methods.

# **1.3 Chapter overview**

Chapter 2 begins with the fundamental rules regarding the use of the BoBC "building blocks" and demonstrates through example how general BoBCs must operate based upon these rules. Two families of building blocks are then presented in detail, including their governing dynamic models, and the optimal building blocks for typical power converters are chosen.

Chapter 3 develops a converter-wide scalar steady-state model of the BoBC based on prior art and a small number of simplifying assumptions. A design process is presented and stress models for the capacitors and switches are developed along with the steadystate model and a simple nomogram-based method to determine suitable CSEBs for a given set of BoBC terminal characteristics. Capacitor sizing equations are also derived. An improved accuracy model is presented, which may be used when the simplifying assumptions are not valid. Frequency content of the steady-state model is investigated and a scalar closed loop current control methodology is presented to mitigate unwanted frequencies within the BoBC.

Chapter 4 develops a single-bridge dynamic phasor model of the BoBC using the dq coordinate system with dc components, which facilitates the converter's use in multiphase ac systems, particularly ac drives. Dynamic behavior is explored using small-signal stability analysis of eigenvalues and transfer functions over a range of closed loop controller gains.

Chapter 5 extends the single-bridge model to multiple levels, with examples of 2 and 3 series-connected bridges, and extensions to arbitrary numbers of bridges. Small-signal analysis demonstrates the scaling of eigenvalues as more bridges are added.

Chapter 6 validates the converter modeling presented throughout the previous chapters using a combination of simulation and experimental results using a laboratory-scale prototype converter. Detailed information is provided regarding both the design of the main power bridge components and the design and construction of the remaining hardware systems.

Chapter 7 concludes by summarizing all contributions and outlining the future work on the BoBC.

A variety of BoBC topologies may be constructed from a variety of "building blocks" called Q-cells. This chapter first describes the general motivation, concepts, and guidelines for developing BoBCs, with several generalized topology examples. Examples of various Q-cells which may be used to construct the converters are then presented and discussed.

# 2.1 **BoBC building blocks**

The bridge of bridge approach to power conversion may consist of branches of relatively small, 2-terminal power converter building blocks referred to as Q-cells (QCs). Briefly, the role of the Q-cell is to source and sink reactive power at multiple frequencies in order to control power flow; this role is further developed throughout this chapter. By combining Q-cells into branches comprising series strings and/or parallel arms, increased voltage blocking and/or current carrying capacity may be realized as illustrated in Fig. 2-1. Voltage blocking capability increases as the number of Q-cells in a series string increases or as more parallel arms are connected in series. Similarly, current handling capability increases as the number of parallel Q-cells in an arm, or as more series strings, are connected in parallel.

Fig. 2-1. Example branches consisting of series string and parallel arm configurations of Q-cells for realizing increased voltage blocking and/or current carrying capacity.

Furthermore, each Q-cell is assumed to be a closed system of components with only 2 power terminals – there are no separate power sources to source or sink real power. This statement carries with it the implication that **energy must be conserved within each Q-cell, i.e. Q-cells themselves cannot sink or source any real power** (aside from any converter losses). This property, hereby referred to as the Energy Conservation Constraint (ECC), is fundamental to all BoB power conversion systems and is developed throughout this thesis.

It is convenient to classify Q-cells with respect to their terminal characteristics in order to develop their interconnections. Instantaneous Q-cell power S(t) is defined as the product of the terminal voltage v(t) and current i(t),

$$S(t) = v(t)i(t).$$

2-1

In a regulated power conversion system, often one of the terminal quantities is established as the controlled variable and the other is the uncontrolled (but known/measured) variable. Of primary importance, then, is whether a Q-cell behaves as a

controllable voltage source, or as a controllable current source. In either case, the source ultimately behaves as a reactive power source because the ECC dictates that real power must be zero. In other words, a given Q-cell will have either a specified voltage across its terminals or a specified current through its terminals, in addition to sourcing the same amount of power that it sinks. Generic two terminal devices used in power converters are often described as being "voltage stiff" and "current stiff." The term "stiffness" signifies a quantity - voltage or current - that cannot be instantaneously changed in the twoterminal device. That is, a "current stiff" Q-cell maintains current flow through its two terminals, while a "voltage stiff" Q-cell maintains a voltage across its two terminals. These properties imply limitations on di/dt and dv/dt, not on i and v themselves. Indeed, Q-cells, in general, may exhibit certain stiffness characteristics due to their internal filter and/or energy storage components. Although it may be convenient to control voltages across voltage stiff Q-cells or current through current stiff Q-cells, such a feature is not absolutely essential in order to achieve power flow regulation. They are required, however, to have specified and/or controllable terminal characteristics regarding either voltage or current, free of net internal energy transfer. Thus, in describing the attributes and operation of BoBCs with arbitrary ratings, the Q-cells may be assumed to behave as ideal controllable voltage and/or current sources with infinite bandwidth.

Furthermore, interconnections of Q-cells along a branch within a BoBC must adhere to fundamental principles that arise from Kirchhoff's Voltage Law (KVL) and Kirchhoff's Current Law (KCL) that govern series and parallel operation. That is, similar to ordinary voltage and current sources, **Q-cells behaving as** *independent* controllable current sources may not be connected in series and Q-cells behaving as *independent* controllable voltage sources may not be connected in parallel. It is possible, however, to control an entire arm as a single voltage source, or an entire string as a single current source, without violating their fundamental properties. Besides this aspect, any number of Q-cells may be interconnected to form strings and/or arms. It is straightforward to see how the BoB approach inherently facilitates multilevel and modular architectures. The manner in which the Q-cell arms and strings can be effectively combined into fully functional BoBCs is discussed in the next section.

# 2.2 Evolution of the essential BoBC topological structure

A simple converter realized using a controlled current source branch to transfer power between two independent dc voltage sources is shown in Fig. 2-2a. Another perfectly valid example, albeit a less common one, would be a controlled voltage source connected in parallel (shunt) with two independent current sources, illustrated in Fig. 2-2b. That is, both cases exhibit controllable power flow. The former example is examined in-depth.

In the case of Fig. 2-2a, the controllable current source branch may comprise any combination of Q-cells in any configuration of series and/or parallel arms as long as the combination is ultimately a controlled current source. This simple primitive converter fails to operate successfully because net energy transfer between  $V_{dc1}$  and  $V_{dc2}$  can only occur when  $I_1$  also contains dc components. Since any practical converter will have  $V_{dc1} \neq V_{dc2}$ , then  $I_1$  will incur real power flow equal to  $P_{I1} = (V_{dc1} - V_{dc2})I_1$ , violating ECC.

Fig. 2-2. Primitive Case example A of power flow control using (a) a controllable current source  $I_1$ , or (b) a controllable voltage source  $V_1$ .

On the other hand, when one of the independent voltage sources is ac, as illustrated in Fig. 2-3, the instantaneous power absorbed by  $I_1$  may be expressed as the product of the voltage across the  $I_1$  branch and the total current through it,

$$S_{I1}(t) = \left(V_{dc} - \sqrt{2}V_{ac}\cos(\omega t)\right) \left(I_{dc} + \sqrt{2}I_{ac}\cos(\omega t + \phi)\right), \qquad 2-2$$

where the constants  $V_{dc}$  and  $I_{dc}$  represent the dc voltage and current;  $V_{ac}$  and  $I_{ac}$  represent the ac rms voltage and current; and  $\omega$  and  $\varphi$  represent the fundamental ac frequency and power factor angle, respectively.  $S_{I1}(t)$  can be simplified into the form  $S_{I1}(t) = P_{I1} + Q_{I1}(t)$ , where

$$P_{I1} = V_{dc}I_{dc} + V_{ac}I_{ac}\cos(\phi)$$

2-3

and

$$Q_{I1}(t) = \sqrt{2}V_{dc}I_{ac}\cos(\omega t + \phi) + \sqrt{2}I_{dc}V_{ac}\cos(\omega t) + V_{ac}I_{ac}\cos(2\omega t + \phi)$$

. 2-4

The real power component  $P_{I1}(t)$  may be made zero by maintaining a proper balance of dc and real ac power, while the reactive power  $Q_{I1}(t)$  must be provided internally by  $I_1$ . Even though the power transfer function between the independent voltage sources may be realized as appropriate, the sources  $V_{ac}$  and  $V_{dc}$  incur significant reactive power flow (ac current through  $V_{dc}$  and vice-versa), since the sum of both ac and dc components flow

Fig. 2-3. Primitive Case example B of power flow control using a controllable current-stiff source  $I_1$ .

through each source. This behavior is rather undesirable and may not be supported by the independent sources.

If both sources are ac, as shown in Fig. 2-4, the general case permits power flow control between the sources using  $I_1$ , although a special case exists when the ac source frequencies are equal but the magnitudes of the voltages and phase of the voltages are arbitrary. This is analogous to two single-phase ac voltage sources in series with an inductor – a familiar circuit to power engineering – where the real power flow is controlled by the phase difference and the reactive power flow is controlled by the difference magnitudes.

Fig. 2-4. Primitive Case example C of power flow control using a controllable current-stiff source  $I_1$ .

However, when the current-stiff source  $I_1$  is an arbitrary 2-terminal device instead of an inductor, the behavior is not as intuitive. With the definitions

$$i_1(t) = \sqrt{2I_1 \cos(\omega t + \varphi)}$$

2-5

$$v_{ac1}(t) = \sqrt{2}V_{ac1}\cos(\omega t)$$

2-6

$$v_{ac2}(t) = \sqrt{2}V_{ac2}\cos(\omega t + \theta), \qquad 2-7$$

the instantaneous power is expressed as

$$\begin{split} S_{i1}(t) &= \sqrt{2}I_1 \cos(\omega t + \phi) \Big[ \sqrt{2}V_{ac1} \cos(\omega t) - \sqrt{2}V_{ac2} \cos(\omega t + \theta) \Big] \\ &= 2V_{ac1}I_1 \cos(\omega t) \cos(\omega t + \phi) - 2V_{ac2}I_1 \cos(\omega t + \theta) \cos(\omega t + \phi) \\ &= V_{ac1}I_1 \Big[ \cos(2\omega t + \phi) + \cos(\phi) \Big] - V_{ac2}I_1 \Big[ \cos(2\omega t + \theta + \phi) + \cos(\phi - \theta) \Big] \\ &= V_{ac1}I_1 \Big[ \cos(\phi) - \frac{V_{ac2}}{V_{ac1}} \cos(\phi - \theta) \Big] \dots \\ &+ V_{ac1}I_1 \Big[ \cos(2\omega t + \phi) - \frac{V_{ac2}}{V_{ac1}} \cos(2\omega t + \phi + \theta) \Big] \end{split}$$

or  $S_{i1}(t) = P_{i1} + Q_{il}(t)$ , where

$$P_{i1} = V_{ac1}I_1 \left[\cos\left(\phi\right) - \frac{V_{ac2}}{V_{ac1}}\cos\left(\phi - \theta\right)\right]$$

2-9

and

$$Q_{i1}(t) = V_{ac1}I_1 \left[ \cos(2\omega t + \phi) - \frac{V_{ac2}}{V_{ac1}} \cos(2\omega t + \phi + \theta) \right].$$

2-10

By Eq. 2-9, real power  $P_{i1}$  can only be conserved when

$$\theta = \varphi - \cos^{-1} \left( \frac{V_{ac1}}{V_{ac2}} \cos(\varphi) \right).$$

2-11

When this condition is satisfied,  $S_{i1}$  becomes purely reactive.

Similar to the ac-dc power transfer case, this case also leads to significant reactive power transfer across the independent voltage sources, which is rather undesirable and may not be supported by the independent sources.

20

In order to overcome the problem of reactive power loading from the independent sources, a bridge configuration may be used. The circuit shown in Fig. 2-5 shows four controlled current-stiff source branches  $I_1$ - $I_4$ , in a full bridge configuration, which control power flow between  $V_{dc}$  and  $V_{ac}$ . The preceding discussion may be extended to show that such a configuration does not violate the ECC. This is also true when load and source are both ac but at different frequencies. Furthermore, the placement of dc and ac sources may readily be interchanged without violating the ECC.

Fig. 2-5. Case example D with BoBC formed by controllable current-stiff sources  $I_1 - I_4$ .

Fig. 2-6 illustrates the current components among the converter branches with dc current as dashed gray loops and the fundamental ac current as solid gray loops. In this topology, while the controlled current branches carry both dc and the fundamental ac frequency, the current through  $V_{dc}$  is only at dc – purely dashed – and the current though  $V_{ac}$  is only at the ac fundamental frequency – purely solid. This behavior may be accomplished through careful control of the converter branches.

Fig. 2-6. Current flow in example dc-ac BoBC

These examples illustrate the role of the controlled current branch, which provides energy storage capability at multiple frequencies simultaneously while sourcing or sinking zero real power. Specifically, in Fig. 2-5, each controlled current branch sinks a specified amount of real power at dc while also sourcing the same amount of real power at the ac fundamental frequency to the load. This results in a net loss of real power in  $V_{dc}$ and a net gain of real power in  $V_{ac}$ . In other words, the power flow within the BoBC itself is purely reactive. As such, the amount of energy storage required for a given application is a function of how much power throughput is required and the frequencies at which the reactive power flows.

It is well-known in power engineering that bulk capacitors and inductors tend to decrease in size as the ac operating frequency increases due to a decreasing amount of energy stored per ac half-cycle. High ac frequencies are often desirable in BoBCs for the same reason, which effectively reduces energy storage requirements within the Q-cells. While conventional high-power converters utilize large components with significant parasitic elements, which limit operation to low ac frequencies, the BoBC is less

vulnerable to this frequency limitation; its multilevel and modular architecture permits the use of many lower-power converters built from smaller components with much smaller parasitic elements and therefore are capable of operating at significantly higher ac frequencies. This results in high-power, high-frequency converter designs with minimal internal energy storage, and is a key advantage of the BoBC topologies over conventional designs when the fundamental ac frequency is a free design parameter.