## Energy-Efficient Domain Specific Architectures: Design Space Exploration, Algorithms and FPGA Prototyping

By

### Anish Nallamur Krishnakumar

A dissertation submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

(Electrical and Computer Engineering)

at the

UNIVERSITY OF WISCONSIN-MADISON

2022

Date of final oral examination: 12/05/2022

The dissertation is approved by the following members of the Final Oral Committee:

Umit Y. Ogras, Associate Professor, Electrical and Computer Engineering, University of Wisconsin-Madison

Yu-Hen Hu, Professor, Electrical and Computer Engineering, University of Wisconsin-Madison

Matthew Sinclair, Assistant Professor, Computer Sciences, University of Wisconsin-Madison

Chaitali Chakrabarti, Professor, Electrical, Computer and Energy Engineering, Arizona State University

Dedicated to my parents Annapurna and Krishnakumar, in-laws Rajalakshmi and Gopal, brother Adarsh, and my wife Reshmi. First and foremost, I extend my deepest gratitude to my advisor, Prof. Umit Y. Ogras, for the exemplary guidance, advice, and encouragement he has offered me throughout my Ph.D. journey. His insightful thoughts and recommendations have helped me solve several challenges I faced during my studies. Specifically, his advice on organizing thoughts and writing research papers, developing simulators, time management, and, most importantly, enabling me to develop the ability to perform independent research will help me a long way in my career ahead. I cherish the bond we have developed over the years and am sure it will continue beyond my journey at the University of Wisconsin-Madison.

I am immensely thankful to Prof. Yu-Hen Hu, Prof. Matthew Sinclair, and Prof. Chaitali Chakrabarti for taking the time to serve on my Ph.D. defense committee. Their suggestions and feedback have been invaluable in improving the quality of my research and this dissertation.

I sincerely thank Prof. Chaitali Chakrabarti, Prof. Radu Marculescu, and Prof. Ali Akoglu for our insightful research discussions over the years. I greatly value their collaboration, suggestions, and feedback. I also extend my sincere thanks to Prof. Daniel Bliss, Prof. David Blaauw, Prof. Trevor Mudge, Prof. Hun-Seok Kim, Prof. Ronald Dreslinski, and Brittany McCall for their input and support during my research.

I am grateful for the exciting discussions, words of encouragement, and lighter moments with friends and colleagues at eLab: Dr. Samet Arda, Prof. Ganapati Bhat, Prof. Sumit Mandal, Shruti Narayana, Yigit Tuncel, Sizhe An, Alper Goksoy, Toygun Basaklar, Vishrut Pandey, Jie Tong, Nuriye Yildirim, Aditya Ukarande, and Conrad Holt. I also thank colleagues and friends at other universities: Dr. Tutu Ajayi, Dr. Hanguang Yu, Dr. Alex Chiriyath, Dr. Arindam Dutta, Joshua Mack, Sahil Hassan, Serhan Gener, Alexander Fusco, Ilkin Aliyev, Xing Chen, Adarsh Akkshai Venkataramani, and Kuan-Yu Chen.

At this juncture, I thank Nagadastagiri Challapalle, who motivated me to pursue a Ph.D. and has been a constant pillar of support for over five years. I thoroughly

enjoyed the words of encouragement and lighter moments with my friends; at Madison: Sneha Chavali, Srinath Namburi, Akhil, Bodduppalli, Srinivas Pothuraju, Siddharth RCS, Ramakrishna Raju, Rahim Shaik, and Indu Kilaru; at Arizona: Surya Golkonda, Yashasvi Reddy, Naga Venkatesh, Aswin Baskaran, and Medhini Vuyyuru; Ranjith Kumar, Makesh Tarun and Raghuraj Krishnamurthy; at India: Vijay Vigneshan, Praveen Kumar, Sona Aishwarya, Rajesh Ganesan, Rajbarath, Jatin Kumar, Kajal Luthra, Anupam Sobti and Shruti Sharma.

I am thankful to Defense Advanced Research Projects Agency (Grant FA8650-18-2-7860) for funding the research presented in this dissertation. My deepest gratitude goes to Prof. Moorthi Sridharan, Prof. Selvan M.P, and Prof. Raja Pitchaimuthu for planting the seeds of pursuing a research career during my undergraduate days.

Finally, this would not have been possible without the support of my parents, Annapurna and Krishnakumar, in-laws Rajalakshmi and Gopal, my brother Adarsh, and my family. Their love, support, and encouragement have been of immense support in this journey. Finally, I am deeply grateful to my loving wife Reshmi, whose unconditional support and immense sacrifice have enabled me to complete this journey seamlessly.

#### **CONTENTS**

| _          |            |      |      |    |

|------------|------------|------|------|----|

| <i>^</i> ' |            |      | nts  | •  |

|            | $\alpha$ n | 1721 | nte. | 1V |

|            |            |      |      |    |

List of Tables vi

List of Figures viii

### Abstract xiv

- **1** Introduction 1

- 1.1 Contributions 5

- **2** Literature Review 9

- 2.1 Research Directions in Domain-Specific Architectures 9

- 2.2 Evaluation Frameworks for DSAs 14

- 2.3 Resource Management Techniques for Heterogeneous Architectures 19

- 2.4 Incremental and Online Updates to Decision Tree Classifiers 27

- 3 DS3: A Domain-Specific System-on-Chip Simulation Framework 30

- 3.1 Background, Motivation and Contributions 30

- 3.2 Overall Goals and Architecture 33

- 3.3 Developer View: DS3 Implementation 35

- 3.4 User View: DS3 Capabilities 41

- 3.5 Simulator Validation 46

- 3.6 Application Case Studies 51

- 4 Imitation Learning Based Task Scheduling for Heterogeneous Systems 66

- 4.1 Background, Motivation and Contributions 66

- 4.2 Overview 71

- 4.3 Proposed Methodology and Approach 75

- 4.4 Experimental Results 82

- 5 Optimization Techniques for Decision Tree Classifier Implementation 105

- 5.1 Background, Motivation and Contributions 105

- 5.2 Hardware Architecture and Evaluation of DT Classifiers 107

- 5.3 Proposed Software Optimization Approaches for DT Classifiers 110

- 5.4 Experimental Results112

- 6 Incremental and Online Updates to Decision Tree Classifiers114

- 6.1 Background, Motivation and Contributions114

- 6.2 An Overview of Decision Tree Classifiers and Assumptions 117

- 6.3 INDENT: Incremental Online DT Training122

- 6.4 Experimental Evaluation 129

- 7 FPGA-based Emulation Framework for Domain-Specific Architectures 139

- 7.1 Background, Motivation and Contributions 139

- 7.2 The FALCON Architecture 141

- 7.3 Demonstrations using FALCON143

- 7.4 Enabling Software and Driver Development 155

- 8 Conclusions and Future Directions 157

- 8.1 Future Directions 159

Bibliography 161

## LIST OF TABLES

| 2.1 | Comparing INDENT with prior work on DT training                                                                                         | 29       |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------|----------|

| 3.1 | List of PE attributes in resource database                                                                                              | 36       |

| 3.2 | Execution times of the tasks on the different PEs for the representative example                                                        | 42       |

| 3.3 | Error percentages in comparison of execution time, power and temperature between DS3 and Odroid-XU3                                     | 48       |

| 3.4 | Execution time profiles of applications on Arm A53 core in Xilinx ZCU102,                                                               |          |

| 3.5 | Arm A7/A15 cores in Odroid-XU3, and hardware accelerators Execution time of applications in benchmark suite with different schedulers   | 52<br>57 |

| 3.6 | Area, performance and energy for different SoC configurations with                                                                      | 0.       |

|     | varying number of accelerators                                                                                                          | 58       |

| 4.1 | Summary of the notations used in the IL-based task scheduling approach                                                                  | 75       |

| 4.2 | Types of features employed for state representation from point of view of task $T_j$                                                    | 78       |

| 4.3 | Characteristics of applications used in this study and the number of                                                                    | 70       |

| 1.0 | frames of each application in the workload                                                                                              | 83       |

| 4.4 | Classification accuracies of trained IL policies with different machine                                                                 |          |

| 4.5 | learning classifiers                                                                                                                    | 87       |

| 4.5 | neural network classifiers                                                                                                              | 87       |

| 4.6 | Training accuracy of IL policies with subsets of the proposed feature set                                                               | 90       |

| 4.7 | Standard deviation (in percentage of execution time) profiling of appli-                                                                |          |

|     | cations in Odroid-XU3 and Zynq ZCU-102                                                                                                  | 96       |

| 4.8 | Configuration of many-core platforms                                                                                                    | 97       |

| 5.1 | Table showing the communication latencies of data transfers for the DT accelerator (depth 4) implementation in the ZCU102 FPGA with the |          |

|     | Arm cores operating at 1.2 GHz and accelerator operating at 300 MHz.                                                                    | 110      |

| 6.1 | A summary of symbols used in INDENT                                             | 118 |

|-----|---------------------------------------------------------------------------------|-----|

| 6.2 | The list of all input features for each task and the specific order of features |     |

|     | enforced by INDENT to allow incremental updates when new clusters               |     |

|     | are added                                                                       | 121 |

| 6.3 | Table summarizing the workload and SoC configuration scenarios used             |     |

|     | for the evaluation of INDENT. The bold text denotes the new processing          |     |

|     | clusters or applications                                                        | 131 |

| 7.1 | Comparison of Hardware Performance Counter Values between Two                   |     |

|     | Different Software Implementations of Matrix Multiplication in VCU128           |     |

|     | operating at a frequency of 32 MHz                                              | 146 |

## LIST OF FIGURES

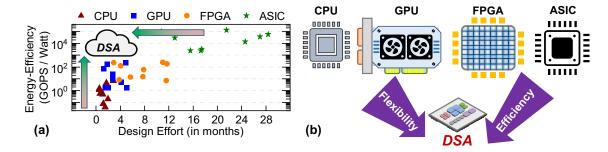

| 1.1 | (a) Trends in energy efficiency and design effort in Giga operations per Watt (GOPS / Watt) for applications implemented on CPU, GPU, FPGA, and fixed-function/special-purpose ASIC. (b) An illustration of domain-specific architecture (DSA) combining the flexibility benefits of CPU and GPU implementations, the performance benefits of FPGA, and the energy efficiency of fixed-function ASIC implementations        | 2        |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

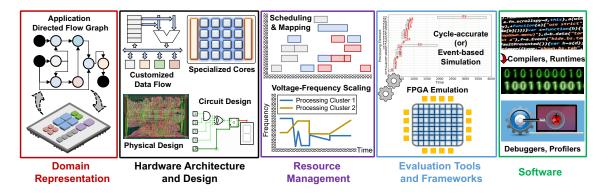

| 2.1 | Prime research directions in the conceptualization, design and development of DSAs. Applications are represented as directed flow graphs. The nodes in the graph represent the key computational kernels within each application and the edges of the graph denote the communication volumes between kernels.                                                                                                               | 10       |

| 2.2 | Interactions between the research directions for the realization of DSAs. The kernel and flow graph information of domain applications and target metrics drive the hardware architecture and design of PEs. The application and hardware PE information is exploited by the resource management techniques. The DSA configurations are evaluated for functionality and performance using simulators, emulation frameworks, | 10       |

| 2.3 | and the software stack                                                                                                                                                                                                                                                                                                                                                                                                      | 12<br>21 |

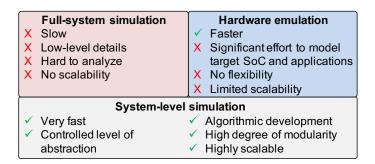

| 3.1 | Common DSE methodologies with their advantages and disadvantages.                                                                                                                                                                                                                                                                                                                                                           | 31       |

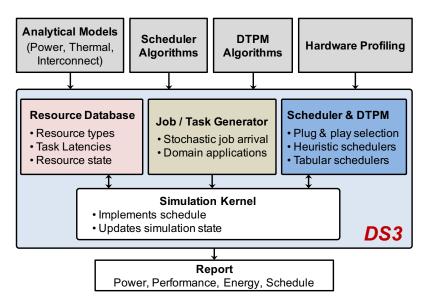

| 3.2 | Organization of DS3 framework describing the inputs and key functional                                                                                                                                                                                                                                                                                                                                                      | 01       |

|     | components to perform rapid design space exploration and validation.                                                                                                                                                                                                                                                                                                                                                        | 34       |

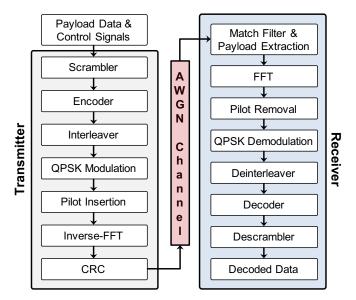

| 3.3 | Block diagrams for WiFi-TX and WiFi-RX applications                                                                                                                                                                                                                                                                                                                                                                         | 37       |

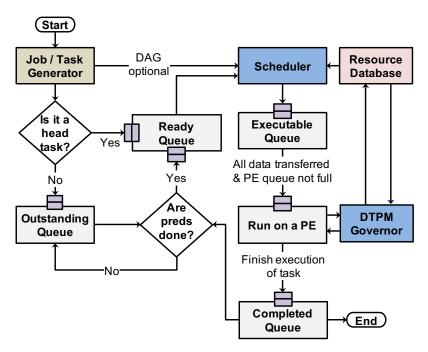

| 3.4 | Life-cycle of a task in DS3 queues                                                                                                                                                                                                                                                                                                                                                                                          | 39       |

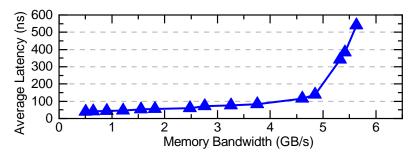

| 3.5  | Bandwidth-Latency curve used to model DRAM latency in DS3 framework.                    | 40 |

|------|-----------------------------------------------------------------------------------------|----|

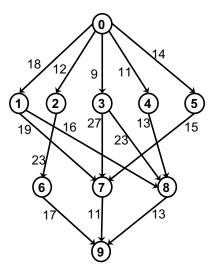

| 3.6  | A canonical task flow graph [1] with 10 tasks. Each node represents                     |    |

|      | a task and each edge represents average communication cost across                       |    |

|      | the available pool of PEs for the pair of nodes sharing that edge. The                  |    |

|      | computation cost table on the right indicates the execution time for each               |    |

|      | of the PEs                                                                              | 42 |

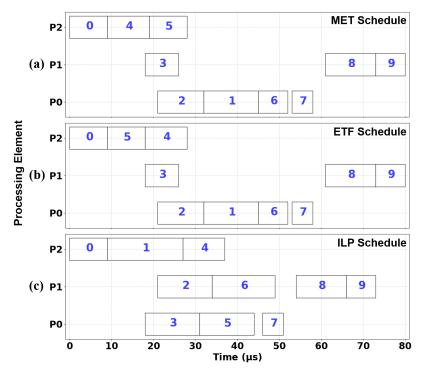

| 3.7  | Schedule of task graph in Figure 3.6 with (a) MET, (b) ETF, and (c) CP.                 | 43 |

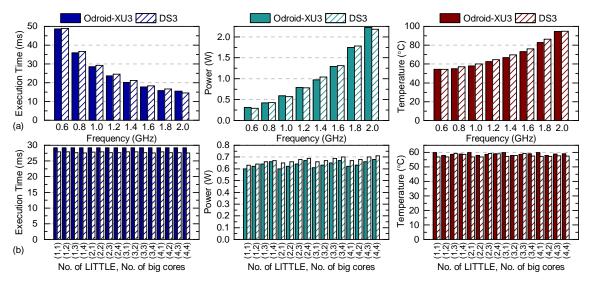

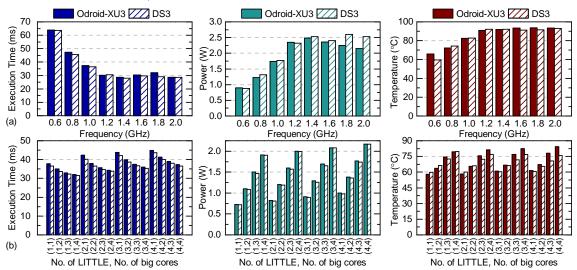

| 3.8  | Comparison of execution time, power and temperature between DS3                         |    |

|      | and Odroid-XU3 for single-threaded applications when (a) Freq-Sweep:                    |    |

|      | Number of cores is constant, frequencies of the cores are varied (b)                    |    |

|      | Core-Sweep: Frequencies of cores are constant, number of cores is varied.               | 47 |

| 3.9  | Comparison of execution time, power and temperature between DS3                         |    |

|      | and Odroid-XU3 for multi-threaded applications when (a) Freq-Sweep:                     |    |

|      | Number of cores is constant, frequencies of the cores are varied (b)                    |    |

|      | Core-Sweep: Frequencies of cores are constant, number of cores is varied.               | 47 |

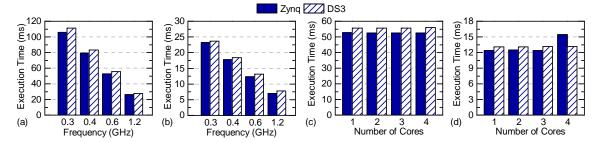

| 3.10 | Comparison of execution time between DS3 and Zynq MPSoC when (a)                        |    |

|      | Freq-Sweep with only Cortex A53 cores, (b) Freq-Sweep with Cortex A53                   |    |

|      | cores and hardware accelerators (c) Core-Sweep with only Cortex A53                     |    |

|      | cores, (d) Core-Sweep with Cortex A53 cores and hardware accelerators.                  | 50 |

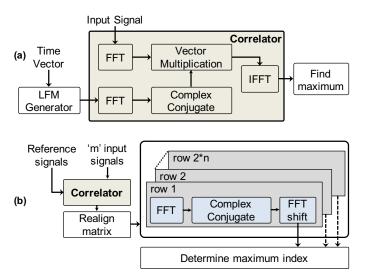

| 3.11 | Block diagram of (a) range detection application, (b) pulse Doppler                     |    |

|      | application where $m$ is number of signals and $n$ is number of samples                 |    |

|      | for a signal                                                                            | 53 |

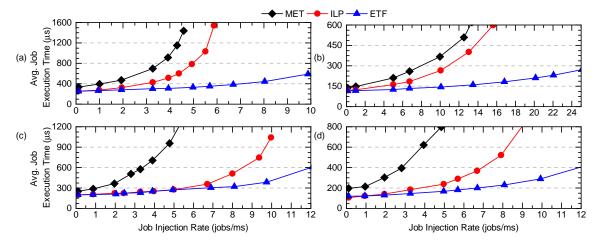

| 3.12 | Results from different schedulers with a workload consisting of (a)                     |    |

|      | WiFi-TX ( $p_{TX}$ =0.2) and WiFi-RX ( $p_{RX}$ =0.8), (b) WiFi-TX ( $p_{TX}$ =0.8) and |    |

|      | WiFi-RX ( $p_{RX}$ =0.2), (c) range detection ( $p_{range}$ =0.8) and pulse Doppler     |    |

|      | $(p_{pulse}=0.2)$ , (d) WiFi-TX $(p_{TX}=0.3)$ , WiFi-RX $(p_{RX}=0.3)$ , range detec-  |    |

|      | tion ( $p_{range}=0.3$ ), and pulse Doppler ( $p_{pulse}=0.1$ )                         | 56 |

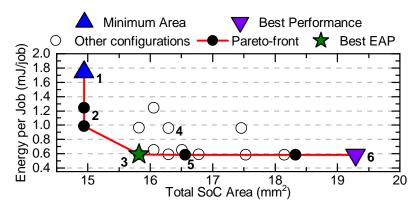

| 3.13 | Design space exploration studies showing energy per job vs. SoC area                    |    |

|      | with pareto-frontier                                                                    | 59 |

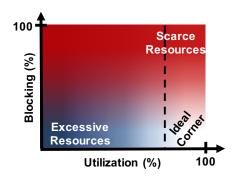

| 3.14 | PE blocking vs utilization (2-D performance plane)                                      | 60 |

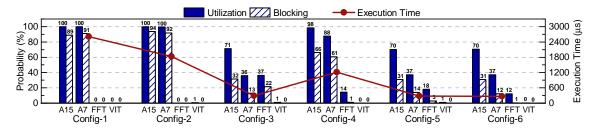

| 3.15 | Utilization vs blocking for PE clusters in representative configurations       |   |

|------|--------------------------------------------------------------------------------|---|

|      | with average job execution times                                               | 6 |

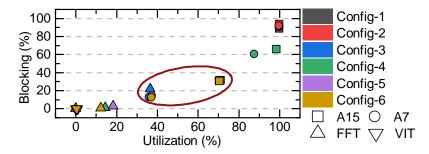

| 3.16 | Results for representative configurations on 2-D performance plane for         |   |

|      | PE clusters                                                                    | 6 |

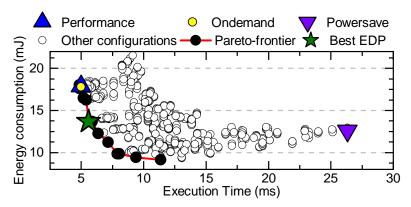

| 3.17 | Pareto frontier in the energy-performance curve for an SoC with 16             |   |

|      | processing elements (PEs) executing a representative workload                  | 6 |

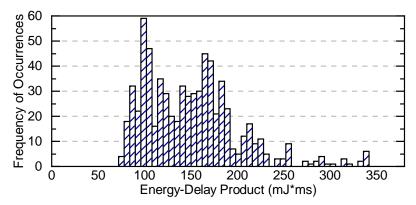

| 3.18 | Energy-Delay Product (EDP) histogram                                           | 6 |

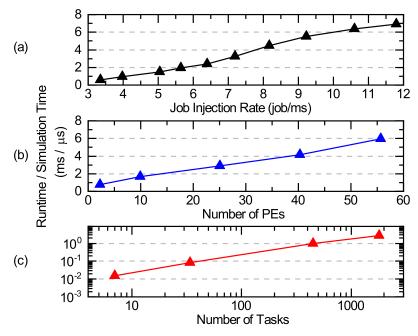

| 3.19 | Results for scalability analysis showing DS3 runtime versus (a) Different      |   |

|      | job injection rates, (b) Varying SoC configurations and (c) Number of          |   |

|      | tasks executed                                                                 | 6 |

| 4.1  | (a) An example DAG consisting of 7 tasks (b) A heterogeneous com-              |   |

|      | puting platform with 4 processing elements and list of tasks in DAG            |   |

|      | supported by each PE (c) A sample schedule of the DAG on the hetero-           |   |

|      | geneous many-core system                                                       | 7 |

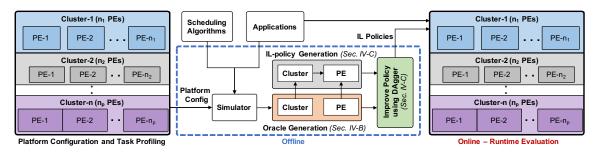

| 4.2  | An overview of the proposed imitation learning framework for task              |   |

|      | scheduling in heterogeneous many-core systems. The framework in-               |   |

|      | tegrates the system configuration, profiling information, scheduling           |   |

|      | algorithms and applications to construct Oracle, and train IL policies         |   |

|      | for task scheduling. The IL policies, that are improved using DAgger,          |   |

|      | are then evaluated on the heterogeneous many-core system at runtime.           | 7 |

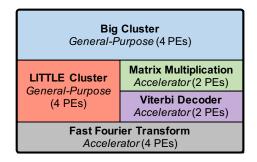

| 4.3  | Configuration of the heterogeneous many-core platform comprising 16            |   |

|      | processing elements, used for scheduler evaluations                            | 8 |

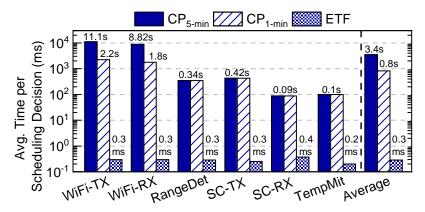

| 4.4  | A comparison of average runtime per scheduling decision for each ap-           |   |

|      | plication with $CP_{5-min}$ , $CP_{1-min}$ and ETF schedulers                  | 8 |

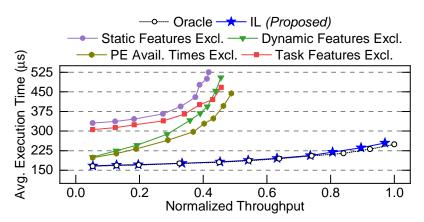

| 4.5  | Average execution time comparison of the applications with Oracle,             |   |

|      | IL ( <i>Proposed</i> ) and IL policies with subsets of features. As shown, the |   |

|      | average execution time with IL closely follows the Oracle                      | 8 |

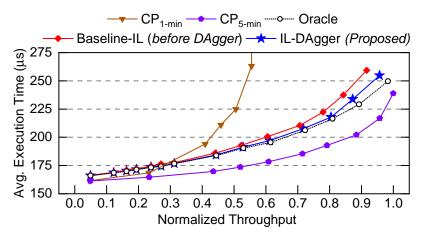

| 4.6  | Comparison of average job execution time between Oracle, CP solutions,    |     |

|------|---------------------------------------------------------------------------|-----|

|      | and imitation learning policies to schedule a workload comprising a       |     |

|      | mix of six streaming applications. IL scheduler policies with baseline-   |     |

|      | IL (before DAgger) and with IL-DAgger (Proposed) are shown in the         |     |

|      | comparison                                                                | 91  |

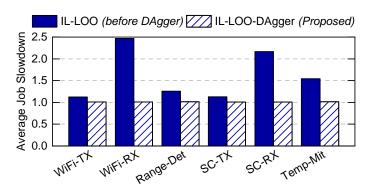

| 4.7  | Average slowdown of IL policies in comparison with Oracle for leave-      |     |

|      | one-out (LOO) experiments before and after DAgger ( <i>Proposed</i> )     | 93  |

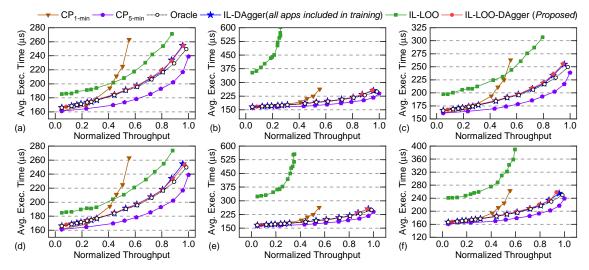

| 4.8  | Average execution time with Oracle, IL-DAgger (all applications are in-   |     |

|      | cluded for training), IL with one application excluded from training (IL- |     |

|      | LOO) and finally, the leave-one-out policy improved with DAgger (Pro-     |     |

|      | posed IL-LOO-DAgger) technique. The excluded applications are: (a)        |     |

|      | WiFi-TX, (b) WiFi-RX, (c) Range Detection (d) Single-Carrier TX (e)       |     |

|      | Single-Carrier RX and (f) Temporal Mitigation                             | 95  |

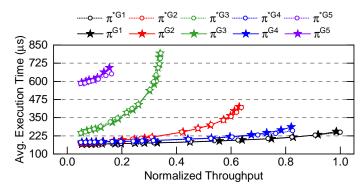

| 4.9  | IL policy evaluation with multiple many-core platform configurations.     |     |

|      | IL policies are trained with only configuration G1                        | 97  |

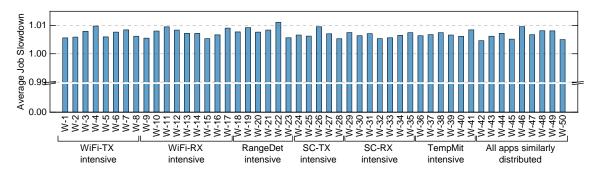

| 4.10 | Comparison of average job slowdown normalized with IL-DAgger (Pro-        |     |

|      | posed) policies against the Oracle for 50 different workloads. The slow-  |     |

|      | down of IL-DAgger policies are shown for workloads with different         |     |

|      | <i>intensities</i> of each application in the benchmark suite             | 99  |

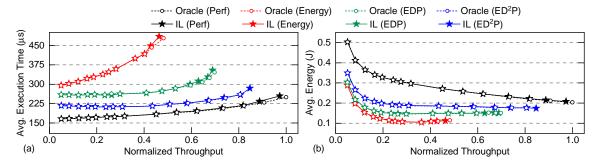

| 4.11 | (a) Average execution time and (b) average energy consumption of the      |     |

|      | workload with Oracles and IL policies for performance, energy, energy-    |     |

|      | delay product (EDP) and energy-delay $^2$ product (ED^2P) objectives.<br> | 100 |

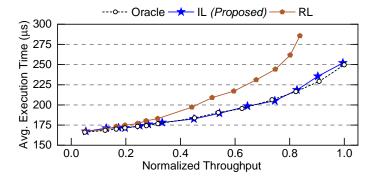

| 4.12 | Comparison of average execution time between Oracle, IL, and RL poli-     |     |

|      | cies to schedule a workload comprising a mix of six streaming real-world  |     |

|      | applications                                                              | 101 |

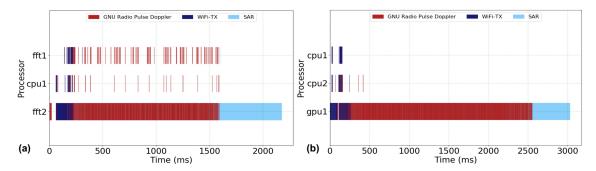

| 4.13 | Gantt charts of the workload execution on (a) Xilinx Zynq ZCU102          |     |

|      | FPGA and (b) Jetson AGX Xavier for a workload comprising the GNU          |     |

|      | Radio Pulse Doppler, WiFiTX and SAR applications                          | 104 |

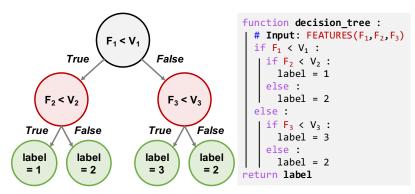

| 5.1  | An illustration of a decision tree of maximum depth 2 (left) and its      |     |

|      | corresponding pseudo code for classification ( <i>right</i> )             | 106 |

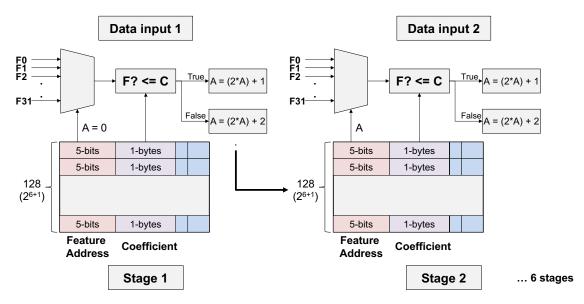

| 5.2 | Proposed microarchitecture for DT classifier acceleration in hardware.     | 108  |

|-----|----------------------------------------------------------------------------|------|

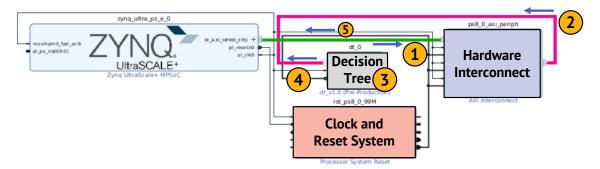

| 5.3 | Schematic of the hardware components for DT accelerator implemen-          |      |

|     | tation in ZCU102 FPGA. The numbered circles indicate the computa-          |      |

|     | tion and communication steps involved in sending and receiving data        |      |

|     | from/to the accelerator                                                    | 109  |

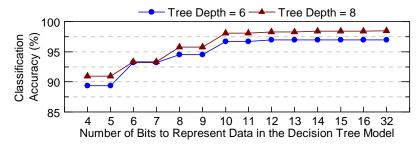

| 5.4 | Effect of number of bits on the classification accuracy (Fixed-point: 4–16 |      |

|     | bits, single-precision floating point: 32 bits)                            | 111  |

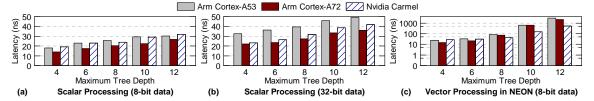

| 5.5 | Latencies of decision tree classifiers for varying tree depths on Arm      |      |

|     | Cortex-A53, Arm Cortex-A72 and Nvidia Carmel cores with (a) scalar         |      |

|     | processing using 8-bit data, (b) scalar processing with floating-point     |      |

|     | (32-bit) data, and (c) vector processing in NEON using 8-bit data          | 112  |

| 5.6 | Transformation of sequential decision tree code into NEON-friendly         |      |

|     | code for SIMD processing                                                   | 113  |

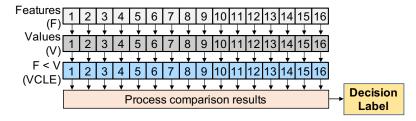

| 6.1 | An example of a decision tree (DT) classifier showing the root, interme-   |      |

|     | diate, and the leaf nodes                                                  | 118  |

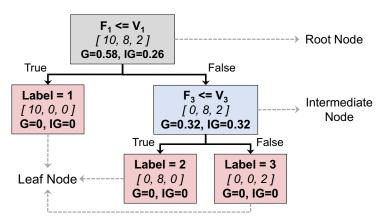

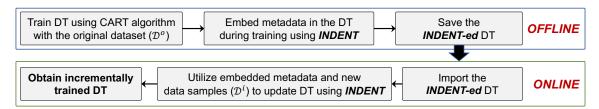

| 6.2 | An overview of the INDENT flow to incrementally train DTs online           | 122  |

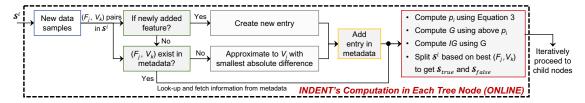

| 6.3 | Block diagram describing the computation in INDENT's online phase          |      |

|     | to incrementally update a DT node                                          | 125  |

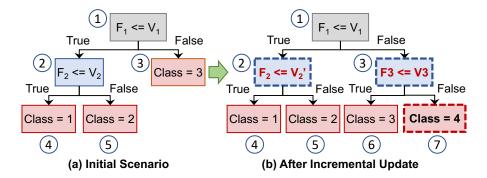

| 6.4 | A canonical example showing the (a) initial and (b) incrementally up-      |      |

|     | dated DT. The incremental update may change decision criteria in nodes     |      |

|     | (node 2), expand nodes (node 3) and introduce new leaf nodes (node 7)      | .128 |

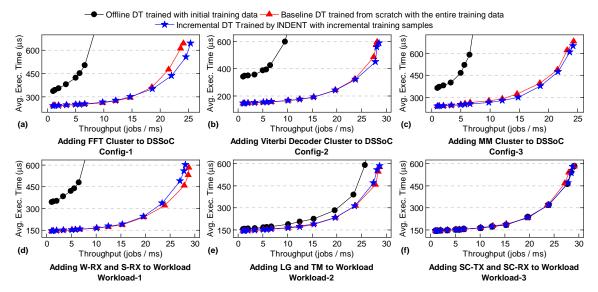

| 6.5 | The incremental DT trained using INDENT (* marker) by updating the         |      |

|     | initial DT (• marker) performs very close to the DT trained from scratch   |      |

|     | with the entire training data ( $\blacktriangle$ marker)                   | 132  |

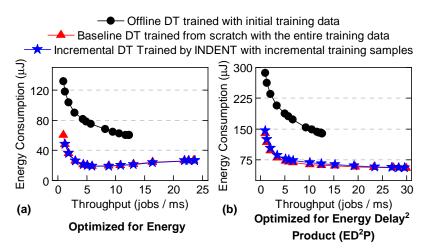

| 6.6 | Energy comparison of INDENT DTs optimized for energy (a) and               |      |

|     | $ED^{2}P$ (b) for workload-1 against a baseline DT                         | 135  |

|     |                                                                            |      |

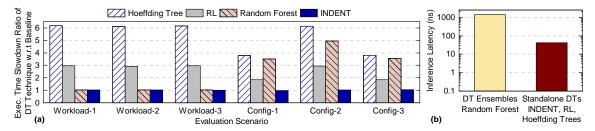

| 6.7 | (a) Comparison of average execution time slowdown ratio of Hoeffding    |      |

|-----|-------------------------------------------------------------------------|------|

|     | Tree [2], RL [3], Random Forest (DT Ensemble) [4] and INDENT (our       |      |

|     | proposed approach) with respect to the baseline DT trained from scratch |      |

|     | with the entire training data. (b) Comparison of inference latencies    |      |

|     | measured on the Jetson Xavier NX hardware platform of DT ensemble       |      |

|     | (random forest [4]) and standalone DTs (such as INDENT, RL [3] and      |      |

|     | Hoeffding trees [2])                                                    | 137  |

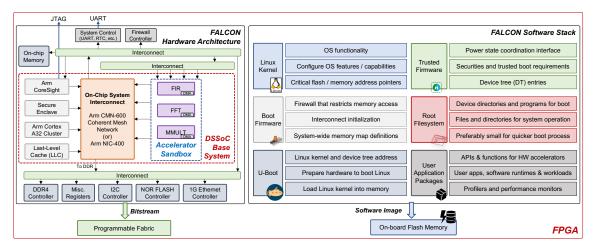

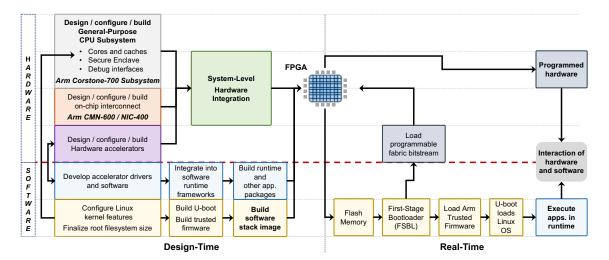

| 7.1 | An overview of the key components and organization of the FALCON        |      |

|     | framework for DSSoC emulation on FPGAs. The hardware architecture       |      |

|     | and design (shown on the left) is programmed as a bitstream onto        |      |

|     | the programmable fabric. The software image (shown on the right) is     |      |

|     | programmed to the on-board flash memory                                 | 141  |

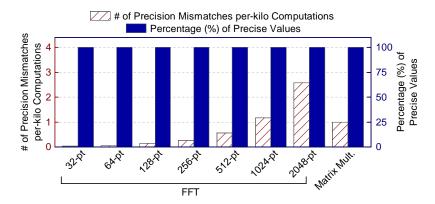

| 7.2 | The number of precision mismatches (primary axis) per-kilo compu-       |      |

|     | tations and the percentage of precise values (secondary axis) of the    |      |

|     | FFT and matrix multiplication hardware accelerators with respect to a   |      |

|     | reference software implementation in VCU128                             | 144  |

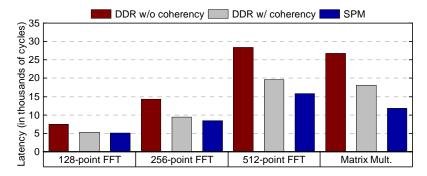

| 7.3 | A comparison of the hardware accelerator latencies (in thousands of cy- |      |

|     | cles) when data is transferred through DDR memory (with and without     |      |

|     | coherency) and the on-chip scratchpad memory (SPM) in VCU128            | 145  |

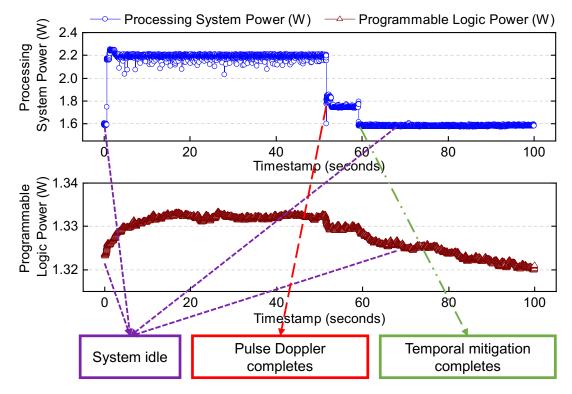

| 7.4 | An illustration of power consumption in the processing system (Arm      |      |

|     | Cortex-A53 cores operating at 1.2 GHz) and programmable fabric (hard-   |      |

|     | ware accelerators operating at 100 MHz) in a Zynq UltraScale+ ZCU102    |      |

|     | FPGA                                                                    | 147  |

| 7.5 | A timeline of the hardware development process and the boot sequence    |      |

|     | in software for a DSSoC emulated by the proposed FALCON framework       | .151 |

|     | • • •                                                                   |      |

#### **ABSTRACT**

The saturation of Moore's Law has stalled the improvement in performance and energy efficiency obtained with conventional homogeneous processors over technology nodes. Homogeneous processors cannot cater to the contrasting performance and energy requirements of different applications, leading to the rise of heterogeneous computing architectures. While heterogeneous processors provide programming flexibility, there is still a steep performance and energy-efficiency gap compared to special-purpose solutions. However, combining all kinds of processing elements in a single chip leads to a severe penalty in design cost, chip area, and poor utilization at runtime. To address all the above challenges, domain-specific architectures (DSAs) judiciously combine processing elements such as general-purpose cores, special-purpose cores, and hardware accelerators to maximize the energy efficiency of domain applications and provide programming flexibility.

The major challenge in DSAs is to optimally utilize the diverse processing elements at runtime to exploit their potential. Mapping tasks to the processing elements (task scheduling) and controlling their voltage and frequencies are critical aspects of resource management. To this end, we pose task scheduling as a classification problem and propose a novel offline imitation learning framework and decision tree (DT) classifiers. Our imitation learning-based scheduling policy achieves performance that is within 1% of an Oracle for multiple optimization objectives and SoC configurations. The offline-trained scheduling policies become ineffective when new applications or processing clusters are introduced in the workload; hence, they must be updated online. DTs pose an additional challenge in online training since they use the entire dataset. To address this challenge, we propose an incremental and online lightweight training framework for DTs that achieves a performance within 5% of a baseline DT by storing only 1-8% of the original dataset. To support the rapid exploration and evaluation of resource management algorithms, we developed a high-level discrete-event full-system simulation framework that models the processing elements, scheduling pipeline, and other components of the system. We also developed an FPGA-based prototyping and emulation framework to enable functional validation and early software development. This dissertation addresses critical challenges in DSA runtime resource management and evaluation frameworks that accelerate their design and development for mainstream adoption.

#### 1 INTRODUCTION

Process technology-driven power, performance, and energy efficiency improvements have recently slowed down significantly [5, 6]. In addition, performance cannot be further improved by scaling the frequency arbitrarily due to the power wall [7, 8]. Consequently, two primary drivers of higher performance-per-watt cease to provide the expected gains. At the same time, the instruction-level parallelism techniques, such as processor pipelining, prefetching, and out-of-order execution, provide only marginal benefits, thereby leaving a substantial scope for improvement in performance and energy efficiency [9].

Homogeneous multicore architectures integrate multiple identical cores onto the same die to provide higher computational capabilities under similar area budgets [10, 11]. They opened new avenues to parallel processing capabilities with higher performance at a modest power consumption increase, thereby allowing drastic energy efficiency improvements [12]. However, homogeneous cores cannot simultaneously satisfy competing application requirements, such as low power and high performance. Low-power cores, such as the Arm Cortex-M series, have limited performance. In contrast, high-performance cores, such as the Arm Cortex-A72/A76 processors, consume higher power due to the out-of-order execution nature, large caches, and deep execution pipelines. Heterogeneous multiprocessor architectures address this problem by integrating low-power and high-performance cores [13, 14]. Therefore, heterogeneous architectures are extensively used in most processing systems, such as mobile phones, laptops, desktops, and servers [15, 16, 17].

Heterogeneous architectures significantly improve performance and energy

Figure 1.1: (a) Trends in energy efficiency and design effort in Giga operations per Watt (GOPS / Watt) for applications implemented on CPU, GPU, FPGA, and fixed-function/special-purpose ASIC. (b) An illustration of domain-specific architecture (DSA) combining the flexibility benefits of CPU and GPU implementations, the performance benefits of FPGA, and the energy efficiency of fixed-function ASIC implementations.

efficiency compared to their homogeneous counterparts. However, they still have a substantial gap with application-specific integrated circuits (ASIC). To provide a quantitative comparison, Figure 1.1(a) shows the energy efficiency of applications implemented on CPU, GPU, FPGA, and ASIC. CPU implementations require the least design effort and also provide low energy efficiency [18]. GPUs and FPGAs improve energy efficiency and performance by exploiting single-instruction multiple data (SIMD) execution and parallelism benefits, respectively [19, 20]. Application code is converted to GPU-compatible code to run on GPUs, and hardware description languages or high-level synthesis for FPGAs. ASICs provide the highest energy efficiency since they are specifically designed for the target application [21]. However, the ASIC effort, which includes design, development, fabrication, and software development could require several months to years. Therefore, there is a critical need to continue the evolution of computing architectures to provide

ASIC-like energy efficiency with the shortest possible time-to-market.

Domain-specific architectures represent an emerging instance of heterogeneous architectures that optimize data flow for applications in a target domain through hardware acceleration while providing programming flexibility [22, 23, 24, 25]. Examples of recently growing domains include wearable and human activity recognition for health monitoring, machine learning and artificial intelligence (AI), autonomous driving, and software defined radios [26, 27, 28, 29, 30, 23]. For instance, machine learning and AI are extensively being used for image processing, scheduling, recommendation systems, spam filtering, stock market analysis, video analytics, and medical applications [31, 32, 33, 34, 35, 29, 36, 37, 38]. Hence, there is a strong need for computing architectures that enable seamless, high-performance, and energy-efficient execution of these domain applications. DSAs aim at improved programmability by including general-purpose cores and the highest energy efficiency by integrating special-purpose processors and hardware accelerators. The domain-specific nature of DSAs stems from the fact that the hardware accelerators (e.g., as [39, 40]) and data flows are highly tailored to the type of computations in the applications of a particular domain. Broadly speaking, DSAs encompass any computing architecture that provides:

• Superior energy efficiency through specialized processing: The specialized processors accelerate the frequently occurring domain-specific computations in hardware, thereby boosting energy efficiency. For example, a custom-designed fast Fourier transform (FFT) hardware accelerates the direct- and inverse-FFT operations, while a systolic matrix multiplication processor accel-

erates machine learning and AI applications.

- **Programmability/flexibility:** DSAs aim to improve the programming flexibility for both domain and non-domain applications. For example, DSAs that target neural network inference must be programmable to execute multi-layer perceptrons, convolutional neural networks, and recurrent neural networks. *Second*, they must be capable of executing other neural network inference operations that cannot be easily implemented using specialized hardware. *Finally*, they should be able to execute non-domain applications to improve flexibility and enable broader usage.

- Heterogeneous processing elements (PEs): The diverse types of PEs in DSAs cater to contrasting application requirements such as low power, high performance, energy efficiency, and programmability.

The potential of DSAs is also evident in recent and growing commercial examples. Google's tensor processing unit (TPU) comprises hardware designs, systems, and software stacks to accelerate machine learning training and inference [41, 42]. TPUs provide  $3\times-7\times$  speedup over state-of-the-art GPUs and  $80\times$  better energy efficiency than general-purpose processors [22, 43, 44]. Nvidia's data center processing unit (DPU) is another DSA that integrates high-performance Arm cores and hardware accelerators with an extensive software eco-system optimized for AI, cloud supercomputing, network security, and wireless communication [45]. Intel's infrastructure processing unit (IPU) is a programmable network device that integrates with server CPUs to accelerate networking control, storage manage-

ment, and security. Offloading the infrastructure operations to the IPU reduces the overhead of infrastructure tasks to improve overall performance and energy consumption [46]. In the low-power domain, RedMulE offers a sub-100 mW DSA for deep learning that comprises RISC-V cores and dedicated matrix-multiplication accelerators [47]. DSAs have started making substantial strides in all domains to offer superior energy efficiency and short time-to-market.

### 1.1 Contributions

DSAs offer multiple alternative PEs to execute tasks, such as general-purpose cores, hardware accelerators, and specialized processors. To exploit the potential of DSAs, one of the most critical aspects remains the ability to efficiently utilize the available PEs for task execution [48, 49, 18]. To this end, system-level design - including scheduling, power-thermal management algorithms and design space exploration studies - plays a crucial role. The first contribution of this dissertation presents a system-level domain-specific SoC simulation (DS3) framework to address this need. DS3 enables both design space exploration and dynamic resource management for power-performance optimization of domain applications. We showcase DS3 using six real-world applications from wireless communications and radar processing domain. DS3, as well as the reference applications, is shared as open-source software to stimulate research in this area.

Reaching the full potential of these architectures depends critically on optimally scheduling the applications to available resources at runtime. The second

contribution of this dissertation addresses these two requirements simultaneously. Existing optimization-based techniques cannot achieve this objective at runtime due to the combinatorial nature of the task scheduling problem. As the third theoretical contribution, this work poses scheduling as a classification problem and proposes a hierarchical imitation learning (IL)-based scheduler that learns from an Oracle to maximize the performance of multiple domain-specific applications. Extensive evaluations with six streaming applications from wireless communications and radar domains show that the proposed IL-based scheduler approximates an offline Oracle policy with more than 99% accuracy for performance- and energy-based optimization objectives. Furthermore, it achieves almost identical performance to the Oracle with a low runtime overhead and successfully adapts to new applications, many-core system configurations, and runtime variations in application characteristics. The fourth contribution focuses on optimization of decision tree classifier inference in hardware and software and achieves a latency of less than 50 nanoseconds for trees of up to depth 12.

Decision trees (DTs) perform high-quality, low-latency task scheduling to utilize the massive parallelism and heterogeneity in DSSoCs effectively. However, offline trained DT scheduling policies can quickly become ineffective when applications or hardware configurations change. There is a critical need for runtime techniques to train DTs incrementally without sacrificing accuracy since current training approaches have large memory and computational power requirements. To address this need, we propose INDENT, an incremental online DT framework to update the scheduling policy and adapt it to unseen scenarios. INDENT updates DT sched-

ulers at runtime using only 1-8% of the original training data embedded during training. Thorough evaluations with hardware platforms and DSSoC simulators demonstrate that INDENT performs within 5% of a DT trained from scratch using the entire dataset and outperforms current state-of-the-art approaches.

DSSoCs integrate several hardware components, resulting in higher design, implementation, and validation complexities. Significant emphasis on pre-silicon validation is required to eliminate functional and performance bugs to avoid the post-silicon failure cost and market loss penalties. Emulation frameworks accelerate pre-fabrication design validation by prototyping target designs. They also allow the early development of software, drivers, firmware, and performance analysis. As the final contribution, we present FALCON, a full-system DSSoC emulation platform that allows functional validation of DSSoCs as they interact with the operating system and runtime frameworks. We show that FALCON allows early software and driver development for accelerators and validates the system before the silicon availability. Finally, we demonstrate that FALCON enables rapid and extensive design space exploration to obtain early pre-silicon power and performance estimates.

In summary, this dissertation makes the following contributions:

- A detailed and comprehensive literature review on DSAs and corresponding research directions [50],

- DS3, a domain-specific system-on-chip simulation framework to perform rapid design space exploration and evaluate resource management algorithms [51],

- An imitation learning (IL) based task scheduling approach [49],

- Optimization techniques for decision tree classifiers [52],

- An incremental and online decision tree training framework [53], and

- An FPGA-based emulation framework for domain-specific architectures.

The rest of the dissertation is organized as follows. The literature survey is discussed in Chapter 2. Chapter 3 presents DS3 and discusses its role in high-level design space exploration and evaluation of resource management algorithms. The IL based task scheduling approach for heterogeneous SoCs is presented in Chapter 4. The optimization of decision tree (DT) classifiers for IL is discussed in Chapter 5. Chapter 6 presents a novel approach to adapt standalone DT classifiers online to variations in the environment. Chapter 7 presents the FPGA-based emulation framework to perform pre-silicon functional validation, early software development, performance and power analysis. Finally, Chapter 8 concludes this dissertation with directions for future work.

## 2.1 Research Directions in Domain-Specific

### **Architectures**

DSAs have the potential to enable high energy efficiency and programmability across multiple applications. However, critical research and infrastructure design challenges must be addressed before DSAs can become a mainstream computing paradigm [6, 22, 54]. For instance, designers must choose the optimal number and type of PEs to balance design time, cost, complexity, area, and energy efficiency. Novel and rapid hardware design techniques that condense the design time and costs allow for a shorter time-to-market [54, 55]. Similarly, DSAs require novel and state-of-the-art simulation, compilation, and emulation frameworks to minimize the gap between conceptualization and market availability of a product [56]. In summary, there is a strong need to understand the factors that currently limit the design and deployment of DSAs. To this end, this dissertation identifies the key research areas (summarized in Figure 2.1) that need new ideas and solutions to make DSAs default choices for designers, developers, and end-users:

• **Domain Representation:** Application source code must be analyzed to extract the domain-specific kernels and construct the data flow graphs that can exploit the data- and task-level parallelism both in applications and hardware [57]. Understanding the domain applications plays a critical role in selecting the PEs for the DSA.

Figure 2.1: Prime research directions in the conceptualization, design and development of DSAs. Applications are represented as directed flow graphs. The nodes in the graph represent the key computational kernels within each application and the edges of the graph denote the communication volumes between kernels.

- Hardware Architecture and Design: With the saturation of energy efficiency

of general-purpose processors, DSAs require novel hardware architectures

and innovative solutions to exploit parallelism and maximize energy efficiency

for domain-specific kernels.

- **Resource Management in DSAs:** Exploiting the full potential of DSAs involves optimally allocating the tasks to PEs, and selecting their voltage-frequency levels at runtime using resource management algorithms.

- Evaluation Frameworks and Productivity Tools: DSAs demand the need for rapid design space exploration frameworks to aid top-level design decisions in the early development phase, and emulation platforms to aid functional validation and software development.

- **Software Development:** The challenge in programming DSAs with heterogeneous PEs demands innovation in software frameworks and toolchains.

Furthermore, the software stack also serves as a bridge between domain representation, hardware and resource management techniques.

### 2.1.1 Interactions between the Research Directions

This section discusses the interactions between the research directions presented so far, as outlined in Figure 2.2. Domain representation efforts analyze the applications and present computational kernels that are potential candidates for implementation in special-purpose hardware. The hardware architecture and design exploit this information to develop customized and efficient processing for these potential candidates using either fixed-function or specialized accelerators. Hardware design techniques also leverage the data dependencies between the kernels in applications to design an appropriate on-chip communication network, such as bus, point-to-point network, and network-on-chip. Similarly, the domain analysis provides design-time and runtime information to the resource management algorithms. Design-time information includes the kernel characteristics and their interactions that affect latency, execution time, and communication volumes. Resource management algorithms exploit this information offline to deploy targeted scheduling and power management techniques for the chosen PEs. The domainspecific information in the applications helps narrow down the vast design space. Simulation frameworks perform rapid design space explorations and systematically evaluate resource management algorithms. The domain representation techniques and software stack share similar tools and infrastructure, such as compilation and performance profiling APIs. They target specific hardware by providing the rele-

Figure 2.2: Interactions between the research directions for the realization of DSAs. The kernel and flow graph information of domain applications and target metrics drive the hardware architecture and design of PEs. The application and hardware PE information is exploited by the resource management techniques. The DSA configurations are evaluated for functionality and performance using simulators, emulation frameworks, and the software stack.

vant compiler and API support. Finally, emulation frameworks accelerate software development, enable performance evaluation, and facilitate functional validation to improve the time-to-market for DSAs.

### 2.1.2 Insights and Open Challenges

DSAs are making solid advances toward becoming the preferred choice for future computing systems. DSA design and development efforts require significant attention as the algorithms, design methodologies, and tools evolve. Furthermore, the subtle interaction between the different DSA research aspects requires substantial

research focus. The ever-lasting pursuit of maximizing performance and energy efficiency while minimizing the cost and design effort leaves the following open research questions:

- How can we reduce the time required to generate application traces, scope them and extract the flow graphs?

- Can we perform DSA hardware-aware application code compilation using state-of-the-art and just-in-time compilation techniques?

- Can we automatically generate highly optimized and specialized hardware based on high-level requirements, such as performance, power, and throughput?

- How can we architect easily programmable and flexible, yet highly specialized hardware?

- Can we design light-weight and near-optimal resource management algorithms considering all application requirements, such as performance, power consumption, energy efficiency, and deadlines?

- Can we explore preemption-based resource management techniques with hardware accelerators (that do not allow context switching) to address realtime needs?

- How can we automatically generate software support for custom-designed hardware accelerators and reduce the development time?

- How can we accurately and quickly calibrate high-level simulators with presilicon data or real hardware, speed up cycle-accurate simulations and reduce the development times for emulation frameworks?

- How can we embed security and privacy into all the DSA design aspects and components?

- How can we seamlessly integrate the different DSA research directions and tools to maximize performance and energy efficiency with minimum intervention from users and developers?

A few challenges involved in DSA design listed in the different sections are compiled here. These and similar questions demand innovation and research for performant and energy-efficient DSA-based computing systems. A comprehensive review on the research problems in DSAs and promising approaches is presented in [50]. This dissertation addresses some of the challenges described here to make DSAs a mainstream computing paradigm.

## 2.2 Evaluation Frameworks for DSAs

### 2.2.1 Simulation Frameworks

As the use cases for a simulation environment intersect with a number of distinct research areas, we break the related work into three parts. First, we discuss existing work in the area of scheduling, power, and thermal optimization algorithms, and we motivate a need for a unified framework that integrates these with rich design

space exploration capabilities. Second, we discuss existing work in the area of design space exploration for embedded systems, and we note the lack of rich support for thermal/power models or plug-and-play scheduling frameworks. Third, for completeness, we give a brief overview of related works in the scope of high performance computing or non-embedded environments. Together, this set of related works serves to motivate the need for an environment such as DS3 that unifies all of these aspects into a single, open-source framework for embedded DSA development.

Starting with works on scheduling, power, and thermal optimization algorithms, one of the most important goals of heterogeneous SoC design is to optimize energy-efficiency while satisfying the performance constraints. To this end, a variety of offline and runtime algorithms have been proposed to schedule applications to PEs in multi-core architectures [58, 59, 60, 61]. Similarly, DVFS policies, such as HiCAP [62], power management governors, such as *ondemand* [63], and thermal management techniques [64] have been proposed to efficiently manage the power and temperature of SoCs. However, existing approaches are typically evaluated in isolated environments and different in-house tools. Hence, there is a strong need for a unified simulation framework [65] to compare and evaluate various scheduling algorithms in a common environment.

Next, there are a large number of works on design space exploration for embedded systems, but they are found to be lacking in support for rich scheduling, thermal, and power optimization algorithms. Khalilzad et al. [66] consider a heterogeneous multiprocessor platform along with applications modeled as synchronous

dataflow graphs and periodic tasks. The design space exploration problem is solved using a constraint programming solver for different objectives such as deadline, throughput, and energy consumption. ASPmT [67] proposes a multi-objective tool using Answer Set Programming (ASP) for heterogeneous platforms with a grid-like network template and applications specified as directed acyclic graphs (DAGs). Trčka et al. [68] utilize the Y-chart [69] philosophy for design space exploration and introduces an integrated framework using the Octopus toolset [70] as its kernel module. Then, for different steps in the exploration process (i.e., modeling, analysis, search, and diagnostics), different languages and tools such as Ptolemy, Uppaal, and OPT4J are employed. Target platforms and applications are modeled in the form of an intermediate representation to support translation from different languages and to different analysis tools. Artemis [71] aims to evaluate embedded-systems architecture instantiations at multiple abstraction levels. Later, authors extend the work and introduce the Sesame framework [72] in which target multimedia applications are modeled as Kahn Process Network (KPN) written in C/C++. Architecture models, on the other hand, include components such as processor, buffers, and buses and are implemented in SystemC. The framework supports different schedulers such as first in, first-out (FIFO), round-robin, or customized. A trace-driven simulation is applied for cosimulation of application and architecture models.

Finally, ReSP [73] is a virtual platform targeting multiprocessor SoCs focusing on a component-based design methodology utilizing SystemC and transaction-level modeling libraries. ReSP adopts lower-level instruction set based simulation

approach and is restricted to applications implemented in SystemC. All aforementioned frameworks or tools lack accurate power and thermal models, and do not support for exploration of scheduling algorithms and power-thermal management techniques.

Outside of embedded systems, there has also been a large body of work on design space exploration via heterogeneous runtimes at the desktop or HPC scale, with StarPU [74] being one of the most prominent examples of such a runtime. StarPU is a comprehensive framework that provides the ability to perform run-time scheduling and execution management for DAG based programs on heterogeneous architectures. Although, the framework allows users to develop new scheduling algorithms, StarPU lacks power-thermal models and DVFS techniques to optimize power and energy consumption. A recent work [75] targets domain-specific programmability of heterogeneous architectures through intelligent compile-time and run-time mapping of tasks across CPUs, GPUs, and hardware accelerators. In the proposed approach, the authors employ four different simulators, more specifically, Contech to generate traces, MacSim to model CPU/GPU architectures, BookSim2 to model the networks-on-chip, and McPat to predict energy consumption. The proposed DS3 simulator integrates the above features in a unified framework to benefit similar studies in the future.

To the best of our knowledge, DS3 is the first open-source framework to integrate all of these distinct elements into a unified simulation environment targeting embedded DSAs. It includes built-in analytical models, scheduling algorithms, DTPM policies, and six reference applications from wireless communication and

radar processing domain.

### 2.2.2 Emulation Frameworks

Emulation frameworks overcome the limitation of simulators by enabling functional verification, early software and firmware development [76, 73, 77]. The emulation frameworks are broadly classified into virtual model-based emulators and FPGA-based frameworks that rely on the actual implementation [78]. It is worth noting that only FPGA-based frameworks allow functionality validation since they use the actual implementation, as compared to representative models in virtual platforms.

The emergence of SystemC and TLM-based modeling also significantly enhanced the development of virtual emulation frameworks [79]. The quick emulator (QEMU) deploys abstract models of the computing elements and transaction-level models for its interactions with the rest of the system [80]. QEMU also enables developers to bringup a variety of guest operating systems and execute applications on the CPU through dynamic binary translations [81]. Along these lines, Arm provides fast models which are accurate and representative models of their IPs such as CPUs, interconnects, subsystems, and other peripheral components [82]. Fast models allow the bringup of the Linux OS, and programmers to develop software, firmware, and applications.

FPGA-based frameworks also improve task scheduling and DTPM policies by utilizing more realistic estimates in MPSoCs [83, 84]. An MPSoC-based sensorand actuator-rich cyber-physical SoC is prototyped in [20], enabling hardware and software co-design. Other frameworks for MPSoCs are presented and discussed

in [85, 86]. The MPSoC-based frameworks must be adapted for DSAs by integrating the other components, such as specialized cores, hardware accelerators, and on-chip interconnects. In that direction, the FPGA-based user-space emulation framework in [87] integrates hardware and software to evaluate resource management policies for DSAs. While this work is an initial step in the DSA direction, frameworks that scale to the entire design are critical to bridge the gap between the requirements and state-of-the-art approaches.

To the best of our knowledge, FALCON is the first FPGA-based emulation platform that integrates general-purpose processors, hardware accelerators, on-chip interconnect, and a detailed software stack that supports the Linux operating system (OS).

## 2.3 Resource Management Techniques for

# **Heterogeneous Architectures**

DSAs offer multiple alternative PEs to execute tasks, such as general-purpose cores, hardware accelerators, and specialized processors. To exploit the potential of DSAs, one of the most critical aspects remains the ability to efficiently utilize the available PEs for task execution [48, 49, 18, 88]. This section discusses the resource management aspects of DSAs, key bottlenecks, and outstanding research problems.

The techniques fall broadly into two categories: (1) static (or design-time) and (2) dynamic (or runtime) techniques. Static algorithms utilize the design time information to manage the resources [1, 89, 90]. These algorithms can provide

optimal or heuristic solutions since they are not bounded by computation and latency constraints [91]. Static approaches cannot access runtime information and are inefficient in several scenarios [49]. DSAs inherently support several simultaneous applications that could demand a substantial amount of system resources. While static algorithms may suffice in limited application-specific scenarios, DSAs require efficient runtime resource management techniques. While several static and dynamic approaches have been proposed previously [92, 93, 94, 95, 96], the following fundamental challenges drive the research need for novel dynamic techniques that target DSAs:

- **Heterogeneity:** PEs with different power and performance characteristics for various applications require algorithms to evaluate all valid execution alternatives to obtain the optimal solution. Considering the characteristics of all heterogeneous PEs at runtime makes the resource management problem complex.

- Streaming Arrivals: Most applications (e.g., video/signal processing, autonomous driving, radar systems) continuously perform identical operations on streaming data frames. The complexity lies in efficiently managing the resources when randomly arriving frames overlap with currently executing and pending tasks from previous frames.

- Concurrent Applications: SoCs execute several applications simultaneously.

Resource management techniques must recognize the divergent application

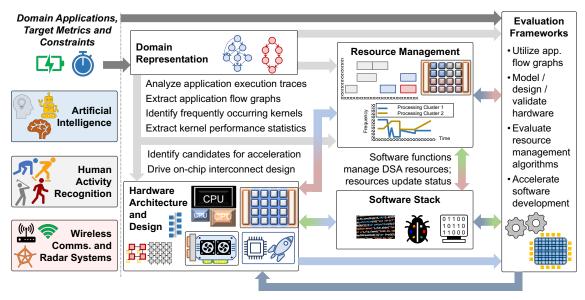

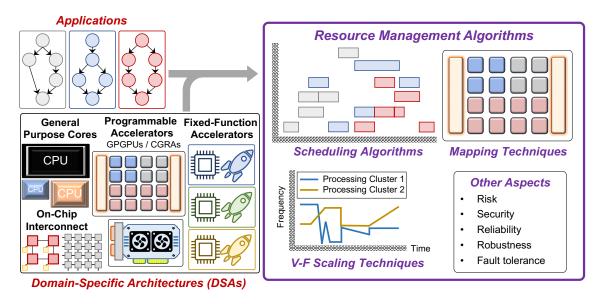

Figure 2.3: The key areas of focus in DSA resource management techniques which interface with the domain applications and DSA hardware. The domain representation outputs and hardware design decisions are used to design task scheduling, voltage-frequency scaling, and other resource management techniques.

characteristics and satisfy their compute requirements, performance, power, and deadline constraints.

The type of applications and the choice of hardware components in the DSA play a critical role in developing resource management techniques. The various aspects of resource management algorithms shown in Figure 2.3 are discussed in the next sections.

## 2.3.1 Task Scheduling Techniques

Current many-core systems use runtime heuristics to enable scheduling with low overheads. For example, the completely fair scheduler (CFS) [97], widely used

in Linux systems, aims to provide fairness for all processes in the system. CFS maintains two queues (active and expired) to manage task scheduling. In addition, CFS gives a fixed time quantum for each process. Tasks are swapped between active and expired queues based on activation and expiration of the time quantum. However, complex heuristics are required to manage such queues. CFS also does not generalize to optimization objectives apart from performance and fairness. More importantly, CFS scheduling is limited to general-purpose cores and lacks support for specialized cores and hardware accelerators [98]. With the same limitations, shortest job first (SJF) [99] scheduler estimates the task's CPU processing time and assigns the first available resource to the task with the shortest execution time.

List scheduling techniques [100, 101] for DAGs [1, 102, 89] prioritize various objectives, such as energy [103, 104], fairness [105], security [106]. In general, this technique places the nodes (tasks) of a DAG in a list and provides a PE assignment and order at design time. Heterogeneous earliest finish time (HEFT) [1] is one example, in which an upward rank is computed to perform the scheduling decisions. The authors in [102] use a lookahead algorithm as an enhancement to the HEFT scheduler to improve the execution time, but suffers from fourth order complexity  $O(n^4)$  on the number of tasks (n). Another recent technique shows improvement in performance with quadratic complexity [89]. However, these algorithms suffer from the time complexity problem and are tailored to particular objectives and fail to generalize to a combination of objectives and choice of applications.

Machine learning (ML)-based schedulers show promise in eliminating the drawbacks of list scheduling and runtime heuristic techniques. ML-based sched-

ulers possess the capabilities to be further tuned at runtime [33]. A recent support vector machine (SVM)-based scheduler for OpenCL kernels assigns kernels (tasks) between CPUs and GPUs [107]. In contrast to schedulers that use supervised learning, authors in [108] uses reinforcement learning (RL) to schedule Tensorflow device placement, but lacks the ability of scheduling streaming jobs. DeepRM [33] uses deep neural networks with RL for scheduling at an application granularity as opposed to using the notion of DAGs. On the other hand, Decima [109] uses a combination of graph neural networks and RL to perform coarse-grained processing-cluster level scheduling for streaming DAGs.

RL-based scheduling techniques have two major drawbacks. *First*, they require a significant number of episodes to converge. For example, the technique proposed in [109] takes 50k episodes, with 1.5 seconds each, to converge to a solution that is equivalent to 21 hours of simulation in Nvidia Tesla P100 GPU. *Second*, the efficiency of an RL-based technique predominantly depends on the choice of the reward function. Usually, the reward function is hand-tuned, depending on the problem under consideration.

To overcome these difficulties, we propose an IL-based scheduling methodology. Since IL uses an Oracle to construct a policy, it does not suffer from slow convergence, as seen in RL. IL-based policies were initially used in robotics to show their fast convergence property [110]. Recently, the use of imitation learning to intelligently manage power and energy consumption in SoCs has been demonstrated [111, 112]. To the best of our knowledge, this is the first approach that applies IL for multi-application streaming task scheduling in heterogeneous many-core platforms.

## 2.3.2 Dynamic Thermal-Power Management (DTPM) Techniques

State-of-the-art PEs and cores support multiple voltage and frequency (V-F) levels. Another critical aspect in exploiting the potential of DSAs is optimally selecting these power states at runtime [113, 114, 115]. The V-F levels of PEs play a primary role in determining power and performance, while power consumption determines the temperature of the PEs [116]. For example, using the highest V-F levels to maximize performance increases power consumption and, in turn, the temperature [117]. Furthermore, portions of the SoC may be placed in different levels of sleep states where they are partially or entirely powered off to save energy and control temperature [8]. Like task scheduling, V-F selection for the cores is also NP-complete [118]. Therefore, efficient DTPM techniques are essential to utilize DSAs efficiently while maintaining the chip temperature within limits [83].

The DTPM techniques also fall into categories similar to the task scheduling algorithms, namely optimization-, heuristic-, and machine learning-based techniques. The extensive use of heterogeneous multiprocessor systems-on-chip (MPSoCs) in battery and energy-constrained systems has attracted substantial research in this domain. The heuristic techniques proposed in [119] and [120] use the difference between achieved and target metrics to adjust the frequencies. The approach presented in [121] combines the benefits of traditional control theoretic approaches and heuristics to develop a lightweight and efficient frequency scaling policy. The control theoretic approach presented in [122] proposed a DVFS technique that calculates the change in application execution time with change in frequency to

honor soft deadline constraints. Recent approaches presented in [123, 113, 124] use machine learning to train policies to determine the optimal operating frequency and generalize to unseen workloads. Temperature management on heterogeneous SoCs is also critical as the on-die power density critically increases [116, 125, 126]. Current approaches for power and thermal management techniques focus on homogeneous and heterogeneous CPU cores and also on GPUs, comprehensively discussed in [127]. A few techniques consider hardware accelerators in their power management policies [128, 129]. However, DSAs demand novel techniques that consider all types of hardware accelerators and specialized cores since they can significantly contribute to the overall power, energy, and temperature.

## 2.3.3 Other Resource Management Research Directions

While task scheduling, mapping, and DTPM ideas dominate the primary aspects of resource management, modern-day SoCs look at other aspects to satisfy requirements such as reliability and security to meet user expectations and privacy standards. For instance, SoCs and processors from Apple, Intel, and RISC-V include a secure enclave to protect user data when the platform is experiencing security attacks [130, 131, 132]. Instead of relying solely on the secure enclave to protect sensitive data, building security into other aspects enhances the security of the design. DSAs seek adaptation and advancement of ideas from prior work on heterogeneous MPSoCs.

**Risk and Security:** Integrating security into scheduling algorithms and dynamic voltage frequency scaling (DVFS) governors is at the expense of chip area, schedul-

ing latency, power and energy overheads, and design complexity. Therefore, low complexity and runtime overheads remain essential requirements of security-aware techniques. Commercial SoCs integrate several third-party IPs to promote design reuse and improve the design cycle [133]. However, using external IPs has the severe risk of untrusted designs, leading to security flaws. To this end, a multi-dimensional optimization approach improves the security of the MPSoC through task scheduling with negligible impact on performance and no additional hardware cost [134]. In this approach, task duplication and isolation are the two techniques that aid in detecting hardware trojans in the presence of third-party IPs. Recent literature has shown that security attacks can extract sensitive data by exploiting the temperature patterns on the chip [135]. Indeed, the ThermalAttackNet [136] discusses the potential of DVFS governors in avoiding the detection of stored passwords using on-chip temperature patterns. Therefore, integrating such techniques into resource management algorithms improves the security of DSAs.

Reliability and Robustness: With the increasing use of SoCs in safety-critical applications (such as autonomous driving, avionics, and medical applications), there is a critical emphasis on reliable and robust computing [137, 138]. The chip temperature plays a critical role in the mean time to failure since it directly impacts the metal fatigue. A tradeoff between power consumption and reliability (in the mean time to failure) is explored by estimating the failure rate at a given chip temperature in [139]. The DVFS technique proposed in this paper integrates a reliability metric into its optimization problem to increase the mean time to failure. Furthermore, differential aging of cores in an SoC results in certain cores failing

sooner than the other counterparts. To address this challenge, the scheduling approach presented in [140] includes the mean time to failure in the objective function along with deadline constraints. While the above techniques focus on prolonging the time to failure, task scheduling techniques also provide reliable and robust decisions in the presence of system faults [141, 142]. For space-based applications, state-of-the-art approaches must provide reliable and robust decision in high-radiation environments [143, 142, 144]. In summary, emerging reliability and robustness requirements demand resource management approaches for DSAs to take them into consideration to enhance usability.

# 2.4 Incremental and Online Updates to Decision Tree Classifiers

DSAs integrate multiple heterogeneous processing elements and offer massive parallelism to execute several jobs in parallel [6, 22]. Task scheduling algorithms must effectively allocate the tasks to the processing elements at runtime to fully exploit their potential [23]. Scheduling policies range from simple lookup tables to static and runtime heuristic schedulers [1, 145, 102, 146, 147]. More recently, DT based machine learning schedulers have attracted significant interest since they provide interpretability and ultra-low inference latencies, making them highly suitable for DSA resource management [49, 52, 148].

Current ML approaches are *static*, i.e., their rules do not change at runtime. Consequently, these models cannot adapt to workload changes and new scenarios.

Therefore, DT classifiers used for resource management must possess the capability to adapt on-the-fly to the variations in the environment, which are inevitable. Since DTs are conventionally batch trained using the CART algorithm, there is a strong need for novel techniques to allow DTs to be updated online [149]. To this end, we categorize the prior work on adaptive, online, and incremental updates to DTs into three broad categories, and compare them qualitatively in Table 2.1.

Reinforcement Learning (RL): Neural networks use stochastic gradient descent (SGD) to update the model parameters in multiple batches. Differentiable and fuzzy approaches utilize SGD approaches to update the DT parameters [150, 3, 151]. After converting a DT to a differentiable model, RL and SGD algorithms can update the parameters when new applications or SoC configurations are encountered. However, RL suffers from significant drawbacks because of: (1) excessive time needed to explore the search space for large problem sizes (such as DSAs), (2) high computational power required to perform SGD iteratively for several iterations, (3) the complexity in designing a good reward function, and (4) difficulty in converging to a well-performing policy [49, 33].

Ensemble Decision Tree Algorithms: Ensemble DT algorithms [4, 152] comprise two key steps: (1) training multiple weak DTs, and (2) combining the weak predictions to obtain a final prediction [153]. Resource management applications target inference latencies in the order of tens of nanoseconds [52]. Hence, executing multiple inferences and combining their predictions in DT ensembles have prohibitive latency overheads, as quantified in Chapter 6.

**Hoeffding Trees:** Hoeffding trees are used when the training sample size exceeds

Table 2.1: Comparing INDENT with prior work on DT training.

| Technique                  | Allows<br>Online<br>Update | Computation<br>and Memory<br>Resources | Training<br>Time | Inference<br>Latency | Ease of<br>Convergence |

|----------------------------|----------------------------|----------------------------------------|------------------|----------------------|------------------------|

| CART DT [149, 4]           | No                         | Low                                    | Low              | Low                  | High                   |

| RL [3]                     | Yes                        | High                                   | High             | Low                  | Low                    |

| DT Ensembles [4, 152, 154] | Yes                        | Low                                    | Low              | High                 | Moderate               |

| Hoeffding Trees [2]        | Yes                        | Low                                    | Low              | Low                  | Low                    |

the memory capacity. They stream the data samples, i.e., the algorithm only observes a portion of the data at a time to construct the DT [2]. However, they rely on a critical assumption: the data distribution does not change over time, and a small set of observed samples is representative of the entire dataset [155]. However, this vital assumption does not apply to SoC resource management. First, the training samples are not independent and identically distributed since they depend on previous scheduling decisions. Second, the initial training samples are not representative of the new applications and additional processing clusters. Therefore, the Hoeffding tree family of algorithms does not converge to a model that performs well for resource management applications; hence is not suitable for online updates [156, 155].

To the best of our knowledge, INDENT is the first approach to incrementally update a single DT model online. INDENT stores just 1-8% of the original training data and yet performs within 5% of a DT that was trained with the entire training data.

#### 3 DS3: A DOMAIN-SPECIFIC SYSTEM-ON-CHIP SIMULATION

#### FRAMEWORK

## 3.1 Background, Motivation and Contributions