#### **Exploiting Simple Analytical Models for Modeling Hardware Accelerators**

by

#### Muhammad Shoaib Bin Altaf

A dissertation submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

(Electrical & Computer Engineering)

at the

UNIVERSITY OF WISCONSIN-MADISON

2016

Date of final oral examination: 12/08/2016

The dissertation is approved by the following members of the Final Oral Committee:

Mark Hill, Professor, Computer Science

Mikko Lipasti, Professor, Electrical & Computer Engineering

Karthikeyan Sankaralingam, Associate Professor, Computer Science

Michael Swift, Associate Professor, Computer Science

David Wood, Professor, Computer Science

To my parents Tehseen Kausar and Sheikh Altaf Hussain, and my wife Iram Majeed for their love and support.

#### **ACKNOWLEDGMENTS**

I consider myself fortunate enough to work under the guidance of my advisor, David Wood. I would not have completed my thesis without his support. Working with David, can be a challenge in the beginning and you take time in getting settled with his unique style of mentoring. He gave me the freedom to choose a problem of my own choice but made sure that I stayed on the right path. He has a knack for communicating ideas succinctly, and expects (and forces) his students to develop the same. Thanks to David, I consider myself a better writer and researcher. Thanks David.

I am also thankful to my committee members for providing useful feedback and comments on my work. Mark Hill encouraged and showed excitement about the modeling framework right form the beginning. His advice on making slides has helped me become a better presenter. Mikko Lipasti suggested the retrospective study of the various interfaces. Micheal Swift suggested the name for "Accelerometer", and his system background improved my work in general and this thesis in particular. Karu Sankaralingam challenged several of my assumptions and made me rethink some parts of the modeling infrastructure.

I would also like to thank my architecture colleagues here at University of Wisconsin-Madison, for the technical and non-technical discussions, including Raghuraman Balasubramanian, Arka Basu, Emily Blem, Yasuko Eckert, Chris Feilbach, Jayneel Gandhi, Dan Gibson, Dibarkar Gope, Venkatraman Govindaraju, Gagan Gupta, Swapnil Haria, Joel Hestness, Derek Hower, Marc de Kruijf, Jason Lowe-Power, Jaikrishnan Menon, Tony Nowatzki, Marc Orr, Sankaralingam Panneerselvam, Vignyan Reddy, Somayeh Sardashti, Rathijit Sen, Srinath Sridharan, Nilay Vaish, Aditya Venkataraman, Amit Yadav, and Hongil Yoon. I would also like to thank the computer architecture affiliates for their feedback.

I am also thankful to Newsha Ardalani—my office-mate for last five years—for introduc-

ing me to the Persian cuisine, lengthy political discussions and sharing mutual frustrations of the graduate school.

I am also thankful to Waheed Bajwa, Muhamamd Zeeshan Nazir and Atif Hashmi for helping me during my early days in Madison. I would also like to thank the Pakistani community and my friends at the Pakistani Students Association for making Madison a home away from home, including Farha Ahmed, Rafay Ahmed, Ali Ahsan, Yasmin Flodin Ali, Bilal Idress Allalwala, Ammad Amin, Umar Anjum, Farhat Hashim, Faisal Khan, Nayab Khan, Samina Khan, Farhat Khan, Lamin Manneh, Rehan Rauf, Rehman Rauf, Nabeel Sharif, Sara Siddiqui, Saad Siddiqui, Anoushka Syed, Deeba Syed, Hashim Waris and Hiba Zakai. Special thanks to Neelofer Khilji for the food.

I thank my close friends in Madison: Syed Zohaib Masood Gilani—my apartment-mate for four years—for willingly consuming the meals I made, Arslan Zulfiqar for the late night "chai" sessions, Rehan Ahmed for the on-demand coffee, Zehra Imam for the cooking sessions, Anisa Ali for the skating lessons, and Junaid Khalid for constantly reminding me about graduating.

I would also like to thank my friends and colleagues at the Daily Cardinal including Aarushi Agni, Alison Bauter, Abby Becker, Riley Begin, Sam Cusick, Stephanie Daher, Scott Girard, Kayla Johnsonova, Mark Kauzlarech, Garce Liu, Dylan Moriarty, Grey Satterfield. They provided the opportunity to not only hone my photography skills but also watch the Badger games for free.

I am also thankful to organizations and individuals which supported me during my graduate studies: University of Engineering & Technology, Lahore Pakistan for funding me in the early semesters at UW-Madison; Mark Allie for providing me teaching assistantship for two years; Kevin Moore for the internship opportunity at Oracle Labs; Wisconsin

Alumni Research Foundation (WARF) for the student ambassadorship opportunity; and Brian Wilson at the DoIT and Eric Sedlar at Oracle Labs for providing access to SPARC T3 and T4 servers, respectively.

Completing my graduate studies would have not been possible without the love and support of my family. I am thankful to my parents, Tehseen Kausar and Sheikh Altaf Hussain, for their love, support and lifelong sacrifices. They have been waiting for this day for a long time. I am also thankful to my siblings for providing inspirations right from my childhood. They brought the best out of me by always raising the bar and supporting my decisions. My elder brother, Muhammad Umair Bin Altaf, encouraged me to apply at Wisconsin and made graduate school life experience easier. My sister, Abeera Batool, lent her ear whenever I wanted to vent out my frustrations. She has a talent for convincing people to look at the brighter perspective. I always felt better after talking to her. My younger brother, Muhammad Awais bin Altaf, acted like an elder brother by regularly providing comforting messages and making sure that I am having a good time. He used to share his personal PhD experiences to help me feel better. Thank you for everything.

I am also thankful to my in-laws for keeping me motivated by regularly asking about my graduation plans. Thank you Zulfiqar Majeed, Musarrat Zulfiqar, Sobia Majeed, Affifa Majeed, Anam Majeed and Asim Majeed.

Last but not the least, I'm thankful to my wife, Iram Majeed and son, Shaffan Altaf, for providing the daily reminders that there is more to life than the graduate school. There were times during thesis writing when I did not want to be with myself and Iram still had to bear with me. I would have not succeeded without her sacrifices and support. Love you and thanks for being a part of my life.

# **CONTENTS**

| Co  | nten               | ts v                                                                                                           |

|-----|--------------------|----------------------------------------------------------------------------------------------------------------|

| Lis | t of T             | Tables viii                                                                                                    |

| Lis | t of I             | Figures ix                                                                                                     |

| Ab  | strac              | et xiv                                                                                                         |

| 1   | Intro              | oduction 1  Contributions 4  1.1.1 LogCA: A High-Level Unified Performance and Energy Model for                |

|     | 1.2                | Hardware Accelerators                                                                                          |

| 2   | Back<br>2.1<br>2.2 | kground and Related Work 7  Accelerator Architectures 7  Analytical Models 8  2.2.1 Simple Modeling Frameworks |

|     | 2.3                | Roofline Models 14                                                                                             |

| 3   |                    | luation Methodology 17  Experimental Setup 17  Workloads 18  Experimental Methodology 19                       |

| 4   | _                  | CA: A High-Level Performance Model for Hardware Accelerators 21  Introduction 21                               |

|   | 4.2  | The Lo  | ogCA Model 24                                           |    |

|---|------|---------|---------------------------------------------------------|----|

|   |      | 4.2.1   | Effect of Granularity                                   | 28 |

|   |      | 4.2.2   | Performance Metrics                                     | 28 |

|   |      | 4.2.3   | Granularity dependent latency                           | 31 |

|   | 4.3  | Experi  | imental Methodology 34                                  |    |

|   | 4.4  | Evalua  | ntion 37                                                |    |

|   |      | 4.4.1   | Linear-Complexity Kernels ( $\beta=1$ )                 | 39 |

|   |      | 4.4.2   | Super-Linear Complexity Kernels ( $\beta > 1$ )         | 41 |

|   |      | 4.4.3   | Sub-Linear Complexity Kernels ( $\beta < 1$ )           | 43 |

|   | 4.5  | Case fo | or Multiple Accelerators 45                             |    |

|   |      | 4.5.1   | Parallel Execution                                      | 45 |

|   |      | 4.5.2   | Serial Execution                                        | 48 |

|   |      |         | 4.5.2.1 Pipelined Execution                             | 49 |

|   |      | 4.5.3   | Results                                                 | 52 |

|   | 4.6  | How to  | o Use LogCA? 57                                         |    |

|   |      | 4.6.1   | For Programmers                                         | 57 |

|   |      | 4.6.2   | For Architects                                          | 59 |

|   | 4.7  | Summ    | ary 59                                                  |    |

| 5 | Log  | CAe: T  | he Energy Counterpart for the LogCA Model 62            |    |

|   | 5.1  |         | uction 62                                               |    |

|   | 5.2  | Energ   | y Model 64                                              |    |

|   | 5.3  |         | up-Efficiency Product 67                                |    |

|   | 5.4  | Result  | s 68                                                    |    |

|   |      | 5.4.1   | Linear Complexity Kernels                               | 68 |

|   |      | 5.4.2   | Super-Linear Complexity Kernels                         | 71 |

|   |      | 5.4.3   | Sub-Linear Complexity Kernels                           |    |

|   |      | 5.4.4   | Speedup-Efficiency Product                              | 71 |

|   | 5.5  | Summ    | ary 73                                                  |    |

| 6 | Acce | elerome | eter: A Sensitivity Analysis of the LogCA Parameters 76 |    |

|   | 6.1  |         | uction 76                                               |    |

|   | 6.2  | Accele  | rometer 78                                              |    |

|   |      |         |                                                         |    |

|   |   | ٠ |   | ٠ |

|---|---|---|---|---|

| v | 7 | 1 | ľ | 1 |

|   |   |   |   |   |

|     |        | 6.2.1   | Performance Bounds                      | 79 |

|-----|--------|---------|-----------------------------------------|----|

|     |        | 6.2.2   | Sensitivity Analysis                    | 80 |

|     |        | 6.2.3   | Totem Plots                             | 83 |

|     | 6.3    | Case S  | tudies 90                               |    |

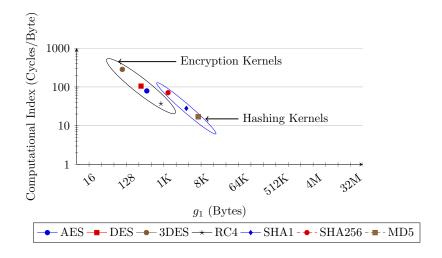

|     |        | 6.3.1   | Cryptographic Accelerators              | 91 |

|     |        | 6.3.2   | General-Purpose Accelerators            | 94 |

|     | 6.4    | Discus  | ssion 99                                |    |

|     | 6.5    | Summ    | ary103                                  |    |

| 7   | Con    | clusion | s105                                    |    |

|     | 7.1    | Summ    | ary of Contributions105                 |    |

|     | 7.2    | Limita  | tions and Directions for Future Work106 |    |

| Bil | oliogi | raphy10 | 08                                      |    |

# LIST OF TABLES

| 3.1 | Algorithmic complexity of the kernels used in the evaluation                      | 18 |

|-----|-----------------------------------------------------------------------------------|----|

| 3.2 | Description of the Cryptographic accelerators                                     | 19 |

| 3.3 | Description of the GPUs                                                           | 20 |

| 4.1 | Description of the LogCA model                                                    | 25 |

| 4.2 | Algorithmic complexity of various kernels with number of elements and granu-      |    |

|     | larity. The power of $g$ represents $\beta$ for each kernel                       | 36 |

| 4.3 | Calculated values of LogCA Parameters                                             | 37 |

| 4.4 | Parallel execution of AES for various granularities. 'n' represents the number of |    |

|     | accelerators running in parallel                                                  | 53 |

| 4.5 | Pipelined execution of matrix multiplication on a discrete GPU. 'n' represents    |    |

|     | the number of pipeline stages                                                     | 53 |

| 4.6 | Pipelined execution of FFT on discrete GPU. 'n' represents the number of          |    |

|     | pipeline stages.                                                                  | 54 |

| 4.7 | Pipelined execution of Radix Sort on a discrete GPU. 'n' represents the number    |    |

|     | of pipeline stages                                                                | 54 |

| 5.1 | Description of the energy counterpart of LogCA model                              | 64 |

# LIST OF FIGURES

| 2.1  | Description of the Roofline model [1]                                                                                                                      | 15 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.1  | Executing Advanced Encryption Standard (AES) [2] on different cryptographic accelerators. Break-even point (speedup of 1) represents the data at which the | 22 |

| 4.2  | accelerated version outperforms the unaccelerated one                                                                                                      | 22 |

|      | accelerator (below)                                                                                                                                        | 25 |

| 4.3  | A graphical description of the performance metrics                                                                                                         | 28 |

| 4.4  | Flowchart for calculating LogCA parameters                                                                                                                 | 36 |

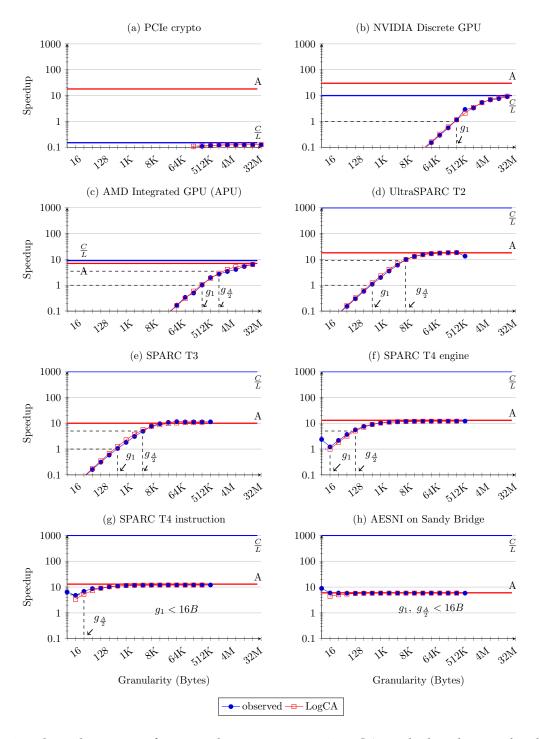

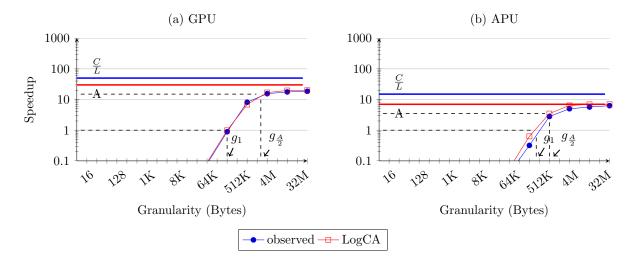

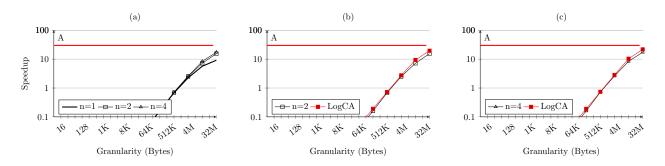

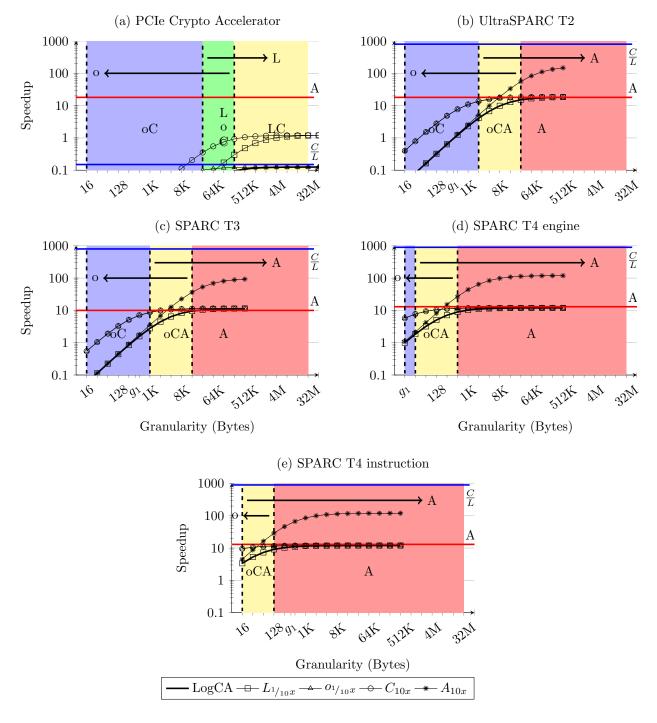

| 4.5  | Speedup curve fittings plots comparing LogCA with the observed values of AES [2] over a range of granularities. LogCA starts following observed values     |    |

|      | after 16B                                                                                                                                                  | 38 |

| 4.6  | Speedup curve fittings plots comparing LogCA with the observed values of SHA256 [3] over a range of granularities. LogCA starts following observed         |    |

|      | values after 64B                                                                                                                                           | 39 |

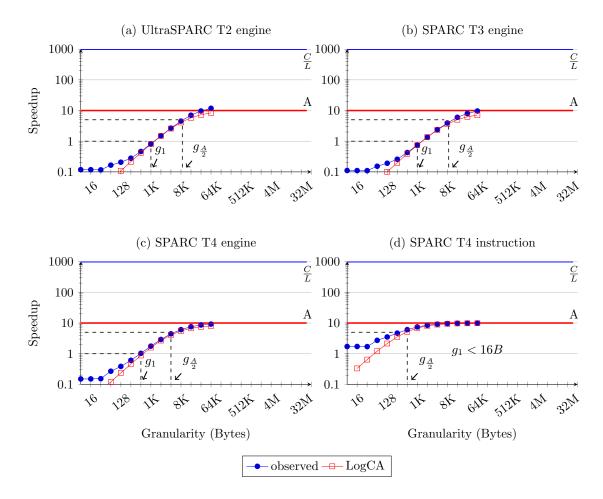

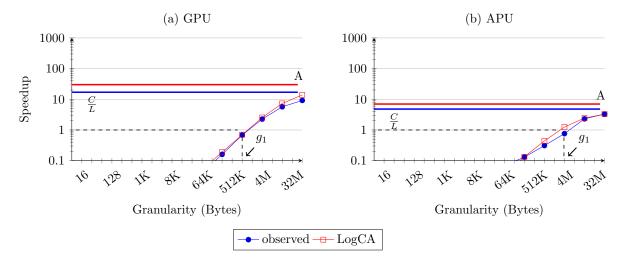

| 4.7  | Speedup curve fittings plots comparing LogCA with the observed values of Radix Sort over a range of granularities                                          | 40 |

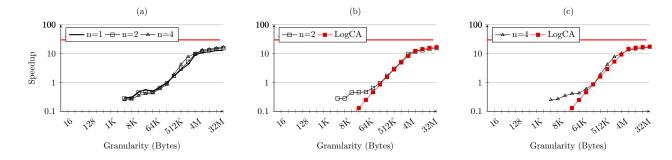

| 4.8  | Speedup curve fittings plots comparing LogCA with the observed values of                                                                                   |    |

| 4.9  | Matrix Multiplication over a range of granularities                                                                                                        | 42 |

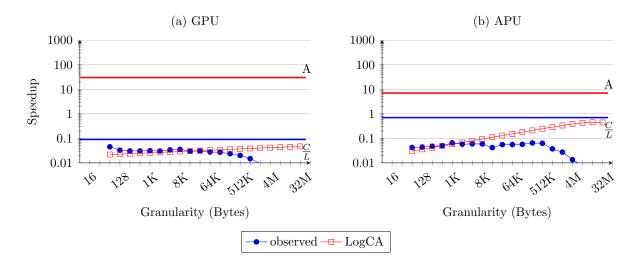

| 4.10 | over a range of granularities                                                                                                                              | 42 |

|      | Binary Search over a range of granularities                                                                                                                | 44 |

| 4.11 | $g_1$ for various encryption and hashing kernels on UltraSPARC T2                                                                                          | 44 |

|      | System configuration for multiple accelerators running in parallel                                                                                         | 45 |

|      | System configuration for multiple accelerators running in serial                                                                                           | 48 |

|      | Overlapping scenarios for pipelined execution of three computations on an accelerator. (a) The base case of an un-pipelined execution. Pipelined execution |    |

|      | when (b) overhead is higher than latency (c) overhead is smaller than latency                                                                              | 50 |

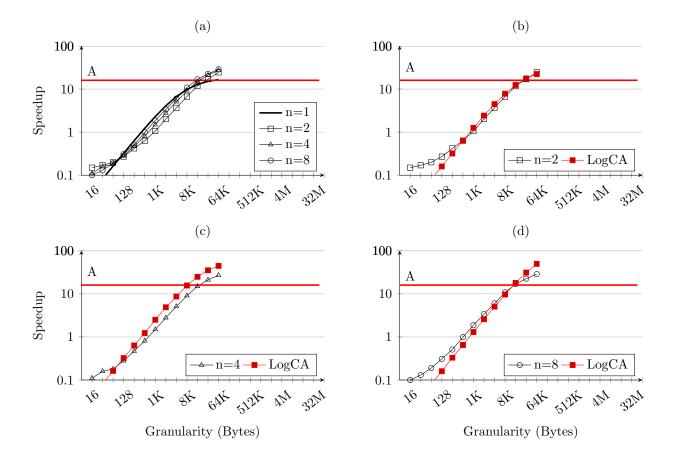

| 4.15 | Parallel execution of AES. (a) Comparing execution on multiple accelerators                     |    |

|------|-------------------------------------------------------------------------------------------------|----|

|      | with a single accelerator. Curve fitting of LogCA with the observed values while                |    |

|      | executing on (b) two (c) four and (d) eight accelerators                                        | 52 |

| 4.16 | Pipelined execution of matrix multiplication on a discrete GPU. (a) Comparing                   |    |

|      | pipelined and un-pipelined execution. Curve fitting of LogCA with the observed                  |    |

|      | values for pipelining (a) two and (b) four computations                                         | 55 |

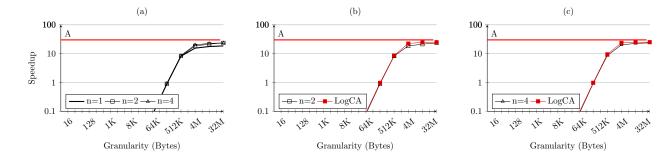

| 4.17 | Pipelined execution of FFT on a discrete GPU. (a) Comparing pipelined and                       |    |

|      | un-pipelined execution. Curve fitting of LogCA with the observed values for                     |    |

|      | pipelining (a) two and (b) four computations                                                    | 55 |

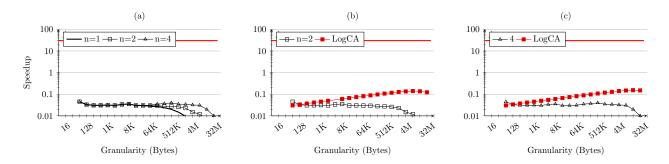

| 4.18 | Pipelined execution of radix sort on a discrete GPU. (a) Comparing pipelined                    |    |

|      | and un-pipelined execution. Curve fitting of LogCA with the observed values                     |    |

|      | for pipelining (a) two and (b) four computations                                                | 56 |

| 4.19 | Pipelined execution of binary search on a discrete GPU. (a) Comparing pipelined                 |    |

|      | and un-pipelined execution. Curve fitting of LogCA with the observed values                     |    |

|      | for pipelining (a) two and (b) four computations                                                | 56 |

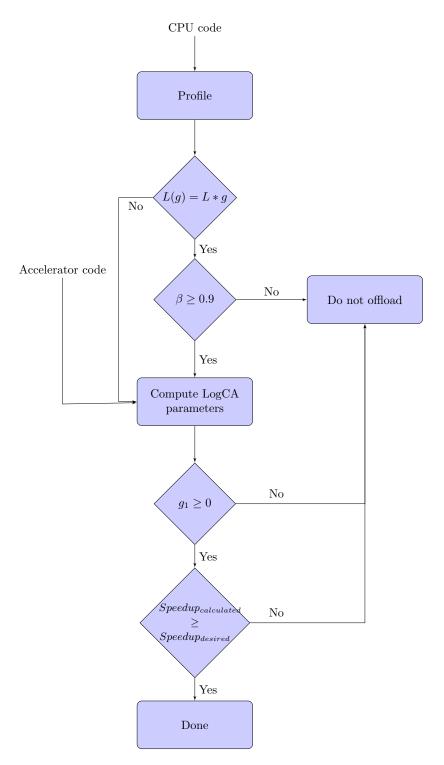

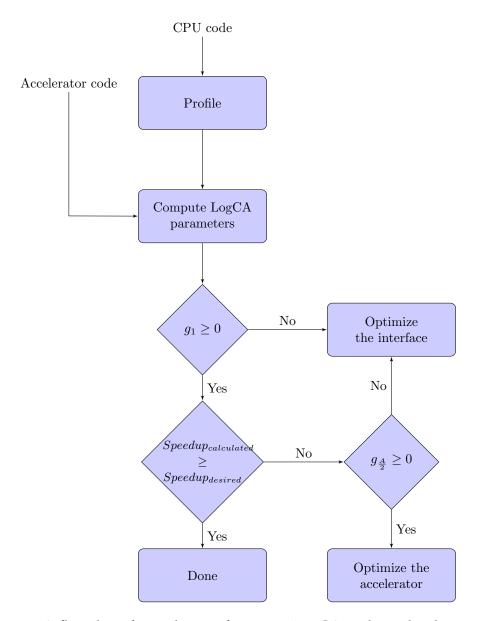

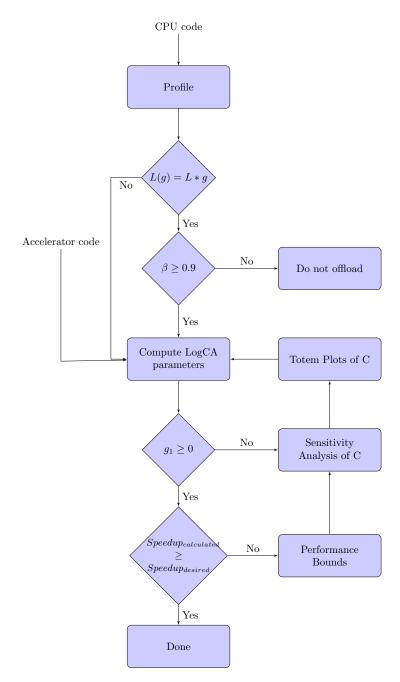

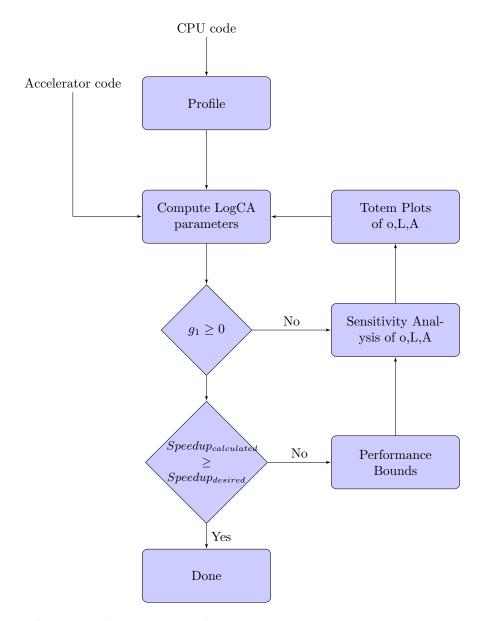

| 4.20 | A flowchart for programmers for using LogCA early in the design stage. $\ \ldots \ \ldots$      | 58 |

| 4.21 | A flowchart for architects for using LogCA early in the design stage                            | 60 |

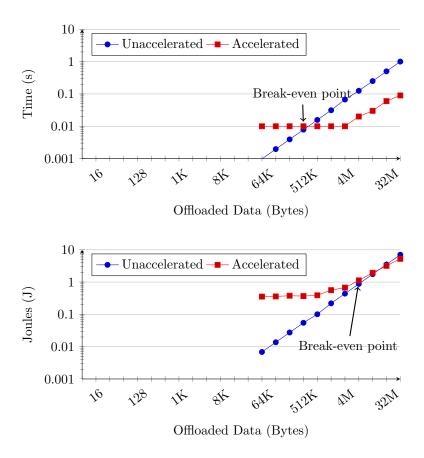

| 5.1  | Execution time (above) and energy (below) for running Advanced Encryption                       |    |

|      | Standard (AES) kernel on a discrete GPU                                                         | 63 |

| 5.2  | Energy consumption for the computation performed on the host (above) and                        |    |

|      | on an accelerator (below)                                                                       | 64 |

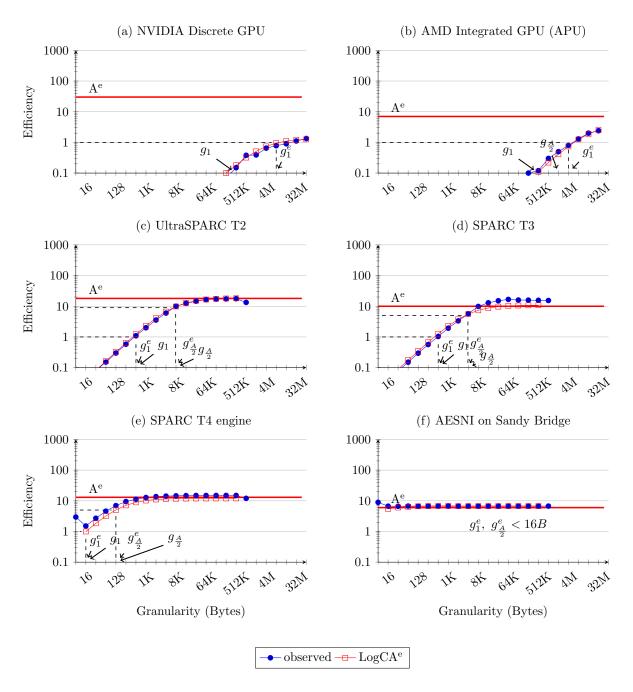

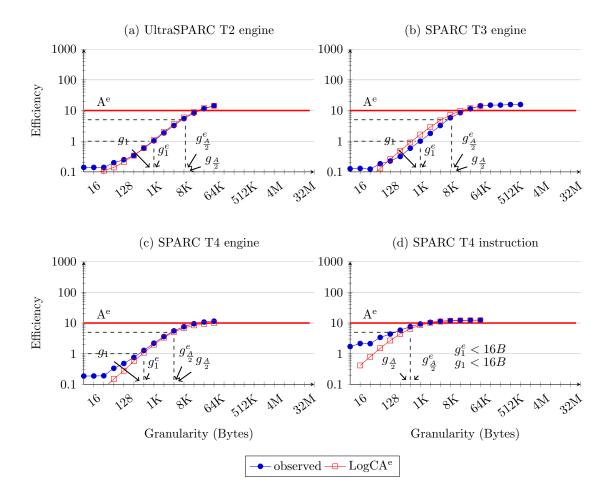

| 5.3  | Efficiency curve fittings plots comparing LogCA <sup>e</sup> with the observed energy of        |    |

|      | AES [2] over a range of granularities. Performance metrics $(g_1, g_{\frac{A}{2}})$ are also    |    |

|      | labelled for a comparison                                                                       | 69 |

| 5.4  | Efficiency curve fittings plots comparing LogCA <sup>e</sup> with the observed energy of        |    |

|      | SHA256 [3] over a range of granularities. Performance metrics $(g_1, g_{\frac{A}{2}})$ are also |    |

|      | labelled for a comparison                                                                       | 70 |

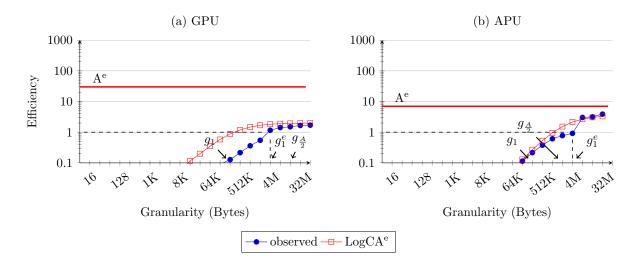

| 5.5  | Efficiency curve fittings plots comparing LogCA <sup>e</sup> with the observed energy of        |    |

|      | Radix Sort over a range of granularities. Performance metrics $(g_1, g_{\frac{A}{2}})$ are also |    |

|      | labelled for a comparison                                                                       | 72 |

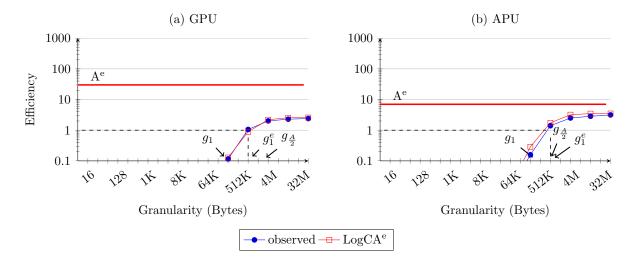

| 5.6 | Efficiency curve fittings plots comparing LogCA <sup>e</sup> with the observed energy of                                                                      |    |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | matrix multiplication over a range of granularities. Performance metrics ( $g_1$ ,                                                                            |    |

|     | $g_{\frac{A}{2}}$ ) are also labelled for a comparison                                                                                                        | 73 |

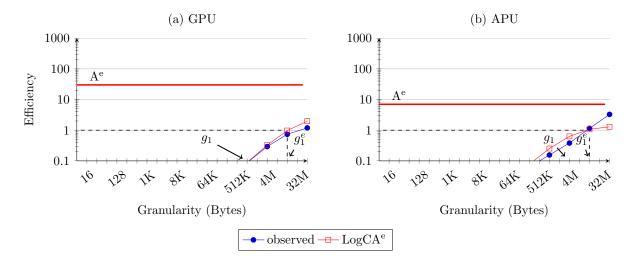

| 5.7 | Efficiency curve fittings plots comparing LogCA <sup>e</sup> with the observed energy of                                                                      |    |

|     | FFT over a range of granularities. Performance metric $(g_1)$ is also labelled for a                                                                          |    |

|     | comparison                                                                                                                                                    | 74 |

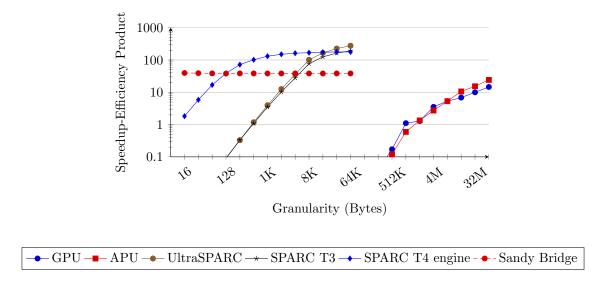

| 5.8 | Speedup-Efficiency Product (SEP) plot for AES on various accelerators                                                                                         | 74 |

| 5.9 | Speedup-Efficiency Product (SEP) plot for SHA on various accelerators                                                                                         | 75 |

| 6.1 | Running Advanced Encryption Standard (AES) kernel on three different crypto-                                                                                  |    |

|     | graphic accelerators                                                                                                                                          | 76 |

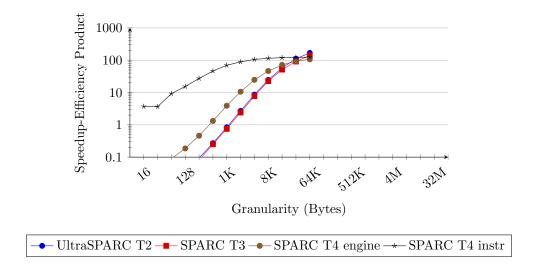

| 6.2 | Accelerometer helps in visually identifying (a) compute and (b) latency bound                                                                                 |    |

|     | kernels                                                                                                                                                       | 78 |

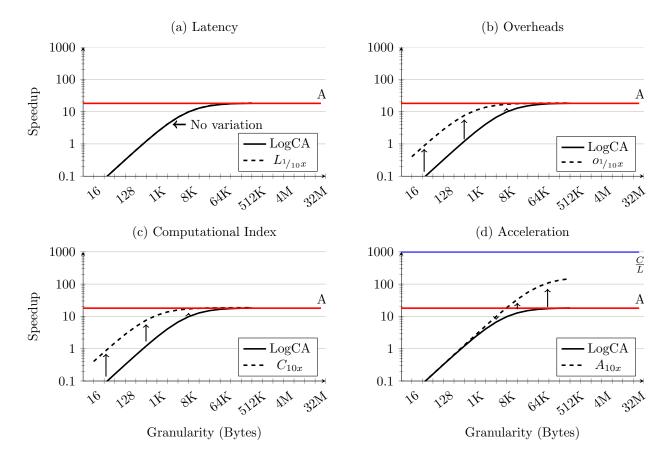

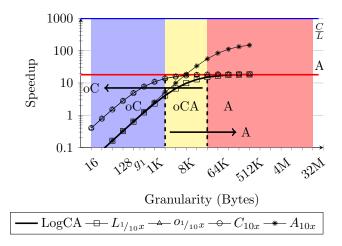

| 6.3 | The effect on speedup of 10x improvement in each LogCA parameter. The base                                                                                    |    |

|     | case is the speedup of AES [2] on UltraSPARC T2                                                                                                               | 82 |

| 6.4 | Optimization regions for UltraSPARC T2. The presence of a parameter in an                                                                                     |    |

|     | optimization region indicates that it can at least provides 20% gains. The hori-                                                                              |    |

|     | zontal arrow indicates the cut-off granularity at which a parameter provides                                                                                  |    |

|     | 20% gains                                                                                                                                                     | 83 |

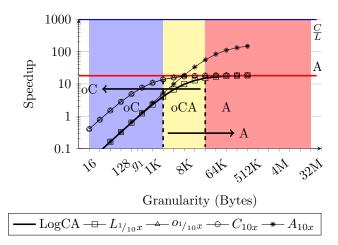

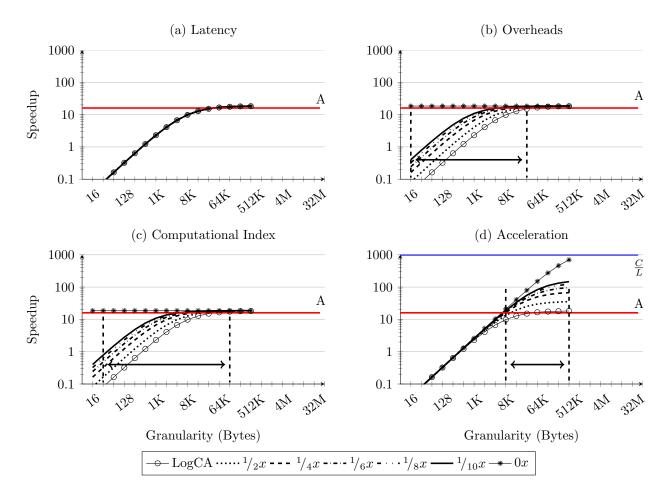

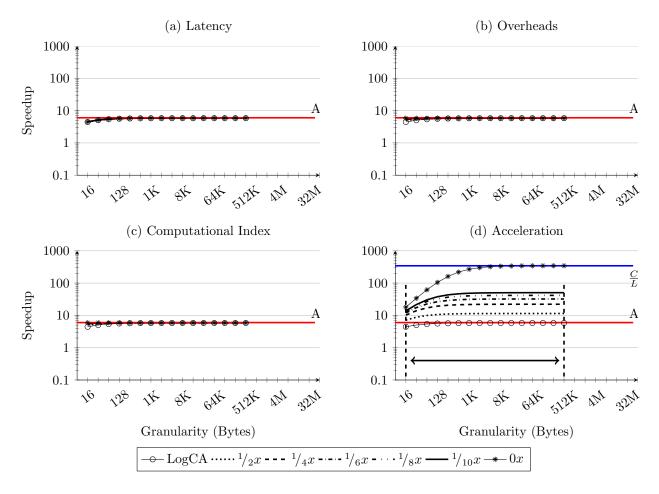

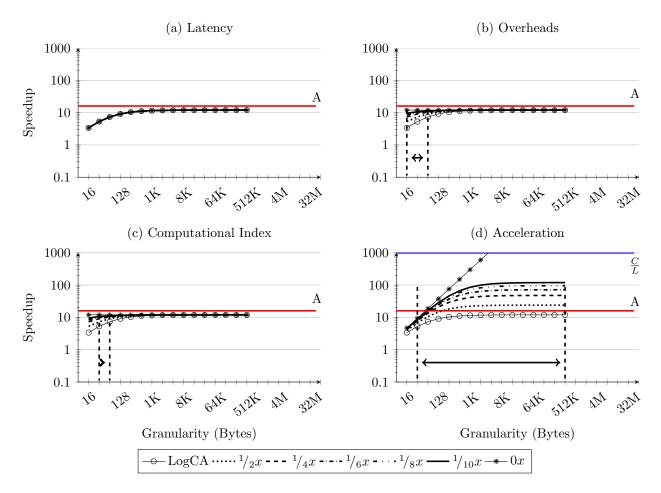

| 6.5 | Totem plots for AES on UltraSPARC T2. We vary each LogCA parameter from                                                                                       |    |

|     | 2x to 10x. We also consider the hypothetical case of decreasing (increasing) each                                                                             |    |

|     | parameter to zero (infinity)                                                                                                                                  | 84 |

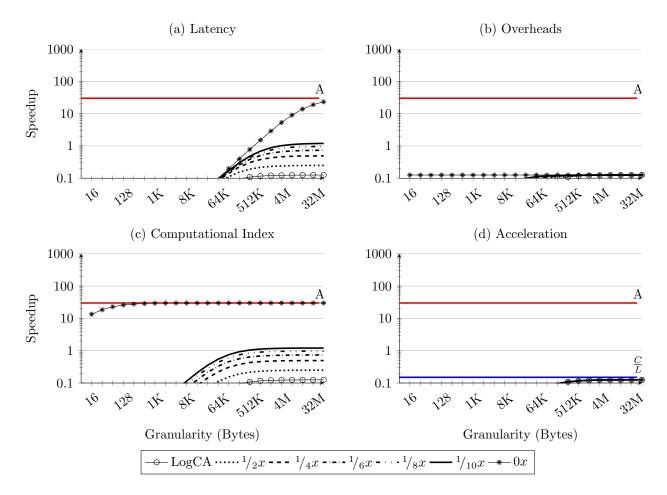

| 6.6 | Totem plots of AES on Sandy Bridge. We vary each parameter (a) Latency (b)                                                                                    |    |

|     | Overhead (c) Computation Index and (d) Acceleration, from 2x to 10x. We also consider the hypothetical case of decreasing (increasing) each parameter to zero |    |

|     | (infinity)                                                                                                                                                    | 86 |

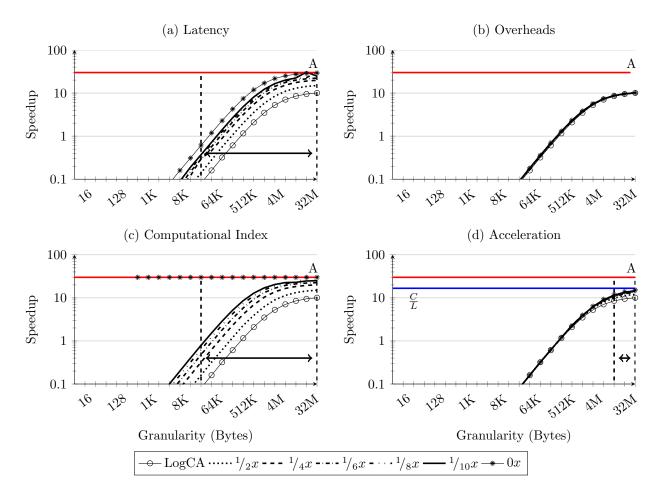

| 6.7 | Totem plots for AES on T4 instr. We vary each parameter (a) Latency (b) Over-                                                                                 |    |

|     | head (c) Computational index and (d) Acceleration, from 2x to 10x. We also                                                                                    |    |

|     | consider the hypothetical case of decreasing (increasing) each parameter to zero                                                                              |    |

|     | (infinity). The marked region indicates optimizations which provide at least                                                                                  |    |

|     | 20% gains                                                                                                                                                     | 87 |

|     | -                                                                                                                                                             |    |

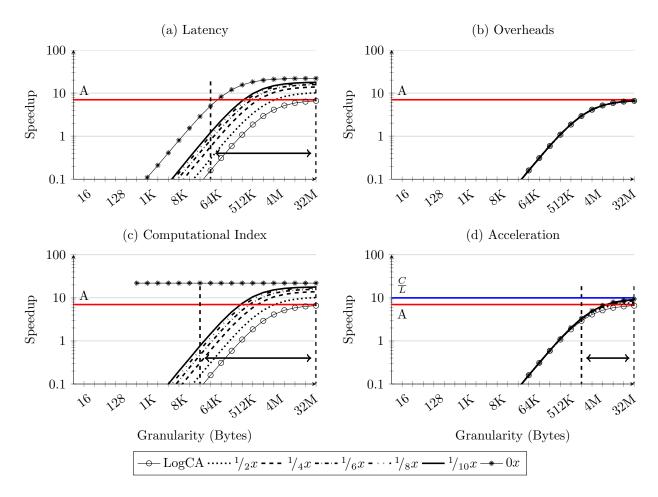

| 6.8  | Totem plots for AES on PCIe accelerator as we vary each LogCA parameter from      |     |

|------|-----------------------------------------------------------------------------------|-----|

|      | 2x to 10x. We also consider the hypothetical case of decreasing (increasing) each |     |

|      | parameter to zero (infinity). The marked region indicates optimizations which     |     |

|      | provide at least 20% gains                                                        | 88  |

| 6.9  | Totem plots of AES on NVIDIA GPU. We vary each parameter (a) Latency (b)          |     |

|      | Overhead (c) Computational index and (d) Acceleration, from 2x to 10x. We         |     |

|      | also consider the hypothetical case of decreasing (increasing) each parameter to  |     |

|      | zero (infinity)                                                                   | 89  |

| 6.10 | Totem plots of AES on AMD APU. We vary each parameter (a) Latency (b)             |     |

|      | Overhead (c) Computational index and (d) Acceleration, from 2x to 10x. We         |     |

|      | also consider the hypothetical case of decreasing (increasing) each parameter to  |     |

|      | zero (infinity)                                                                   | 90  |

| 6.11 | LogCA for performing Advanced Encryption Standard [2] on various crypto-          |     |

|      | graphic accelerators. LogCA identifies the design bottlenecks through LogCA       |     |

|      | parameters in an optimization region. The bottlenecks which LogCA suggests        |     |

|      | in each design is optimized in the next design                                    | 92  |

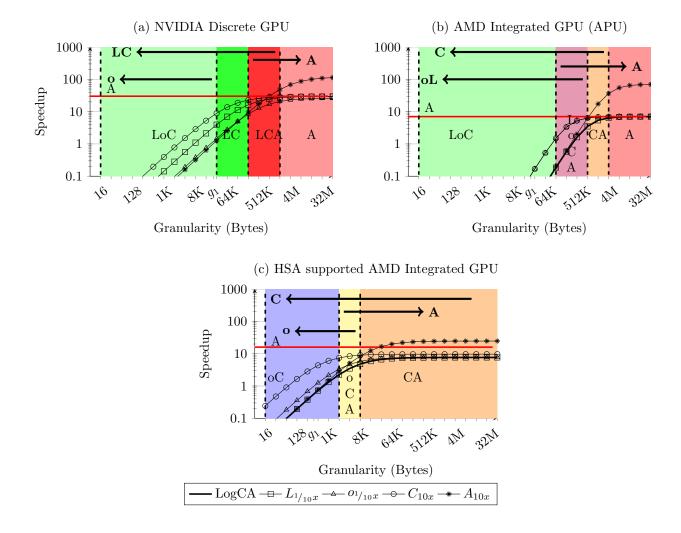

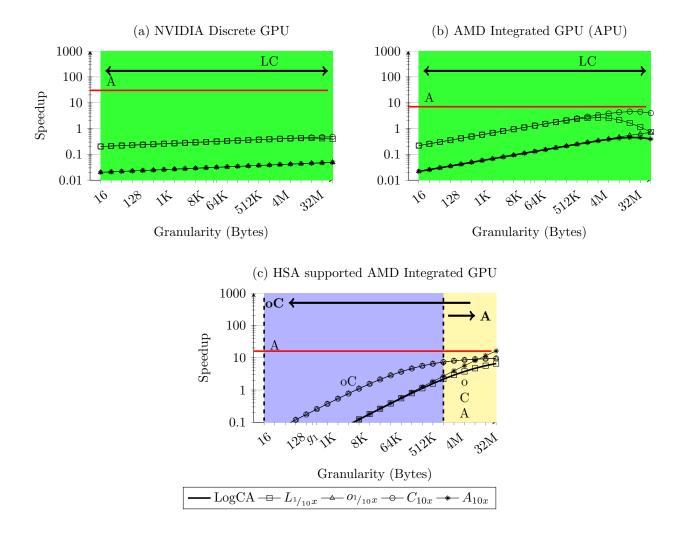

| 6.12 | Various optimization regions for matrix multiplication over a range of granular-  |     |

|      | ities on (a) NVIDIA discrete GPU, (b) AMD APU and (c) HSA Supported GPU.          |     |

|      |                                                                                   | 95  |

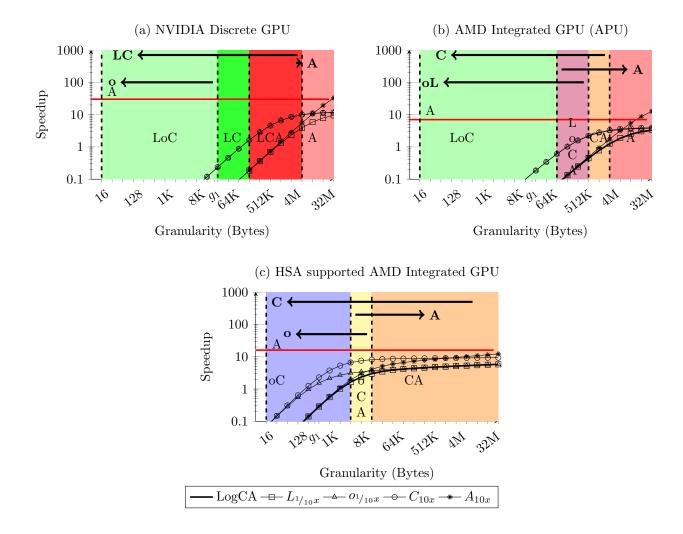

| 6.13 | Various Optimization regions for FFT over a range of granularities on (a) NVIDIA  |     |

|      | discrete GPU, (b) AMD APU and (c) HSA Supported GPU                               | 96  |

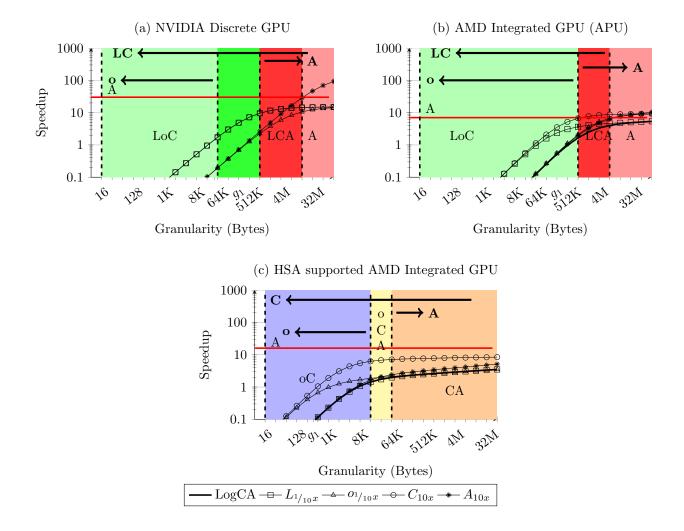

| 6.14 | Various Optimization regions for Radix Sort over a range of granularities on (a)  |     |

|      | NVIDIA discrete GPU, (b) AMD APU and (c) HSA Supported GPU                        | 97  |

| 6.15 | Various Optimization regions for Binary Search over a range of granularities on   |     |

|      | (a) NVIDIA discrete GPU, (b) AMD APU and (c) HSA Supported GPU                    | 98  |

| 6.16 | A flowchart for programmers for using Accelerometer with LogCA early in the       |     |

|      | design stage                                                                      | 101 |

| 6.17 | A flowchart for architects for using Accelerometer with LogCA early in the        |     |

|      | design stage                                                                      | 102 |

| 6.18 | Optimization regions for UltraSPARC T2. The presence of a parameter in an        |

|------|----------------------------------------------------------------------------------|

|      | optimization region indicates that it can at least provides 20% gains. The hori- |

|      | zontal arrow indicates the cut-off granularity at which a parameter provides     |

|      | 20% gains                                                                        |

#### ABSTRACT

With the end of Dennard scaling, architects have increasingly turned to special-purpose hardware accelerators to improve the performance and energy efficiency for some applications. Unfortunately, accelerators do not always live up to their expectations and may under-perform in some situations. Understanding the factors which effect the performance of an accelerator is crucial for both architects and programmers early in the design stage. Detailed models can be highly accurate, but often require low-level details which are not available until late in the design cycle. In contrast, simple analytical models can provide useful insights by abstracting away low-level system details.

In this dissertation, we aim to explore the potential of such simple models for hardware accelerators. To this end, we propose two complementary proposals. In our first proposal, we develop a simple analytical model, LogCA, to argue whether an accelerator is helpful for a given task or not. Once the usefulness of an accelerator is established, our second proposal, Accelerometer, helps in identifying bounds and bottlenecks associated with an accelerator design.

We validate our modeling framework across kernels of varying complexity on both on-chip and off-chip accelerators. We also describe the utility of our models using two retrospective case studies. First, we discuss the evolution of interface design in SUN/Oracle's encryption accelerators. Second, we discuss the evolution of memory interface design in three different GPU architectures. In both cases, we show that the adopted design optimizations for these machines are similar to the suggested optimizations. We argue that architects and programmers can use insights from these retrospective studies for improving future designs.

## 1 INTRODUCTION

In recent years, with increasing complexity of the computational systems, empirical methods are now needed to discover system limits and predict future behavior.

— Clayton Morrison and Richard Snodgrass,

Computer Science can use More Science [4]

Over the years, research and progress in the compute industry has been driven by the doubling of transistors every two years [5]—a phenomenon known as *Moore's law*. The trend of increasing transistor density and shrinking transistor sizes has been facilitated by *Dennard Scaling* [6], which has kept a chip's power consumption within acceptable limits. This growth has resulted in over billion of transistors on a chip [7] and this trend was expected to continue with *Moore's law*.

Unfortunately, with the breakdown of Dennard scaling, we have hit a *utilization wall* [8], resulting in an exponential decrease in the chip area operating at maximum frequency, with each new generation. This leads to the so-called problem of *Dark Silicon* [9, 10, 11, 12, 13] where some or most of the transistors on a chip have to be in-active, i.e., in a Dark state, to meet the power budget.

This failure of Dennard scaling over the last decade has inspired architects to introduce specialized functional units such as accelerators [14, 15]. These accelerators have shown considerable performance and energy improvement over general-purpose cores for some applications [8, 16, 17, 18, 19, 20, 21, 22]. In the server space, commercial processors already incorporate a variety of accelerators, ranging from encryption to compression, from video streaming to pattern matching, and from database query engines to graphics processing [23,

24, 25]. In the mobile space, we are also witnessing a consistent increase in the area of accelerators across generations. For example, more than 60% of the die area of Apple A8's SoC is dedicated to these accelerators [26]. Moreover, for a seamless integration of these accelerators, there are recent industrial efforts like IBM's Coherent Accelerator Processor Interface (CAPI) [27, 28] and Cache Coherent interconnect for Accelerators (CCIX) [29]. These efforts seek to develop coherent interfaces for achieving higher bandwidth and lower latencies while providing a uniform interface.

Unfortunately, despite these developments, accelerators do not always perform as expected [30, 31]. The gains from an accelerator, among others, depend on: 1) coupling with the host, i.e., whether an accelerator is part of pipeline, attached to a cache, memory or I/O bus, 2) granularity of the computation, i.e., instruction-level, kernel-level or application-level, and 3) overheads involved in transferring control and data from the host to an accelerator. Occasionally, these factors may offset the potential benefits of an accelerator, resulting in lower or no performance benefits.

With this uncertainty in the performance and expected ubiquitousness of accelerators in the future architectures [26], programmers and architects face these obvious questions: When not to use an accelerator? If using an accelerator, how much data to offload? What are the performance bounds associated with an accelerator design? Where to connect an accelerator in the system and how does it affect the gains? Does a performance-efficient solution guaranty energy efficiency and vice versa?

To answer these questions, programmers and architects can employ a number of existing performance analysis techniques. These techniques range from simple to complex analytical models and from functional to full-system simulation models [32, 33].

Complex modeling techniques, including full-system simulators [34, 35, 36] can provide

highly accurate performance estimates. However, this accuracy comes at the cost of long simulation times and low-level system details which are not available till late in the design cycle.

In contrast, analytical models—simpler ones in particular—abstract away these low-level system details using mathematical equations [37]. These equations help in understanding and analyzing complex systems by exposing the relationship among various design parameters and the sensitivity of the performance on these parameters without long simulation times. Consequently, providing key insights early in the design cycle that are useful for experts and non-experts alike.

Over the years, a number of simpler analytical models have been extremely useful in analyzing complex systems: Little's law [38] delineates the relationship between average wait time and number of waiting items in a system; Amdhal's law [39] provides theoretical limits for parallel computations; Hill and Marty [40] extends Amdhal's law for multi-core architectures; PRAM [41] and LogP [42] for parallel computations; Roofline explicates a bound and bottleneck analysis for the multi-core architectures [1], and recently Cache Calculus [43] for modeling cache performance.

The aforementioned models provide useful insights despite their simplicity. Therefore, in this dissertation we aim to explore the effectiveness of simple analytical models for hardware accelerators.

#### 1.1 Contributions

In this section, we briefly describe our main contributions.

# 1.1.1 LogCA: A High-Level Unified Performance and Energy Model for Hardware Accelerators

Despite the increasing trend towards heterogeneous architectures, the architecture community lacks a simple model to reason about accelerators. Such a model should help programmers and architects—early in the design cycle—in deciding whether an accelerator is helpful for a given task or not.

To this end, we propose LogCA—a unified performance and energy model for hardware accelerators—in Chapter 4 and 5. LogCA strikes a balance between too simple and too complex models. It provides useful insights for both programmers and architects by abstracting away the underlying architecture. With LogCA, we also formalize performance metrics for predicting the "right" amount of offloaded data and demonstrate that sub-linear and linear complexity algorithms are more sensitive to overheads and communication latencies than higher complexity algorithms. While the general trend may not be surprising, we argue that LogCA is accurate enough to answer important what-if questions very early in the design cycle.

While LogCA does not tell the architect how to design hardware to achieve those values, it can help him/her decide whether a given design will satisfy the high-level performance goals. For architects, we believe an important benefit of LogCA is the ability to formalize appropriate design goals for a new accelerator. History is replete with accelerators whose overheads were so high that they were rarely used, e.g., SuperSPARC I copy engine, Niagara

1 cryptographic accelerator, etc.

An earlier version of this work, encompassing the performance model with linear complexity kernels, appears in Computer Architecture Letters in June 2014 [44]. In this dissertation, we extend the performance model with a complementary energy model and kernels ranging from sub-linear to super-linear complexity. We also discuss the effect of pipelining and parallel execution on the performance.

#### 1.1.2 Accelerometer: A Sensitivity Analysis of the LogCA Parameters

Oftentimes LogCA justifies the use of an accelerator, however the gains from an accelerator are less than expected. In such scenarios, programmers and architects need to know the cause of bottlenecks and whether these bottlenecks need attention of a programmer or an architect.

To this end, we extend LogCA through a sensitivity analysis of its parameters and develop Accelerometer in Chapter 6. The sensitivity analysis helps in visually identifying performance bounds and bottlenecks. Furthermore, the identification of these bottlenecks provides an opportunity for optimization and Accelerometer demarcates these optimization opportunities through various optimization regions. With these optimization regions, programmers and architects can visually identify the potential gains associated with each optimization.

We demonstrate the utility of our model using two retrospective case studies. In the first case study, we consider the evolution of the interface in cryptographic accelerators on Sun/Oracle's SPARC T-series processors. For the second case, we consider the memory interface design in three different GPU architectures: a discrete, an integrated and a heterogeneous system architecture (HSA) supported GPU. In both cases, we show that

the adopted design optimizations for these machines are similar to the model's suggested optimizations. We argue that architects and programmers can use insights from these retrospective studies for improving future designs.

Parts of this work have been submitted for publication. In this dissertation, we include a thorough sensitivity analysis of the parameters for different complexity kernels.

# 1.2 Thesis Organization

In this dissertation, we provide a brief overview of the taxonomy of accelerators and discuss related work in Chapter 2. We describe our evaluation methodology and workloads in Chapter 3. We present our first proposal, LogCA, in Chapter 4. In Chapter 5, we complement the performance model with an energy model. Chapter 6 presents Accelerometer for identifying bounds and bottlenecks associated with an accelerator design. Finally, we conclude this dissertation in Chapter 7 with pointers to future work.

## 2 BACKGROUND AND RELATED WORK

This chapter compares and contrasts our work with the prior approaches for modeling accelerator architectures. With the availability of a broad range of accelerators, we find it pertinent to first define an accelerator.

#### 2.1 Accelerator Architectures

Patel and W. Hwu [14] define an accelerator as:

An accelerator is a separate architectural substructure (on the same chip, or on a different die) that is architected using a different set of objectives than the base processor, where these objectives are derived from the needs of a special class of applications. Through this manner of design, the accelerator is tuned to provide higher performance at lower cost, or at lower power, or with less development effort than with the general-purpose base hardware.

Based on this definition, the current breed of accelerators can be classified into various categories. Cascaval et al. [15] provide a taxonomy of these accelerators from an architecture and programming perspective. In this dissertation, we are mostly concerned with the architecture specific classification. Hence, we classify them in the following three categories.

**Fixed-Function Accelerators** provide the best performance per watt ratio at the cost of flexibility. They are implemented in ASICs or other custom logic and are favorable for frequently used application domains. Examples of these accelerators include: floating point units, cryptographic accelerators, compression accelerators, and database accelerators [25, 24].

**Reconfigurable Accelerators** provide maximum functional flexibility at the cost of performance. These accelerators are most suitable for those application domains which

are still in the prototyping phase. Accelerators designed using Field Programmable Gate Arrays (FPGAs) are the main examples of this class of accelerators. These accelerators are mostly connected through either PCIe [45] or QPI interface [46, 47]. Recently, there has been a growing interest in using these accelerators in the data centers [48, 49].

**Programmable Accelerators** provide better flexibility as compared to the fixed-function accelerators. They are more apt for application domains which are not mature or are going through continuous developments. Common examples include the graphics processing units (GPUs), general purpose GPUs (GPGPUs) and the programmable network interface controllers.

In this dissertation, our focus is on the effect of the interface in the design of accelerators. Since reconfigurable accelerators do not provide many options for the interface, we have primarily focused on the fixed-function and programmable accelerators. Although we have not validated our modeling framework for the reconfigurable accelerators, we believe that with the generality and abstraction our model provides, our modeling framework is equally applicable for the reconfigurable accelerators.

## 2.2 Analytical Models

There is a rich body of work exploring analytical models for prediction of an accelerator's performance [50]. For some models, the motivation is to determine the future trend in heterogeneous architectures [51, 52], and exploring the potential benefits associated with an accelerator [39, 53, 54, 55], whereas for others, the motivation is to determine the right amount of data to offload [56].

#### 2.2.1 Simple Modeling Frameworks

Using simplistic models to predict the performance of a machine has a long history [39, 40, 57, 58, 59, 60, 61, 62, 54, 42]. In the early days of parallel computing, *Amdahl's Law* [39] provided a simple model to predict the performance gains for parallel machines. The model argued that despite the number of parallel resources, the speedup is limited by the serial fraction of an algorithm. Hence, the speedup is given by

$$Speedup = \frac{1}{s + \frac{p}{N}} \tag{2.1}$$

where s is the time spent on the serial part of the program, p is the time spent on the part of the program that can be parallelized and N is the number of processors.

Over the years, Amdahl's law has been extended for various domains, ranging from multi-core architectures [40, 59, 62] to data-centers [60] and from energy-constrained environments [57, 61, 58] to heterogeneous architectures [54, 63].

To this end, Daga et al. [54] revisit Amdahl's law for accelerator-based architectures while analyzing the effectiveness of integrated GPUs over discrete GPUs. They argue that for discrete GPUs, data-copying overheads are high and can not be ignored. They factor in the overheads in the speedup computation, and the speedup is given by

$$Speedup = \frac{1}{s + p' + o} \tag{2.2}$$

where s is the serial fraction of the program, p' is the accelerated parallel fraction and o is the parallel overhead.

We present a similar simple model—LogCA—for accelerators. We argue that despite the peak performance of an accelerator, the achievable speedup is limited by the setup overheads and communication latencies. Our proposed model, LogCA, is inspired by LogP [42] which is a model for the design and analysis of algorithms for parallel machines.

With LogP, the goal was to develop a simple yet accurate model for parallel computation at a time when the available models were either too simplistic, i.e., zero communication latencies and infinite bandwidth, or too specific, i.e., applicable for a particular configuration of a machine. LogP was developed in an era when a diverse set of parallel machines were emerging and it was difficult to model each of them. To overcome this difficulty and provide a simple interface, LogP abstracted away the underlying details with four parameters. These four parameters represent communication bandwidth (g), communication overhead (o), communication delay (L), and the number of processors (P). We use a similar strategy of using system parameters for abstracting away the low-level details. LogCA retains the L and o parameters from LogP but as discussed in Chapter 4 its remaining three parameters focus on properties of an accelerator and the offloaded computation.

### 2.2.2 Early-Stage Modeling Frameworks

Chung et al. [51] in a detailed study predict the future landscape of heterogeneous computing. They extend the work of Hill and Marty [40] by incorporating power, bandwidth and scalability of the unconventional cores (U-cores)—a term they coined to encompass GPUs, FPGA and ASICs. They also include the ITRS roadmap in deriving parameters for their model. Conceptually, their U-core's efficiency parameter is similar to our Acceleration (A) parameter. Similar to our modeling framework, the main goal of this work is not to provide exact numbers but provide high-level ideas of the trade-offs involved in various design decisions.

In another work in early-stage modeling, Hempstead et al. [52] propose Navigo. Navigo

provides a compromise between back-of-the-envelope calculations and detailed simulators. The model takes technology node, input voltage, frequency, number of cores and market selection as inputs. A designer can then sweep across these inputs and observe the expected system output as throughput and power. Overall, Navigo provides an estimate about the amount of specialization required to maintain performance in power-constrained future architectures. In contrast, our early-stage framework helps architects reason about accelerators for a given task.

#### 2.2.3 Modeling Communication Cost

Oftentimes, performance models exclude communication cost while estimating performance on accelerators. However, similar to our model, various studies [64, 54, 53] argue that communication cost can not be ignored. To this end, Nilakantan et al. [64] incorporate communication cost for early-stage modeling of accelerator-rich architectures. Their analytical model also predicts the minimum accelerator area required to reach particular performance goal. Similarly, Daga et al. [54] show the overheads for communicating over the PCIe bus as a major bottleneck in exploiting the full potential of GPUs. They observe that integrated GPUs fail to deliver comparable performance as their discrete counterpart for memory-bound kernels because of the limited bandwidth.

Meswani et al. [53] explore such analytical models for high performance computing (HPC) applications. They argue that HPC applications' code size can be huge, resulting in years of development time. For these applications, it make sense to predict the performance gains before porting an application code to an accelerator. They divide an application into idioms—a particular computation or memory access pattern. Using micro-benchmarks, they evaluate the effect of data size on various idioms, e.g., streaming, gather scatter, stencil,

etc. They later predict the performance of an application by identifying the frequency of occurrence of an idiom in that application. This study is performed on high performance computing applications with GPUs and FPGAs as the target devices.

#### 2.2.4 Predicting Offloaded Data

The idea of offloading computationally intensive workloads to remote servers has been extensively studied for mobile networks. Kumar et al. [56] provide a detailed survey on models which tried to answer the basic question: when (and where) to offload the workloads. We define performance and energy metrics to answer a similar question. Unlike our modeling framework, these models for mobile networks do not provide insights for programmers and architects in designing either the interface or the remote servers.

#### 2.2.5 Performance Prediction on GPUs

A number of studies [65, 55, 66, 67, 68, 69, 70] have been performed for predicting performance on GPU architectures. These studies differ by the complexity of the model and the type of input code. We briefly discuss the most relevant below.

Hong et al. [65] develop an analytical performance model for predicting execution time on GPUs. The model requires the PTX code and uses the number of running threads and parallel memory requests. The authors later extend their model and develop an integrated power and performance model for GPUs [55]. They use the execution time from the earlier timing model to predict the power consumption. The power model also helps in predicting the number of cores to achieve optimal performance per watt.

Sim et al. [70] extend Hong et al.'s [65] work and develop an analytical model to help programmers predict the performance benefits from GPUs. Their model also helps in

identifying the potential bottlenecks and suggest optimizations to alleviate these bottlenecks. The model employs a number of architectural parameters to compute the execution time. From an optimization perspective, apart from thread-level parallelism, the model tries to exploit optimizations in instruction and memory-level parallelism. However, as a down-side it also requires the assembly code of the CUDA kernel.

Lai and Seznec [71, 68] develop TEG, Timing Estimation tool for GPUs, which is an analytical tool for estimating performance on GPUs. The model also helps in quantifying the bottlenecks. Similar to earlier approaches, TEG requires CUDA kernel assembly code and instruction trace for estimating the execution time.

Unlike earlier approaches, which require device specific code, GROPHECY [69] tries to predict the performance of a kernel on a GPU using the CPU code. The model defines a CPU code skeleton—an abstraction of the portion of the CPU code to be ported to the GPU—and use an analytical model to predict the execution time on GPUs.

In terms of goals, our work is closely related to the work of Zhang and Owens [67]. The authors have developed a micro-benchmark-based model for GPUs. The model identifies performance bottlenecks and helps programmers and architects predict performance on GPUs. The model is developed at an instruction and architectural level and determines the bottlenecks by breaking down the total execution time in the instruction pipeline, shared memory, and global memory. Unlike our approach, the model does not predict the potential benefits from these optimizations.

In contrast to studies that require understanding of the underlying architecture, Song et al. [66] use a simple counter-based approach augmented with machine learning to predict power and performance efficiency for GPUs. The model also helps in identifying bottlenecks and suggests optimizations to overcome them.

In general, our work is different from these studies because of the complexity. These models use a large number of parameters to accurately predict the power and/or performance, whereas we limit the number of parameters to reduce the complexity of our model. They also require deep understanding of the underlying architecture. Most of these models also require access to GPU specific assembly or PTX codes. Unlike these approaches, we use CPU code to provide bounds on the performance.

#### 2.3 Roofline Models

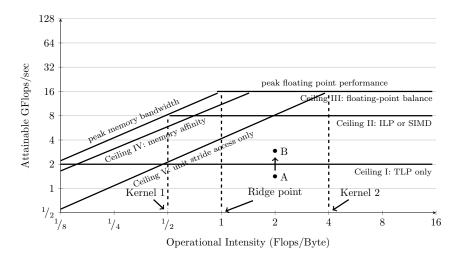

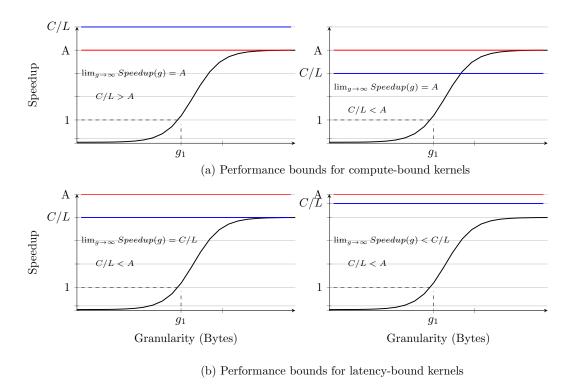

In terms of simplicity and motivation, our work in Chapter 6—Accelerometer—closely follows the Roofline model [1]—a visual performance model for multi-core architectures. For the Roofline model, the goal is not to predict the exact performance but provide insights about the relationship among various system parameters.

Roofline employs a "bound and bottleneck" analysis to provide useful insights about the expected performance of a system. It exposes inherent hardware limitations for a particular kernel and suggests several optimizations which programmers can use to fine tune that kernel on a given system.

To establish these bounds, Roofline limits the performance with the peak floating point performance and peak memory bandwidth. For a given system, the operating point of a kernel remains within these bounds (hence the name 'roofline'). The model defines the intersection of these two bounds as the *ridge point*. This point helps programmers and compiler writers understands how close they are to in achieving peak performance. The location of the operating point also helps in determining whether a kernel is compute bound or memory bound. For example, Kernel 1 in Figure 2.1 is memory bound while Kernel 2 is compute bound. Also bottlenecks in a design may limit a computation's performance way

below the peak performance. Roofline exposes these bottlenecks with performance *ceilings* and suggests various optimizations to reach these *ceilings* and ultimately the roof of the model.

Because of the effectiveness in providing useful insights, Roofline has been extended in the past for various architectures [72, 73, 74]. Below, we discuss some of them briefly.

Choi et al. [72] propose an energy-based counterpart of the Roofline. The model exposes the interplay of time, energy and power using algorithmic and architecture specific parameters. Among these parameters, the number of operations, concurrency, and memory traffic characterizes an algorithm, whereas per operation cost (time and energy) characterizes a particular machine. By considering time and energy simultaneously, this model provides a much broader picture to an algorithm designer.

In contrast to earlier approaches, the Boat Hull model [73] predicts the execution time without using the accelerator specific source code. The authors use their previous work on algorithm classification [75] to partition a given kernel into different classes. After

Figure 2.1: Description of the Roofline model [1].

classifying the kernel, the model generates a Roofline for each class. The authors validate the model for both GPUs and traditional multi-core architectures. Unlike Boat Hull, our classification is based on algorithmic complexity. We model complexity of the algorithms using the power-law.

Jia et al. [74] propose GPURoofline, a Roofline model for GPUs. Similar to the original Roofline model, GPURoofline targets programmers who are not expert GPU architects, but need help tuning kernels for a particular GPU architecture. They validate the model for both AMD and NVIDIA GPUs.

In a similar spirit to Roofline, Lai and Seznec [76] propose a model to provide an upper bound on the kernel performance on GPUs. The model identifies the architectural bottlenecks in the systems and scope of optimization for achieving peak performance. Similar to other modeling methodologies, the model requires GPU assembly code as an input.

Despite the similarities, unfortunately Roofline and its extensions can not be used for exposing design bottlenecks in an accelerator's interface for several reasons: First, the primary goal of these models has been to help programmers and compiler-writers write better code for a given system while providing no insights for architects. Second, performance gains for accelerators are measured in speedup while Roofline measures performance in terms of operations per bytes. And third, Roofline does not account for the communication cost of offloading data from the host to an accelerator. Our extension for *LogCA*, *Accelerometer*, is inspired by Roofline and is intended to address these shortcomings.

# 3 EVALUATION METHODOLOGY

This chapter describes the experimental setup and benchmarks for validating our models on real machines. We also discuss our methodology for measuring model parameters and performance metrics.

## 3.1 Experimental Setup

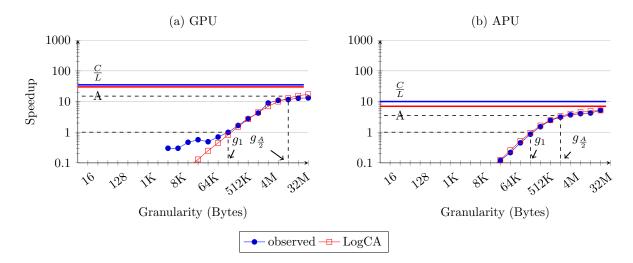

Our experimental setup comprises of on-chip and off-chip cryptographic accelerators (Table 3.2) and various GPUs (Table 3.3). The on-chip cryptographic accelerators include cryptographic units on Sun/Oracle UltraSPARC T2 [77], SPARC T3 [78], SPARC T4 [79] and AES-NI (AES New Instruction) [80] on Sandy Bridge, whereas the off-chip accelerator is a Hifn 7955 chip connected through the PCIe bus [81]. The GPUs include a discrete NVIDIA GPU, an integrated AMD GPU (APU), and a heterogeneous system architecture (HSA) supported integrated GPU [82].

For the on-chip cryptographic accelerators, each core in UltraSPARC T2 and SPARC T3 has a physically addressed cryptographic unit. These cryptographic units require privileged DMA calls for operation, which may incur overheads of thousands of cycles. However, the cryptographic unit on SPARC T4 is integrated within the pipeline and does not require privileged DMA calls. SPARC T4 also provides non-privileged cryptographic instructions to access the cryptographic unit, thus reducing the overheads. Similar to SPARC T4, Sandy bridge provides a non-privileged cryptographic instruction – AESNI – for encryption.

The discrete GPU is connected through the PCIe bus, whereas for the APU, the GPU is co-located with the host processor on the same die. For the APU, the system memory is

| Kernel                             | Algorithmic Complexity  |

|------------------------------------|-------------------------|

| Advanced Encryption Standard (AES) | $\mathcal{O}(n)$        |

| Secure Hashing Algorithm (SHA)     | $\mathcal{O}(n)$        |

| Matrix Multiplication (GEMM)       | $\mathcal{O}(n^3)$      |

| Fast Fourier Transform (FFT)       | $\mathcal{O}(n \log n)$ |

| Radix Sort                         | $\mathcal{O}(kn)$       |

| Binary Search                      | $\mathcal{O}(\log n)$   |

| Discrete Cosine Transform (DCT)    | $\mathcal{O}(n^2)$      |

Table 3.1: Algorithmic complexity of the kernels used in the evaluation

partitioned between host and GPU memory. This eliminates the PCIe bottleneck of data copying but still requires copying data between memories. In both cases, depending on the size of the data, a number of cycles are spent in copying the data from the host memory to device memory. Unlike discrete GPU and APU, HSA supported GPU provides a unified and coherent view of the system memory. With the host and GPU sharing the same virtual address space, explicit copying of data between memories is not required.

#### 3.2 Workloads

In this section, we describe the workloads we have used in our evaluation. We have selected our kernels to cover a diverse set of workloads. These kernels range from sub-linear to super-linear complexity algorithms. Table 3.1 list the algorithmic complexities of these kernels.

Our workloads consist of encryption, hashing and GPU kernels. For encryption and hashing kernels, we have used OpenSSL [83] – an open source cryptography library, and for GPU kernels, we have used AMD OpenCL SDK [84]. We also want to observe how speedup varies with the size of the offloaded data. To do that, we have modified our kernels to enable input size from 16B to 32MB.

# 3.3 Experimental Methodology

We have used Linux utilities to calculate the execution time on the cryptographic accelerators, whereas for the GPUs we have used NVIDIA and AMD OpenCL profilers to compute the setup, kernel and data transfer times. For our performance numbers, we report the average of one hundred executions. We have modified OpenSSL to enable the support for underlying hardware accelerators [85]. For verifying the usage of cryptographic accelerators, we have used built-in counters in UltraSPARC T2 and T3 [86]. SPARC T4, however, no longer supports these counters, so we have used Linux utilities to trace the execution of the cryptographic instructions [87].

We have measured the average power using "Watts up? PRO" power meter [88]. We compute energy by multiplying measured power by the execution time.

| <b>Crypto Accelerator</b> | PCIe      | UltraSPARC | SPARC      | SPARC        | Sandy      |

|---------------------------|-----------|------------|------------|--------------|------------|

|                           | Crypto    | T2         | T3         | <b>T4</b>    | Bridge     |

| Processor                 | AMD       | S2         | S2         | S3           | Intel Core |

|                           | A8-3850   |            |            |              | i7-2600    |

| Frequency GHz             | 2.9       | 1.16       | 1.65       | 3            | 3.4        |

| Caches                    | L1: 24K   | L1: 8K     | L1: 8K     | L1: 16K      | L1: 64K    |

|                           | L2: 4M    | L2: 4M     | L2: 6M     | L2: 128K     | L2: 256K   |

| OpenSSL version           | 0.98o     | 0.98o      | 0.980      | 1.02, 1.0.1k | 0.98o      |

| Kernel                    | Ubuntu    | Oracle     | Oracle     | Oracle       | Linux      |

|                           | 3.13.0-55 | Solaris 11 | Solaris 11 | Solaris 11.2 | 2.6.32-504 |

Table 3.2: Description of the Cryptographic accelerators

| Platform              | NVIDIA           | AMD              | AMD                 |

|-----------------------|------------------|------------------|---------------------|

|                       | Discrete GPU     | APU              | HSA                 |

| Name                  | Tesla C2070      | Radeon HD 6550   | Radeon R7           |

| Architecture          | Fermi            | Beaver Creek     | Kaveri              |

| Stream Processors     | 16               | 5                | 8                   |

| Compute Units         | 448              | 400              | 512                 |

| Device Memory         | 6G               | 1G               | 4G                  |

| Peak Core Clock Freq. | 1.5 GHz          | 600 MHz          | 720 MHz             |

| Peak FLOPS            | 1 T              | 480 G            | 856 G               |

| Host:                 |                  |                  |                     |

| Processor             | Intel            | AMD              | AMD                 |

|                       | Xeon E5520       | A8-3850          | A10-7850K           |

| Frequency GHz         | 2.27             | 2.9              | 1.7                 |

| Cache                 | L1: 32K L2: 256K | L1: 24K L2: 4M   | L1: 16K L2: 2M      |

|                       | L3: 8M           |                  |                     |

| Kernel                | Linux 2.6.32-504 | Ubuntu 3.13.0-55 | Ubuntu 4.0.0-040050 |

Table 3.3: Description of the GPUs

# 4 LOGCA: A HIGH-LEVEL PERFORMANCE MODEL

### FOR HARDWARE ACCELERATORS

The most that can be expected from any model is that it can supply a useful approximation to reality: All models are wrong; some models are useful.

— George Box

### 4.1 Introduction

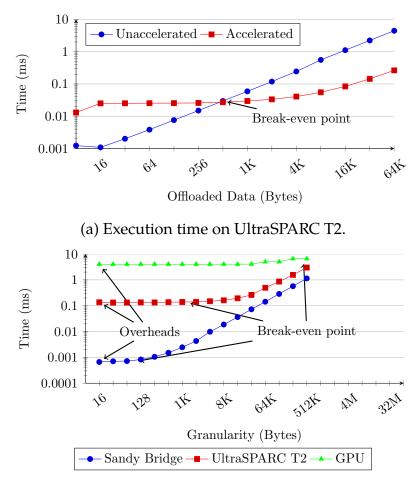

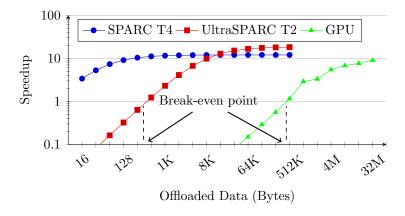

Earlier, we defined an accelerator as a specialized component for providing performance and energy efficiency. Unfortunately, accelerators do not always live up to their name or potential. Offloading a kernel to an accelerator incurs latency and overhead that depends on the amount of offloaded data, location of the accelerator, and its interface with the system. In some cases, these factors may outweigh the potential benefits, resulting in lower than expected or — in the worst case — no performance gains (speedup). Figure 4.1 illustrates such an outcome for the cryptographic accelerator in UltraSPARC T2 running the Advanced Encryption Standard (AES) kernel [2].

Figure 4.1 provides two key observations: First, accelerators can under-perform as compared to a general-purpose core, e.g., the accelerated version in UltraSPARC T2 outperforms the unaccelerated one only after crossing a threshold block size, i.e., the break-even point (Figure 4.1-a); second, different accelerators – while executing the same kernel – have different break-even points and overheads. For example, Sandy Bridge breaks even for smaller offloaded data while UltraSPARC T2 and GPU break even for large offloaded data

(b) Variation in overheads and break-even points for different cryptographic accelerators.

Figure 4.1: Executing Advanced Encryption Standard (AES) [2] on different cryptographic accelerators. Break-even point (speedup of 1) represents the data at which the accelerated version outperforms the unaccelerated one.

#### (Figure 4.1-b).

We also observe that a light-weight accelerator, like Sandy Bridge, breaks-even for a smaller offloaded data. It incurs low overheads but provides lesser gains. On the other hand, a heavy-weight accelerator, like a GPU, provides substantial gains at the cost of high overheads and large offloaded data. While offloading large data to get gains may seem a possible solution, applications may have a restriction on the amount of data that can be

offloaded. This is one of the challenges an architect may face in the design and placement of an accelerator.

Understanding the factors which dictate the performance of an accelerator are crucial for both architects and programmers. Programmers need to be able to predict when offloading a kernel will be performance-efficient. Similarly, architects need to understand how the accelerator's interface — and the resulting latency and overheads to offload a kernel — will affect the achievable accelerator performance.

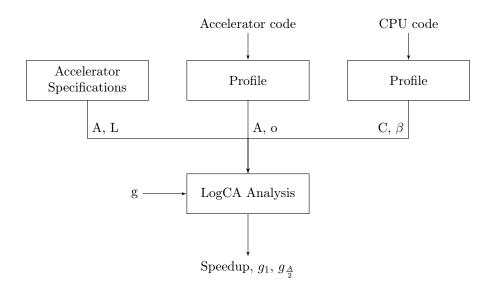

To address these issues, we propose LogCA, a performance model for hardware accelerators. LogCA derives its name from the five parameters listed in Table 4.1. These parameters characterize the communication latency (L) and overheads (o) of the accelerator interface, the granularity or size (g) of the off-loaded data, the complexity (C) of the computation, and the accelerator's peak performance improvement (A) as compared to a general purpose core.

LogCA is inspired by LogP [42], the well-known parallel computation model. LogP sought to find the right balance between overly simple models (e.g., PRAM) and the detailed reality of modern parallel systems. LogCA seeks to strike the same balance for hardware accelerators, providing sufficient simplicity such that programmers and architects can easily reason with it. Just as LogP was not the first model of parallel computation, LogCA is not the first model for hardware accelerators [50]. With LogCA, our goal is to develop a simple model that supports the important implications (§4.2) of our analysis using as few parameters as possible while providing sufficient accuracy. In Einstein's words, we want our model to be as simple as possible and no simpler.

The rest of the chapter is organized as follows. We develop our model and discuss the resulting implications in Section 4.2. We describe our methodology for calculating model

parameters in Section 4.3, and discuss the results in Section 4.4. Section 4.6 delineates how programmers and architects use LogCA, and we conclude with a summary in Section 4.7.

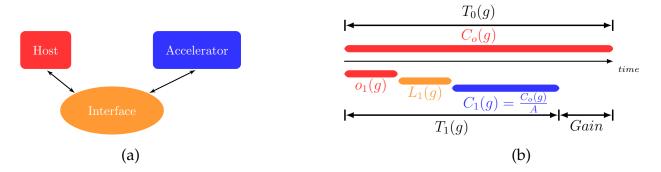

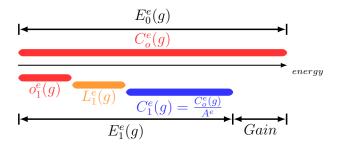

# 4.2 The LogCA Model

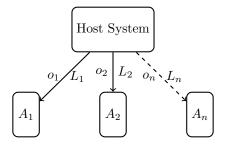

LogCA assumes an abstract system with three components (Figure 4.2 (a)): *Host* is a general-purpose processor; *Accelerator* is a hardware device designed for the efficient implementation of an algorithm; and *Interface* connects the host and accelerator abstracting away system details including the memory hierarchy.

Our model uses the interface abstraction to provide intuition for the overhead and latency of dispatching work to an accelerator. This abstraction enables modeling of different paradigms for attaching accelerators – directly connected, system bus or PCIe. This also gives the flexibility to use our model for both on-chip and off-chip accelerators. This abstraction can also be trivially mapped to shared memory systems or other memory hierarchies in heterogeneous architectures. The model further abstracts the underlying architecture using the five parameters defined in Table 4.1.

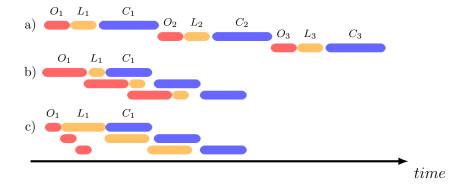

Figure 4.2 (b) illustrates the overhead and latency model for an un-pipelined accelerator where computation 'i' is returned before requesting computation 'i + 1'. Figure 4.2 (b) also shows the breakdown of time for an algorithm on the host and accelerator. We assume that the algorithm's execution time is a function of granularity, i.e., the size of the offloaded data. With this assumption, the unaccelerated time  $T_0$  (time with zero accelerators) to process data of *granularity* g, will be

$$T_0(g) = C_0(g)$$

(4.1)

| Parameter           | Symbol | Description                                                                                                 | Units       |

|---------------------|--------|-------------------------------------------------------------------------------------------------------------|-------------|

| Latency             | L      | Cycles to move data from the host<br>to the accelerator across an un-<br>pipelined interface, including the | Cycles      |

|                     |        | cycles data spends in the caches or memory                                                                  |             |

| Overhead            | O      | Cycles the host spends in setting up the algorithm                                                          | Cycles      |

| Granularity         | g      | Size of the offloaded data                                                                                  | Bytes       |

| Computational Index | Č      | Cycles the host spends per byte of data                                                                     | Cycles/Byte |

| Acceleration        | A      | The peak speedup of an accelerator                                                                          | N/A         |

Table 4.1: Description of the LogCA model.

Figure 4.2: Top level description of the LogCA model (a) Shows the various components (b) Time-line for the computation performed on the host (above) and on an accelerator (below)

where  $C_0(g)$  is the computation time on the host.

When the data is offloaded to an accelerator, the new execution time  $T_1$  (time with one accelerator) is

$$T_1(g) = O_1(g) + L_1(g) + C_1(g)$$

(4.2)

where  $O_1(g)$  is the host overhead time in offloading 'g' bytes of data to the accelerator,  $L_1(g)$  is the interface latency and  $C_1(g)$  is the computation time in the accelerator to process data of granularity g.

To make our model more concrete, we make several assumptions. We assume that an accelerator with acceleration 'A' can decrease, in the absence of overheads, the algorithm's computation time on the host by a factor of 'A', i.e., the accelerator and host use algorithms with the same complexity. Thus, the computation time on the accelerator will be  $C_1(g) = \frac{C_0(g)}{A}$ . This reduction in the computation time results in performance gains, and we quantify these gains with speedup, the ratio of the un-accelerated and accelerated time:

$$Speedup(g) = \frac{T_0(g)}{T_1(g)} = \frac{C_0(g)}{O_1(g) + L_1(g) + C_1(g)}$$

(4.3)

We assume that the computation time is a function of the computational index 'C' and granularity, i.e.,  $C_0(g) = C * f(g)$ , where f(g) signifies the complexity of the algorithm. We also assume that f(g) is power function of 'g', i.e.,  $\mathcal{O}(g^\beta)$ . This assumption results in a simple closed-form model and bounds the performance for a majority of the prevalent algorithms in the high-performance computing community [89].

The above assumption works well for modeling a variety of kernels, ranging from sub-linear ( $\beta < 1$ ) to super-linear ( $\beta > 1$ ) complexities. However, this assumption may not work well for logarithmic complexity algorithms, i.e.,  $\mathcal{O}(\log(g))$ ,  $\mathcal{O}(g\log(g))$ . This is because, asymptotically, there is no function which grows slower than a logarithmic function. Despite this limitation, we observe that—in the granularity range of our interest—LogCA can also bound the performance for logarithmic functions.

For many algorithms and accelerators, the overhead is independent of the granularity, i.e.,  $O_1(g) = o$ . Latency, on the other hand, will often be granularity dependent, i.e.,  $L_1(g) = L*g$ . Latency may be granularity independent if the accelerator can begin operating when the first byte (or block) arrives at the accelerator, i.e.,  $L_1(g) = L$ . Thus, LogCA can also model pipelined interfaces using granularity dependent latency assumption.

We define *computational intensity*<sup>1</sup> as the ratio of computational index to latency, i.e.,  $\frac{C}{L}$  and it signifies the amount of work done on a host per byte of offloaded data. Similarly, we define *accelerator's computational intensity* as the ratio of computational intensity to acceleration, i.e.,  $\frac{C/A}{L}$  and it signifies the amount of work done on an accelerator per byte of offloaded data.

For simplicity, we begin with the assumption of granularity independent latency. We revisit granularity dependent latencies later (§ 4.2.3). With these assumptions,

$$Speedup(g) = \frac{C * f(g)}{o + L + \frac{C * f(g)}{A}} = \frac{C * g^{\beta}}{o + L + \frac{C * g^{\beta}}{A}}$$

(4.4)

The above equation shows that the speedup is dependent on LogCA parameters and these parameters can be changed by architects and programmers through algorithmic and design choices. An architect can reduce the *latency* by integrating an accelerator more closely with the host. For example, placing it on the processor die rather than on an I/O bus. An architect can also reduce the *overheads* by designing a simpler interface, i.e., limited OS intervention and address translations, lower initialization time and reduced data copying between buffers (memories), etc. A programmer can increase the *computational index* by increasing the amount of work per byte offloaded to an accelerator. For example, kernel fusion [90, 91]—where multiple computational kernels are fused into one—tends to increase the *computational index*. Finally, an architect can typically increase the *acceleration* by investing more chip resources or power to an accelerator.

<sup>&</sup>lt;sup>1</sup>not to be confused with operational intensity [1], which signifies operations performed per byte of DRAM traffic.

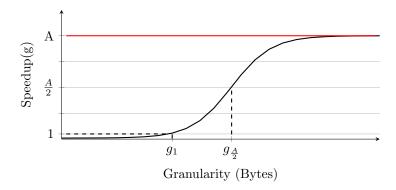

Figure 4.3: A graphical description of the performance metrics

### 4.2.1 Effect of Granularity

A key aspect of LogCA is that it captures the effect of granularity on the accelerator's speedup. Figure 4.3 shows this behavior, i.e., speedup increases with granularity and is bounded by the acceleration 'A'. At one extreme, for large granularities, equation (4.4) becomes,

$$\lim_{g \to \infty} Speedup(g) = A \tag{4.5}$$

While for small granularities, equation (4.4) reduces to:

$$\lim_{g \to 0} Speedup(g) \simeq \frac{C}{o + L + \frac{C}{A}} < \frac{C}{o + L}$$

(4.6)

Equation (4.6) is simply *Amdahl's Law* [39] for accelerators, demonstrating the dominating effect of overheads at small granularities.

### 4.2.2 Performance Metrics

To help programmers decide when and how much computation to offload, we define two performance metrics. These metrics are inspired from the vector machine metrics  $N_v$  and

$N_{1/2}$ [92], where  $N_v$  is the vector length to make vector mode faster than scalar mode and  $N_{1/2}$  is the vector length to achieve half of the peak performance. Since vector length is an important parameter in determining performance gains for vector machines, these metrics characterize the behavior and efficiency of vector machines with reference to scalar machines. Our metrics tend to serve the same purpose in the accelerator domain.