### Energy-efficient Communication Architectures for beyond von-Neumann AI Accelerators: Design and Analysis

by

#### Sumit K. Mandal

A dissertation submitted in partial fulfillment of the requirements for the degree of

#### Doctor of Philosophy

(Department of Electrical and Computer Engineering)

#### at the

#### UNIVERSITY OF WISCONSIN-MADISON

2022

Date of final oral examination: 04/22/2022

The dissertation is approved by the following members of the Final Oral Committee:

Umit Y. Ogras, Associate Professor, Electrical and Computer Engineering, University of Wisconsin-Madison

Mikko H. Lipasti, Professor, Electrical and Computer Engineering, University of Wisconsin-Madison

Karu Sankaralingam, Professor, Computer Sciences Engineering, University of Wisconsin-Madison

Chaitali Chakrabarti, Professor, Electrical Engineering, Arizona State University

| • |

|---|

| 1 |

Dedicated to my parents Abha Mondal and Sasthi Pada Mandal.

This dissertation is the result of efforts over the last five years of my graduate study and over 20 years of education. The last five years have been one of the most productive phase of my life and it would not have been possible without the support of faculty, colleagues, friends, and family. First and foremost, I would like to thank my advisor, Prof. Umit Y. Ogras, for the guidance, patience, and advice he has offered me over the years of my graduate study. His insightful recommendations on writing, time management, communication, and networking helped me grow as a researcher and person. I am also grateful for his help and support in my academic job search. His thoughtful comments and advice on the interview process helped me greatly in securing an academic position. Prof. Ogras did everything to ensure his students' success, which is something I will strive to achieve in my career.

I would like to thank Prof. Chaitali Chakrabarti, Prof. Mikko H. Lipasti and Prof. Karthikeyan Sankaralingam for being part of my Ph.D. defense committee. Their insightful comments helped me in improving this dissertation. I am also thankful to Prof. Partha Pratim Pande, Prof. Janardhan Rao Doppa, Prof. Prabhat Mishra, Prof. Yu Cao, Prof. Jae-sun Seo, and Prof. Sudip Pasricha for their inputs and guidance in my research over the past few years. I am also thankful to Dr. Michael Kishinevsky and Dr. Raid Ayoub for their continued mentorship.

I am grateful for the interesting discussions, words of encouragement, and lighter moments with friends and colleagues: Ujjwal, Ganapati, Samet, Manoj, Darshan, Ranadeep, Anish, Yigit, Sizhe, Alper, Toygun, Shruti, Jie, Harsh and Gokul. I also like to thank my other friends for their continuous encouragement and support: Priyabrata, Siddhartha, Gaurav, Subarna, Sudhir and Sanvi. I enjoyed the numerous trips that I took with them.

Finally, I would like to thank my parents, Abha Mondal and Sasthi

Pada Mandal, for their constant love, support, and encouragement over the years. It is their love and encouragement that motivated me to pursue graduate studies and contribute to research. I also thank my cousins and friends back in India, with whom I have numerous happy moments.

#### **CONTENTS**

List of Tables vi

List of Figures viii

Abstractxvii

- **1** Introduction 1

- **2** Literature Review 7

- 2.1 Energy-efficient Communication Architectures for General Purpose Processors 7

- 2.2 Communication-centric AI Accelerator Design 15

- 2.3 Analytical Performance Modeling of Networks-on-Chip 20

- 3 Communication-Aware Hardware Accelerators for Deep Neural Networks (DNNs) 25

- 3.1 Background and Motivation 25

- 3.2 Area-aware NoC Optimization 33

- 3.3 Latency-aware NoC optimization 36

- 3.4 Experimental Evaluation 54

- 4 Communication-Aware Hardware Accelerators for Graph Convolutional Networks (GCNs) 68

- 4.1 Background and Motivation 68

- 4.2 The Proposed COIN Architecture 75

- 4.3 Experimental Evaluation 83

- 5 Performance Analysis of Priority-Aware NoCs101

- 5.1 Background and Motivation 101

- 5.2 Proposed Network Transformations 105

- 5.3 Generalization for Arbitrary Number of Queues112

- 5.4 Experimental Evaluations 115

- 6 Performance Analysis of NoCs with Bursty Traffic126

- 6.1 Background and Motivation 126

- 6.2 Proposed Approach to Handle Bursty Traffic 128

- 6.3 Experimental Results with Bursty Traffic134

- 7 Performance Analysis of NoCs with Deflection Routing 139

- 7.1 Background and Motivation 139

- 7.2 Proposed Superposition-based Approach 144

- 7.3 Experimental Results with Deflection Routing 154

- 8 Performance Analysis of NoCs with Weighted Round Robin Arbitration 161

- 8.1 Background and Motivation 161

- 8.2 Proposed Methodology and Approach167

- 8.3 Experimental Results 180

- 9 Conclusion of the Thesis and Future Work188

Bibliography 190

#### LIST OF TABLES

| 2.1 | Comparison of prior research and our novel contribution          | 24  |

|-----|------------------------------------------------------------------|-----|

| 3.1 | Summary of the notations used in this work                       | 39  |

| 3.2 | Schedules for $N_k = N_{k+1} \ldots \ldots \ldots \ldots \ldots$ | 45  |

| 3.3 | Schedules for $N_k < N_{k+1} \ldots \ldots \ldots \ldots$        | 48  |

| 3.4 | Schedules for $N_k > N_{k+1} \ldots \ldots \ldots \ldots$        | 49  |

| 4.1 | Properties for different GCN datasets                            | 83  |

| 4.2 | Summary of circuit level and NoC parameters                      | 83  |

| 4.3 | Comparison of Percentage Contribution of Communication           |     |

|     | Energy (%)                                                       | 90  |

| 4.4 | Comparison with Nvidia Quadro RTX-8000 GPU                       | 93  |

| 4.5 | Configuration of the edge devices considered                     | 93  |

| 4.6 | Comparison of energy (mJ) between COIN and state-of-the-art      |     |

|     | GCN accelerator [64]                                             | 97  |

| 4.7 | Comparison of EDP (mJ-ms) between COIN and state-of-the-         |     |

|     | art GCN accelerator [64]                                         | 98  |

| 5.1 | Accuracy for cache-coherency traffic flow                        | 122 |

| 5.2 | Configuration settings in the gem5 simulation                    | 123 |

| 6.1 | Summary of the notations used in this work                       | 129 |

| 6.2 | Comparisons against existing alternatives (Reference [102] and   |     |

|     | Reference [136]). <i>H</i> denotes errors over 100%              | 136 |

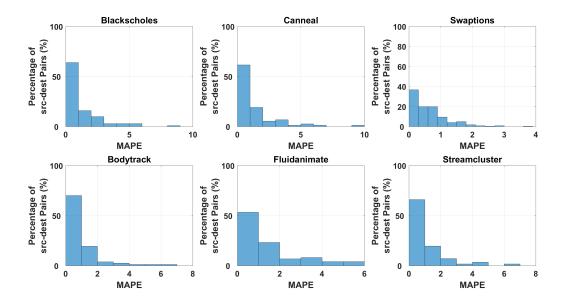

| 6.3 | Modeling Error (%) with Real Applications                        |     |

| 7.1 | Summary of the notations used in this work.                      | 145 |

| 7.2 | Validation of the proposed analytical model for $6\times6$ mesh and      |

|-----|--------------------------------------------------------------------------|

|     | 6×1 ring                                                                 |

|     | with bursty traffic arrival, and comparisons against prior work [102,    |

|     | 136]. 'E' signifies error >100%                                          |

|     |                                                                          |

| 8.1 | Comparison of prior research and our novel contribution 165              |

| 8.2 | List of the important parameters used in this work 169                   |

| 8.3 | Summary of results for synthetic applications with <b>100% hit</b> . 183 |

| 8.4 | Summary of results for synthetic applications with 100% miss. 183        |

| 8.5 | Analysis on execution time of the proposed model 186                     |

#### LIST OF FIGURES

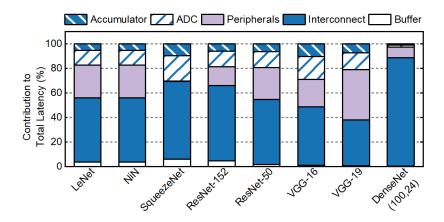

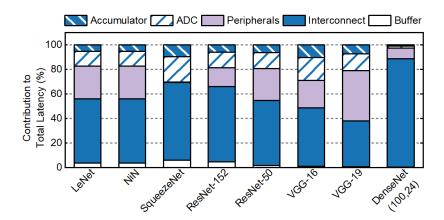

| 1.1 | Percentage contribution of different components of the IMC             |    |

|-----|------------------------------------------------------------------------|----|

|     | hardware to total latency. 40%-90% of the total latency is spent       |    |

|     | on on-chip communication when bus-based H-Tree intercon-               |    |

|     | nect is used                                                           | 2  |

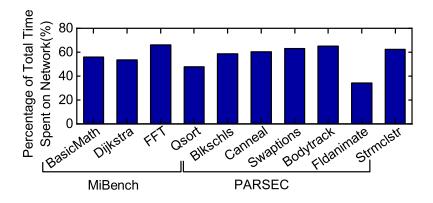

| 1.2 | Experiments of different applications show that 40%-70% of             |    |

|     | the total simulation time is spent on the network                      | 3  |

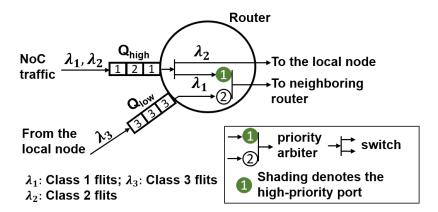

| 1.3 | The high priority queue $(Q_{high})$ stores two different traffic      |    |

|     | classes which are already in the NoC, while the low priority           |    |

|     | queue $(Q_{low})$ stores the newly injected flits from the local node. |    |

|     | As flits from class–2 are routed to the local node, low-priority       |    |

|     | flits compete with only class–1 flits in $Q_{high}$                    | 4  |

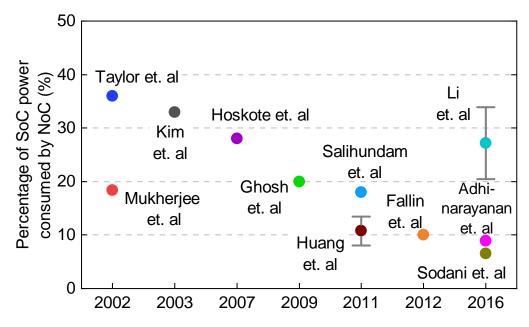

| 2.1 | Percentage of the total power consumed by NoC over the past            |    |

|     | two decades                                                            | 8  |

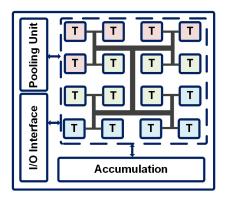

| 3.1 | Multi-tiled IMC architecture with bus-based H-Tree intercon-           |    |

|     | nect [41]                                                              | 26 |

| 3.2 | Percentage contribution of different components of the IMC             |    |

|     | hardware to total latency. 40%-90% of the total latency is spent       |    |

|     | on on-chip communication when bus-based H-Tree intercon-               |    |

|     | nect is used                                                           | 27 |

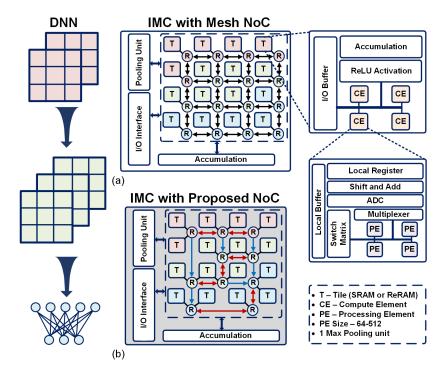

| 3.3 | IMC architecture with an arbitrary DNN mapped onto different           |    |

|     | tiles with, (a) the mesh-NoC and (b) the proposed latency-             |    |

|     | optimized NoC                                                          | 31 |

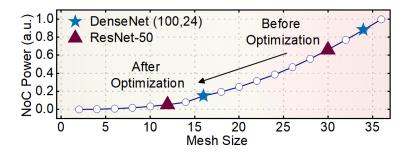

| 3.4 | NoC optimization effectively reduces the power consumption             |    |

|     | because of its non-linear dependence on the mesh size. We              |    |

|     | obtain NoC power through BookSim [90] simulations                      | 34 |

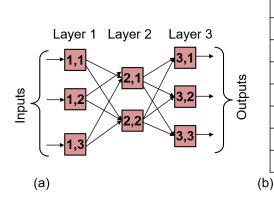

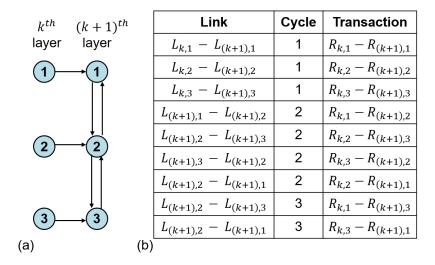

| 3.5 | (a) Communication between layers in a DNN and (b) The                                |    |

|-----|--------------------------------------------------------------------------------------|----|

|     | schedules for obtaining minimum communication latency be-                            |    |

|     | tween layers. Without loss of generality, it is assumed that the                     |    |

|     | computation time in the tile is 0 cycles                                             | 36 |

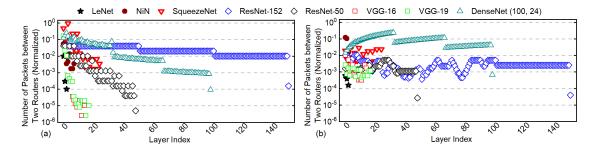

| 3.6 | The number of packets between two routers with (a) one router                        |    |

|     | per tile, and (b) the proposed technique. All the numbers are                        |    |

|     | normalized with a factor of $4 \times 10^5$ (the highest number of                   |    |

|     | packets per router between two layers with one router per                            |    |

|     | tile, which occurs between 4 <sup>th</sup> and 5 <sup>th</sup> layer of SqueezeNet). |    |

|     | The number of packets between routers decreases significantly                        |    |

|     | with the proposed approach for all DNNs except DenseNet                              |    |

|     | (100,24) and ResNet-50. However, the number of routers used                          |    |

|     | for DenseNet with our proposed technique (300) is less than                          |    |

|     | the number of routers required (1088) if one router is allocated                     |    |

|     | per tile. Our technique achieves around 72% reduction in the                         |    |

|     | NoC area. Similar improvement is seen for ResNet-50 as well.                         | 37 |

| 3.7 | (a) NoC architecture which achieves the minimum possible                             |    |

|     | latency when two consecutive layers each have three routers,                         |    |

|     | (b) Schedule to achieve the minimum possible latency                                 | 43 |

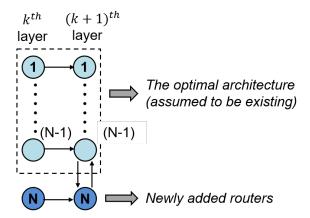

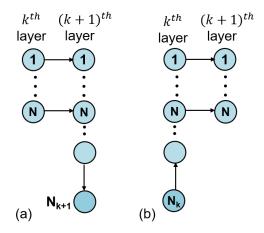

| 3.8 | NoC architecture which achieves the minimum possible latency                         |    |

|     | when two consecutive layers consist of N routers each                                | 44 |

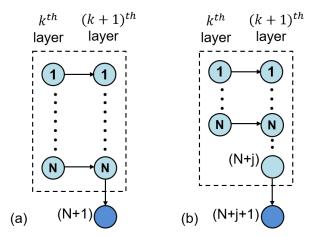

| 3.9 | NoC architecture to achieve minimum latency for Case 2. (a)                          |    |

|     | shows the case when there is one more router in $(k+1)^{\text{th}}$ layer            |    |

|     | than k <sup>th</sup> layer. (b) shows the general case. The dotted box shows         |    |

|     | the optimal architecture (already proved) and the circles filled                     |    |

|     | with dark color represent the newly added router                                     | 46 |

|     |                                                                                      |    |

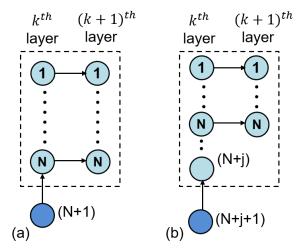

| 3.10 | NoC architecture to achieve minimum latency for Case 3. (a)                   |    |

|------|-------------------------------------------------------------------------------|----|

|      | shows the case when there is one more router in $(k+1)^{\text{th}}$ layer     |    |

|      | than k <sup>th</sup> layer, (b) shows the general case. The dotted box shows  |    |

|      | the optimal architecture (already proved) and the circles filled              |    |

|      | with dark color represent the newly added router                              | 47 |

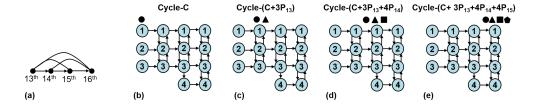

| 3.11 | Operation of the proposed NoC for a section of DenseNet                       |    |

|      | (100,24) [82]. (a) A representative section of DenseNet (100,24).             |    |

|      | (b)– $(d)$ show the communication between the layers of DenseNet              |    |

|      | (100,24)                                                                      | 47 |

| 3.12 | NoC architecture which achieves minimum possible latency                      |    |

|      | when (a) $N_k < N_{k+1}$ and (b) $N_k > N_{k+1}$                              | 48 |

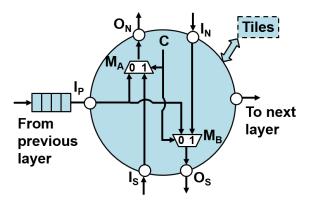

| 3.13 | Router architecture of the proposed NoC                                       | 53 |

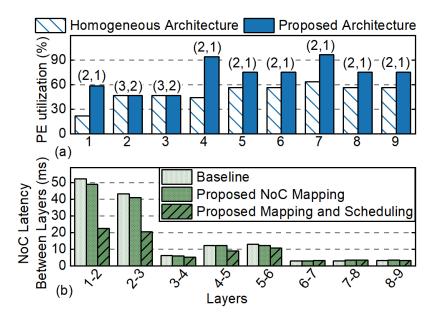

| 3.14 | Layer-wise improvement for NiN in (a) PE utilization for each                 |    |

|      | layer with SRAM-based heterogeneous tile architecture. The                    |    |

|      | tile structure for each layer $(c_k, p_k)$ is shown on top of each bar        |    |

|      | and (b) communication latency for each layer with proposed                    |    |

|      | NoC optimization                                                              | 56 |

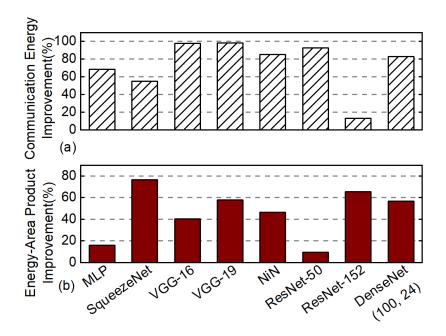

| 3.15 | Improvement in (a) communication energy of the proposed                       |    |

|      | energy-aware NoC optimization with respect to the baseline                    |    |

|      | (SRAM) and (b) energy-area product of the generated SRAM-                     |    |

|      | based architecture with respect to the baseline (SRAM)                        | 57 |

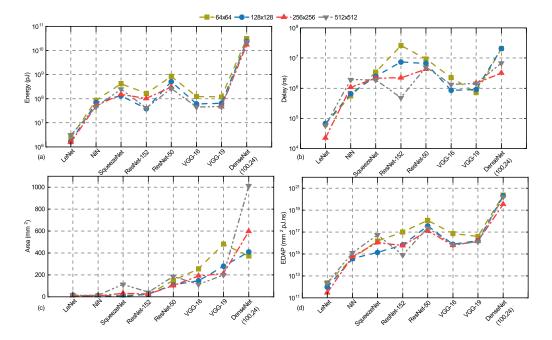

| 3.16 | Performance of the baseline SRAM-based IMC architecture for                   |    |

|      | different DNNs with different crossbar size. We observe that                  |    |

|      | a crossbar size of $128 \times 128$ or $256 \times 256$ performs better (with |    |

|      | mesh-NoC) than other crossbar sizes. $\ \ldots \ \ldots \ \ldots \ \ldots$    | 58 |

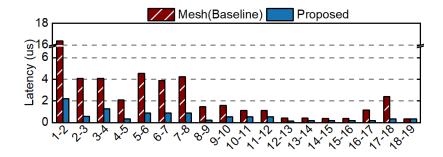

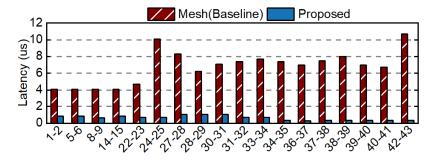

| 3.17 | Improvement in communication latency for each layer of VGG-19. $ \\$          | 59 |

| 3.18 | Improvement in communication latency for each layer of ResNet-                |    |

|      | 50                                                                            | 59 |

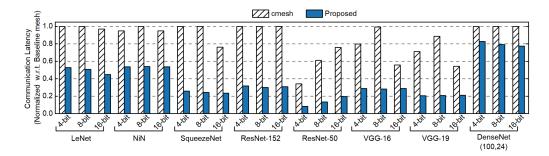

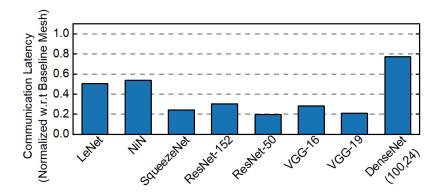

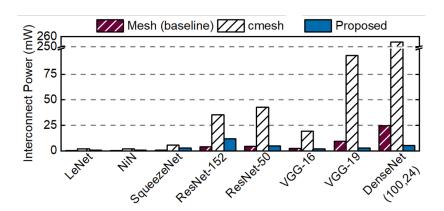

| 3.19 | Improvement in communication latency for different DNNs          |    |

|------|------------------------------------------------------------------|----|

|      | (with crossbar size of 256×256) and weights and activation       |    |

|      | precision with respect to mesh-NoC for cmesh [183] and the       |    |

|      | proposed approach                                                | 60 |

| 3.20 | Improvement in communication latency with proposed NoC           |    |

|      | with respect to mesh for crossbar size of 128 $\times$ 128       | 61 |

| 3.21 | Comparison of interconnect power consumption with different      |    |

|      | techniques                                                       | 61 |

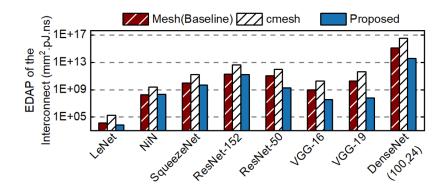

| 3.22 | Interconnect EDAP comparison for different DNNs                  | 62 |

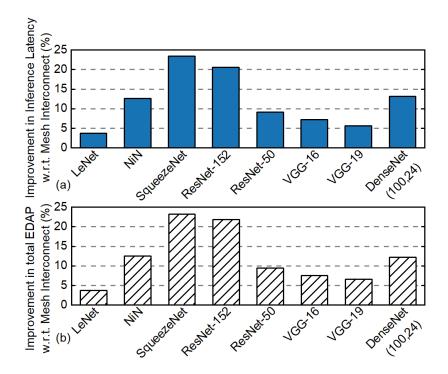

| 3.23 | Overall improvement in (a) total inference latency and (b) total |    |

|      | EDAP of a SRAM-based IMC architecture with the proposed          |    |

|      | latency-optimized interconnect with respect to the baseline      | 64 |

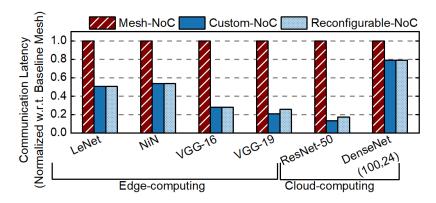

| 3.24 | Results of leave-one-out experiments with reconfigurable NoC     |    |

|      | for edge computing- and cloud computing-based DNNs               | 66 |

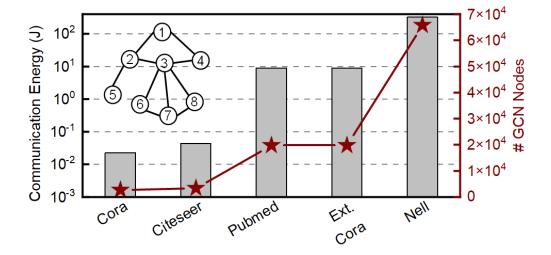

| 4.1  | Communication energy with a baseline IMC-based GCN ac-           |    |

|      | celerator. In the baseline architecture, the number of compute   |    |

|      | elements is equal to the number of GCN nodes and compute         |    |

|      | elements are interconnected by a 2D mesh NoC through a dedi-     |    |

|      | cated router. The x-axis is sorted by increasing number of GCN   |    |

|      | nodes                                                            | 70 |

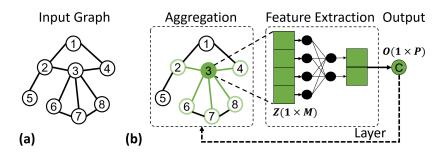

| 4.2  | (a) An example input graph, (b) Graph Convolutional Network      |    |

|      | model                                                            | 74 |

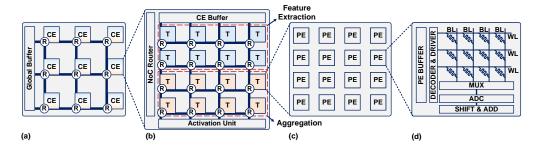

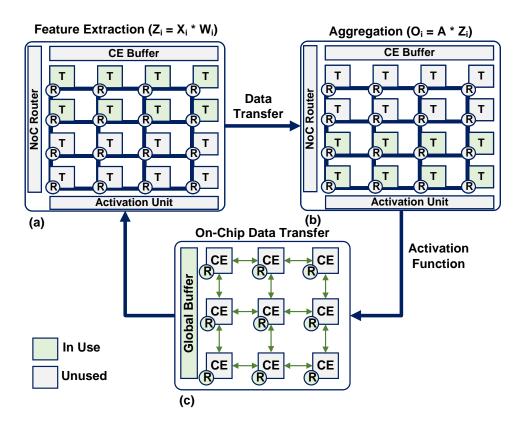

| 4.3  | Overview of the COIN architecture for GCN acceleration. Each     |    |

|      | compute element (CE) consists of an array of processing ele-     |    |

|      | ments (PEs) or RRAM-based IMC crossbar arrays connected          |    |

|      | by an NoC-mesh. A subset of the PEs performs the aggregation     |    |

|      | operation while the remaining performs the feature extraction.   |    |

|      | Aggregation PEs store the adjacency matrix while the feature     |    |

|      | extraction PEs store the layer weights                           | 75 |

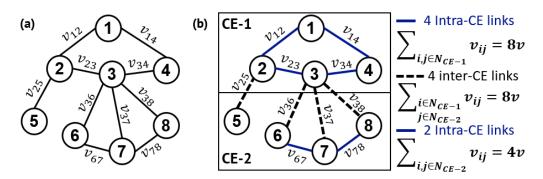

| 4.4  | A canonical graph example for intra-CE and inter-CE commu-       |    |

|------|------------------------------------------------------------------|----|

|      | nication                                                         | 76 |

| 4.5  | Layer-wise execution dataflow of the proposed COIN architec-     |    |

|      | ture. (a) shows feature extraction operation of layer-i in a CE, |    |

|      | (b) shows aggregation operation of layer-i in a CE, (c) shows    |    |

|      | the communication between CEs                                    | 81 |

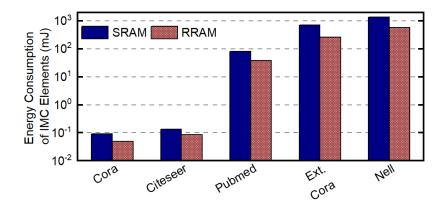

| 4.6  | Comparison of Energy Consumption (in log scale) of IMC           |    |

|      | Elements between SRAM and RRAM-based designs                     | 84 |

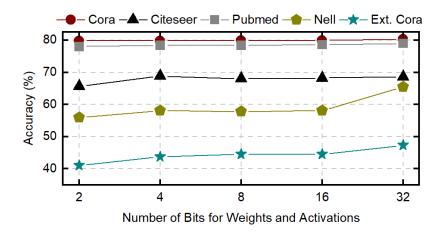

| 4.7  | Accuracy with different quantization bits for weights and acti-  |    |

|      | vations for different datasets                                   | 86 |

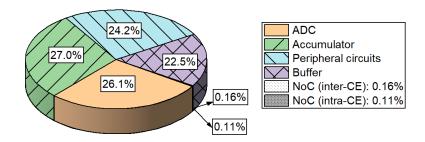

| 4.8  | Different components of COIN and corresponding area              | 87 |

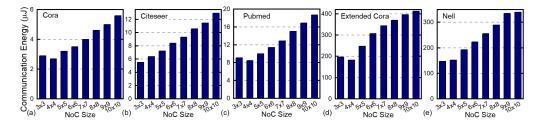

| 4.9  | Comparison of communication energy consumption with dif-         |    |

|      | ferent NoC sizes for (a) Cora, (b) Citeseer, (c) Pubmed, (d)     |    |

|      | Extended Cora and (e) Nell                                       | 87 |

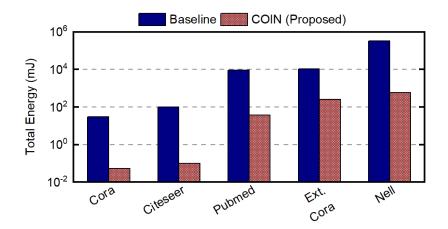

| 4.10 | Comparison of total energy (in log scale) with respect to a      |    |

|      | baseline architecture. In the baseline architecture, the number  |    |

|      | of compute elements is equal to the number of GCN nodes          |    |

|      | and compute elements are interconnected by a 2D mesh NoC         |    |

|      | through a dedicated router                                       | 89 |

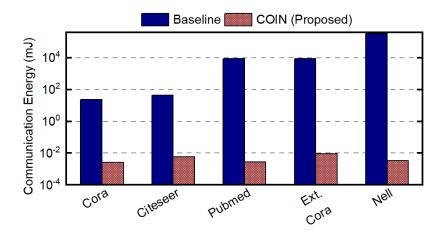

| 4.11 | Comparison of communication energy (in log scale) between        |    |

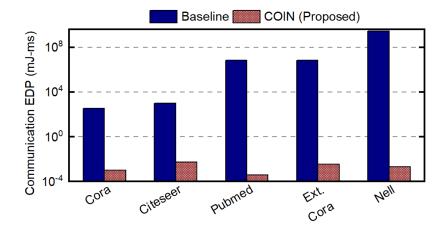

|      | baseline and proposed COIN architecture                          | 91 |

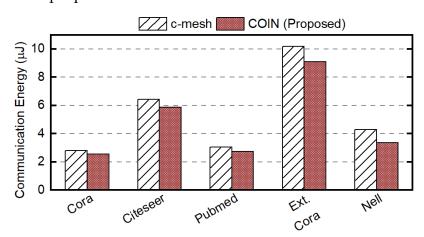

| 4.12 | Comparison of inter-CE communication energy between the          |    |

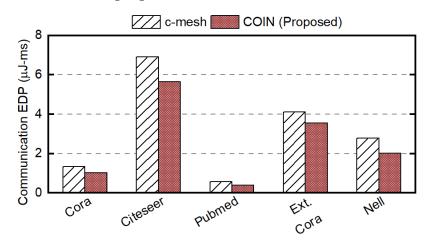

|      | proposed architecture with c-mesh NoC and proposed COIN          |    |

|      | architecture with mesh NoC                                       | 91 |

| 4.13 | Comparison of EDP (in log scale) for on-chip communication       |    |

|      | between baseline and proposed COIN architecture                  | 92 |

| 4.14 | Comparison of EDP for inter-CE communication across base-        |    |

|      | line, proposed architecture with c-mesh NoC, and proposed        |    |

|      | COIN architecture. COIN achieves least EDP across all datasets.  | 92 |

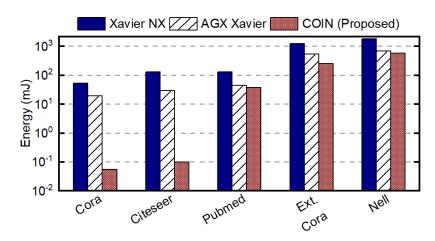

| 4.15 | Comparison of energy (in log scale) between COIN and edge                   |     |

|------|-----------------------------------------------------------------------------|-----|

|      | devices. COIN consumes less energy than both Nvidia Jetson                  |     |

|      | edge devices                                                                | 93  |

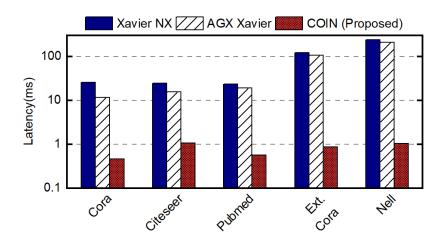

| 4.16 | Comparison of latency (in log scale) between COIN and edge                  |     |

|      | devices. COIN incurs less latency than both Nvidia Jetson edge              |     |

|      | devices                                                                     | 94  |

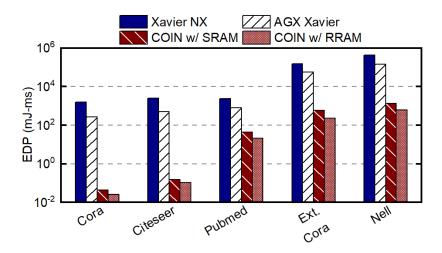

| 4.17 | Comparison of EDP (in log scale) between COIN and edge                      |     |

|      | devices. We present the performance of COIN with both SRAM                  |     |

|      | and RRAM-based IMC elements. COIN with both kinds of                        |     |

|      | devices outperforms both Xavier NX and AGX Xavier Nvidia                    |     |

|      | Jetson devices across all datasets                                          | 95  |

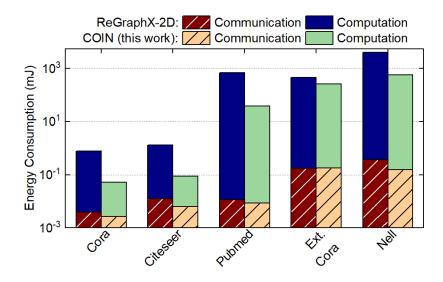

| 4.18 | Comparison of energy consumption (in log scale) between 2D                  |     |

|      | version of ReGraphX [10] and COIN. The breakdown between                    |     |

|      | communication and computation energy is shown for both the                  |     |

|      | architectures                                                               | 97  |

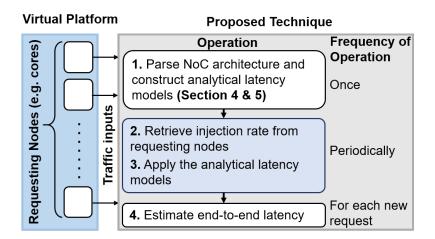

| 5.1  | Overview of the proposed methodology                                        | 102 |

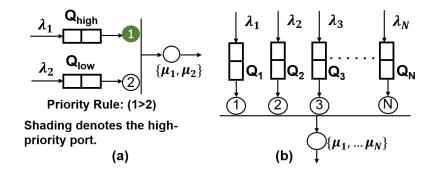

| 5.2  | (a) A system with two queues. Flits in $Q_{high}$ have higher               |     |

|      | priority than flits in Q <sub>low</sub> . (b) A system with N queues, where |     |

|      | $Q_i$ has higher priority than $Q_j$ for $i < j \ldots \ldots \ldots$       | 103 |

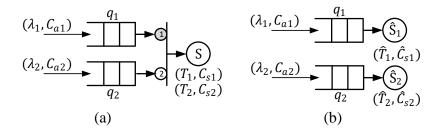

| 5.3  | Split at high priority: Structural Transformation                           | 106 |

| 5.4  | Comparison of simulation with the basic priority-based queu-                |     |

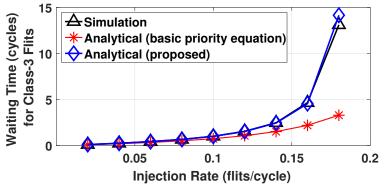

|      | ing model and proposed analytical model                                     | 107 |

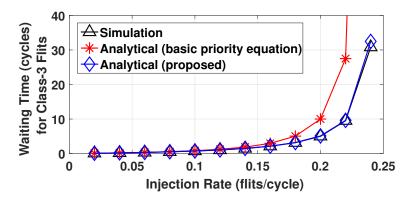

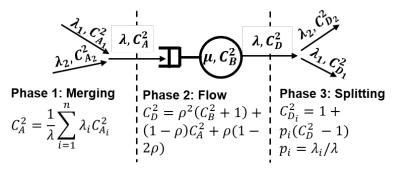

| 5.5  | Decomposition technique: In phase 1, different traffic flows                |     |

|      | merge into a single flow with an inter-arrival time $C_A$ ; in phase        |     |

|      | 2, flits flow into the queue and leave the queue with an inter-             |     |

|      | departure time $C_D$ ; in phase 3, flits split into different flows         |     |

|      | with individual inter-departure time                                        | 108 |

| 5.6  | Split at low priority: Service Rate Transformation. $\mu^*$ denotes |     |

|------|---------------------------------------------------------------------|-----|

|      | transformed service rate. The waiting time of class-1 flits de-     |     |

|      | pends on the residual time of the class-3 flits, as shown in        |     |

|      | Equation 5.5                                                        | 109 |

| 5.7  | Comparison of simulation with the basic priority-based queu-        |     |

|      | ing model and proposed analytical model                             | 110 |

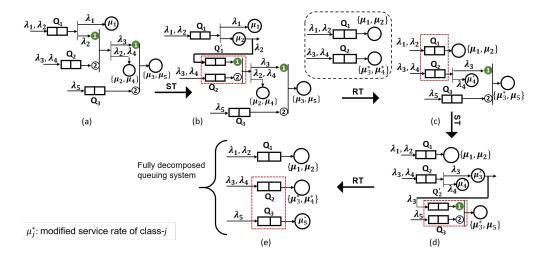

| 5.8  | Applying the proposed methodology on a representative seg-          |     |

|      | ment of a priority-based network. ST and RT denote Struc-           |     |

|      | tural and Service Rate Transformation, respectively. Red-dotted     |     |

|      | squares show the transformed part from the previous step. Fig-      |     |

|      | ure (a) shows the original queuing system. After applying ST        |     |

|      | on $Q_1$ , we obtain the system shown in Figure (b). The system     |     |

|      | in Figure (c) is obtained by applying RT on $Q_2$ . ST is applied   |     |

|      | again on $Q_2$ to obtain the system shown in Figure (d). Finally,   |     |

|      | RT is applied on $Q_3$ to obtain the fully decomposed queuing       |     |

|      | system shown in Figure (e)                                          | 114 |

| 5.9  | The fraction of simulation time spent by different functions        |     |

|      | while running Streamcluster in gem5. NoC-related functions          |     |

|      | take 60% of simulation time                                         | 117 |

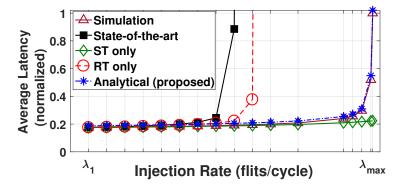

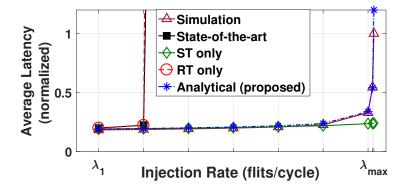

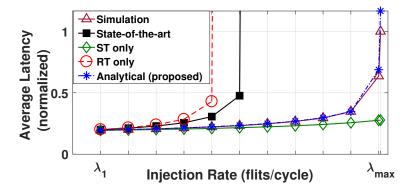

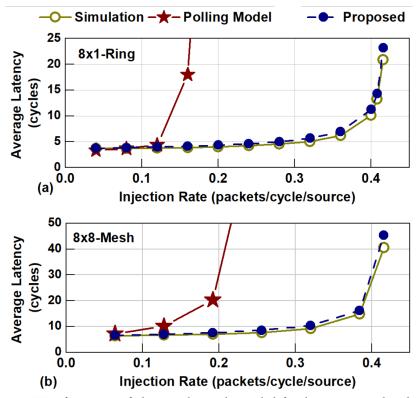

| 5.10 | Evaluation of the proposed model on a ring with eight nodes.        | 118 |

| 5.11 | Evaluation of the proposed model                                    |     |

|      | on a 6×6 mesh                                                       | 119 |

| 5.12 | Evaluation of the proposed model                                    |     |

|      | on an 8×8 mesh                                                      | 120 |

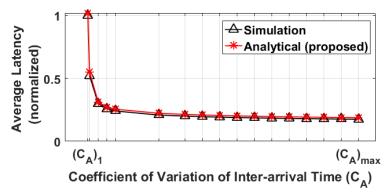

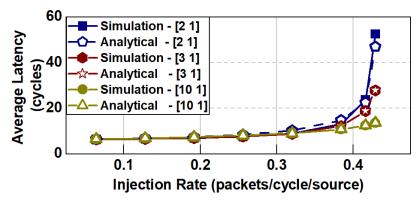

| 5.13 | Effect of coefficient of variation of inter-arrival time on average |     |

|      | latency for a $6\times6$ mesh                                       | 120 |

| 5.14 | Evaluation of the proposed model on one variant of the Xeon         |     |

|      | server architecture                                                 | 121 |

| 5.15 | Per-class latency comparison for the server example                 | 122 |

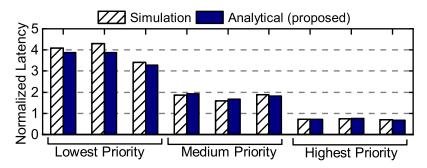

| 5.16 | Model comparison for different applications from PARSEC suite.      | 124 |

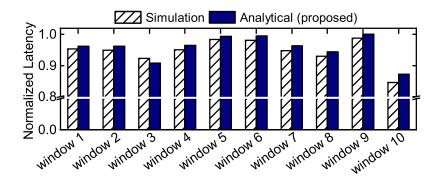

| 5.17 | Evaluation of the proposed model under a finer level of time                            |     |

|------|-----------------------------------------------------------------------------------------|-----|

|      | granularity (100K cycles) for Streamcluster application                                 | 125 |

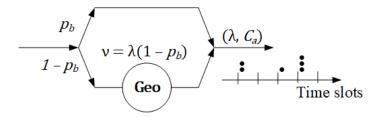

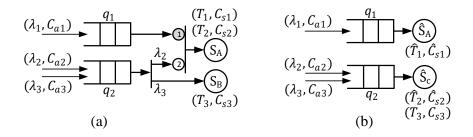

| 6.1  | GGeo traffic model                                                                      | 128 |

| 6.2  | Decomposition of a basic priority queuing                                               | 131 |

| 6.3  | Decomposition of flow contention at low priority                                        | 133 |

| 6.4  | Decomposition of flow contention at high priority                                       | 134 |

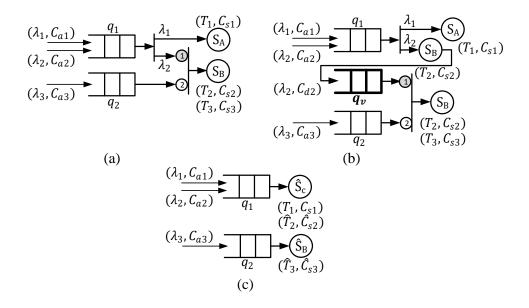

| 6.5  | Comparison of a proposed analytical model with cycle-accurate                           |     |

|      | simulation for $8\times8$ and $6\times6$ mesh for (a) $p_b=0.2$ and (b)                 |     |

|      | $p_b = 0.6$ . SOTA1 and SOTA2 refer to the analytical modeling                          |     |

|      | techniques proposed in [102] and [136] respectively                                     | 137 |

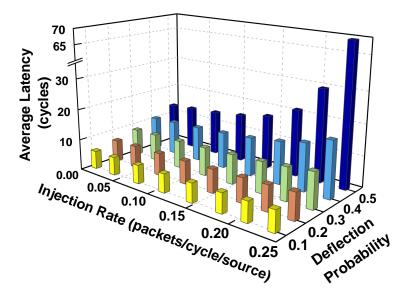

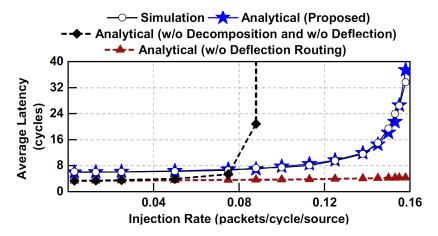

| 7.1  | Cycle-accurate simulations on a $6\times6$ NoC show that the average                    |     |

|      | latency increases significantly with larger deflection probability                      |     |

|      | $(p_d)$ at the sink. $\hdots$                                                           | 140 |

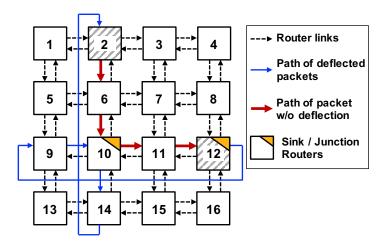

| 7.2  | A representative $4{\times}4$ mesh with deflection routing                              | 142 |

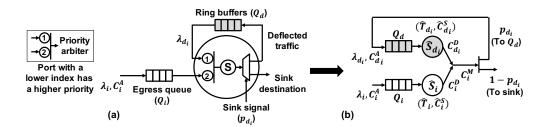

| 7.3  | (a) Queuing system of a single class with deflection routing                            |     |

|      | (b) Approximate queuing system to compute $C_{d_i}^A$                                   | 144 |

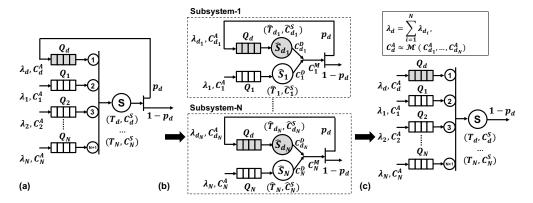

| 7.4  | (a) Queuing system with N classes with deflection routing, (b)                          |     |

|      | Decomposition into N subsystems to calculate GGeo parame-                               |     |

|      | ters of deflected traffic per class, (c) Applying superposition                         |     |

|      | to obtain the GGeo parameters of overall deflected traffic. $\ensuremath{\mathfrak{M}}$ |     |

|      | denotes the merging process                                                             | 149 |

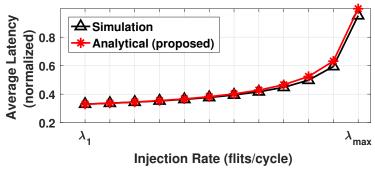

| 7.5  | Comparison of average latency between simulation and analyt-                            |     |

|      | ical model for the canonical example shown in Figure 7.4 with                           |     |

|      | $p_d = 0.3$ and $N = 5$                                                                 | 151 |

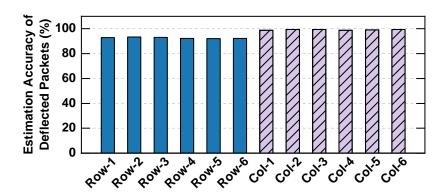

| 7.6  | Estimation accuracy of average number of packets deflected for                          |     |

|      | each row and column in a $6\times6$ mesh with $p_d=0.3.$                                | 155 |

| 7.7 | Comparison of average latency between simulation, the an-                            |

|-----|--------------------------------------------------------------------------------------|

|     | alytical model proposed in this work, and analytical models                          |

|     | proposed in [102, 136] for a $6 \times 6$ mesh with deflection proba-                |

|     | bility (a) 0.1 and (b) 0.3                                                           |

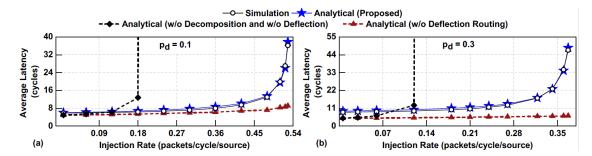

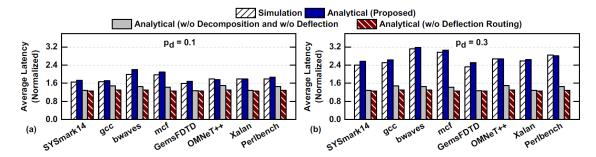

| 7.8 | Average latency comparison between simulation, the analytical                        |

|     | model proposed in this work, and analytical models proposed                          |

|     | in [102, 136] for a $6 \times 6$ mesh with (a) $p_d = 0.1$ and (b) $p_d = 0.3$ . 157 |

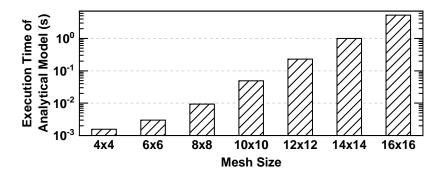

| 7.9 | Execution time of the proposed analytical model (in seconds)                         |

|     | for different mesh sizes                                                             |

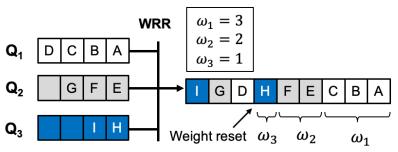

| 8.1 | Illustration of weighted round-robin arbitration. 'A' is served                      |

|     | first, 'I' last. In this example it is assumed that no new packets                   |

|     | arrived until all prior packets (A-I) have been served 166                           |

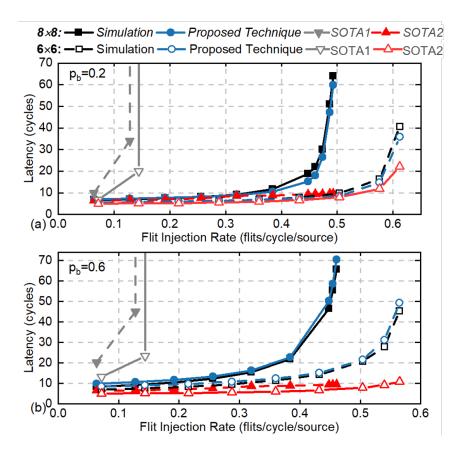

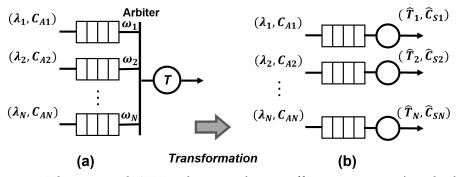

| 8.2 | The original WRR arbiter with its traffic parameters (on the                         |

|     | left) and a transformed WRR (on the right) that comprises                            |

|     | fully decomposed queue nodes using our effective service time                        |

|     | transformations                                                                      |

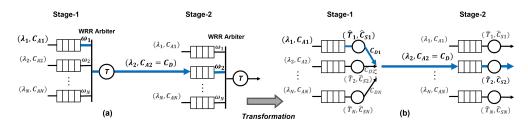

| 8.3 | Illustration of extending the proposed analysis to multiple                          |

|     | stages. Only two consecutive stages are shown for clarity. The                       |

|     | departure statistics at a given stage become the arrival statistics                  |

|     | of the subsequent stage. The blue line denotes that the class                        |

|     | which wins the arbitration goes to the next stage 176                                |

| 8.4 | Verification of the analytical model for basic round-robin with                      |

|     | (a) 8×1 and (b) 8×8 NoC                                                              |

| 8.5 | Verification of the analytical model for weighted round-robin                        |

|     | with $8 \times 8$ NoC. [x y] denotes that the WRR weights associated                 |

|     | with channels connected to the internal routers is x and traffic                     |

|     | channels of external input to the NoC is y                                           |

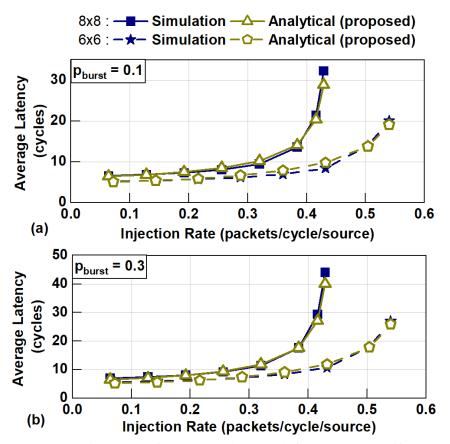

| 8.6 | Verification of analytical model for bursty traffic with (a) $p_{burst} =$           |

|     | 0.1 and $p_{burst} = 0.3$                                                            |

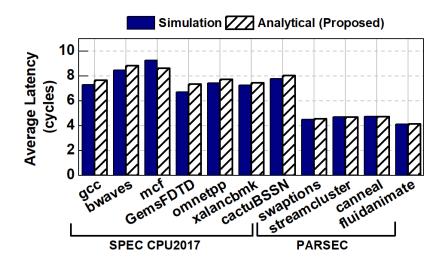

| 8.7 | Verification against real applications                                               |

Hardware accelerators for deep neural networks (DNNs) exhibit high volume of on-chip communication due to deep and dense connections. State-of-the-art interconnect methodologies for in-memory computing deploy a bus-based network or mesh-based Network-on-Chip (NoC). Our experiments show that up to 90% of the total inference latency of a DNN hardware is spent on on-chip communication when the bus-based network is used. To reduce the communication latency, we propose a methodology to generate an NoC architecture along with a scheduling technique customized for different DNNs. We prove mathematically that the generated NoC architecture and corresponding schedules achieve the minimum possible communication latency for a given DNN. Experimental evaluations on a wide range of DNNs show that the proposed NoC architecture enables 20%-80% reduction in communication latency with respect to state-of-the-art interconnect solutions.

Graph convolutional networks (GCNs) have shown remarkable learning capabilities when processing data in the form of graph which is found inherently in many application areas. To take advantage of the relations captured by the underlying graphs, GCNs distribute the outputs of neural networks embedded in each vertex over multiple iterations. Consequently, they incur a significant amount of computation and irregular communication overheads, which call for GCN-specific hardware accelerators. We propose a communication-aware in-memory computing architecture (COIN) for GCN hardware acceleration. Besides accelerating the computation using custom compute elements (CE) and in-memory computing, COIN aims at minimizing the intra- and inter-CE communication in GCN operations to optimize the performance and energy efficiency. Experimental evaluations with various datasets show up to  $174 \times$  improvement in energy-delay product with respect to Nvidia Quadro RTX 8000 and edge

GPUs for the same data precision.

Networks-on-chip (NoCs) have become the standard for interconnect solutions in DNN accelerators as well as industrial designs ranging from client CPUs to many-core chip-multiprocessors. Since NoCs play a vital role in system performance and power consumption, pre-silicon evaluation environments include cycle-accurate NoC simulators. Long simulations increase the execution time of evaluation frameworks, which are already notoriously slow, and prohibit design-space exploration. Existing analytical NoC models, which assume fair arbitration, cannot replace these simulations since industrial NoCs typically employ priority schedulers and multiple priority classes. To address this limitation, we propose a systematic approach to construct priority-aware analytical performance models using micro-architecture specifications and input traffic. Our approach decomposes the given NoC into individual queues with modified service time to enable accurate and scalable latency computations. Specifically, we introduce novel transformations along with an algorithm that iteratively applies these transformations to decompose the queuing system. Experimental evaluations using real architectures and applications show high accuracy of 97% and up to  $2.5 \times$  speedup in full-system simulation.

In recent years, deep neural networks (DNNs) and graph convolutional networks (GCNs) have shown tremendous success in recognition and detection tasks such as image processing, health monitoring, and language processing [116, 145]. Higher accuracy in DNNs is achieved by using larger and more complex models. However, such models require a large number of weights, and consequently, traditional DNN hardware accelerators require a large number of memory accesses to fetch the weights from off-chip memory, leading to a large number of off-chip memory accesses lead to higher latency and energy consumption.

In-Memory Computing (IMC) techniques reduce memory access related latency and energy consumption through the integration of computation with memory accesses. A prime example is the crossbar-based IMC architecture which provides a significant throughput boost for DNN acceleration. At the same time, crossbar-based in-memory computing dramatically increases the volume of on-chip communication, when all weights and activations are stored on-chip. Emerging DNNs with higher accuracy, such as those derived through Neural Architecture Search (NAS) [212, 224, 225], further exacerbate the problem of on-chip communication due to larger model size and more complex connections. Therefore, designing an efficient on-chip communication architecture is crucial for the in-memory acceleration of DNNs.

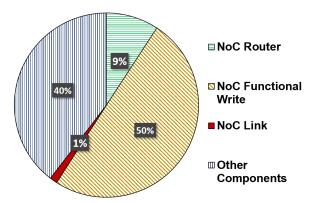

State-of-the-art IMC architectures usually deploy a bus-based H-Tree interconnect [147, 188]. Figure 3.2 shows that up to 90% of the total inference latency of a DNN hardware is spent on on-chip communication when the H-Tree interconnect is used. In order to reduce on-chip communication latency, NoC-based interconnects are employed for conventional SoCs [88] and DNN accelerators [44, 183]. Eyeriss-V2 [44] proposes to use three different NoCs for weights, activations, and partial sums. Such

Figure 1.1: Percentage contribution of different components of the IMC hardware to total latency. 40%-90% of the total latency is spent on on-chip communication when bus-based H-Tree interconnect is used.

an architectural choice allows for higher performance at the cost of both area and energy consumption. ISAAC [183] employs a concentrated-mesh (cmesh) NoC at the tile-level of the IMC accelerator.

In this work, we minimize the communication energy across a large number of tiles using an NoC architecture with optimized tile-to-router mapping and scheduling. We also propose an optimization technique to determine the optimal number of NoC routers required for each layer of the DNN. Next, we propose a methodology to generate a latency-optimized NoC architecture along with a scheduling technique customized for different DNNs. We prove, through induction, that the proposed NoC architecture achieves minimum possible communication latency using the minimum number of links between the routers. These two techniques together generate a custom NoC for IMC acceleration of a given DNN. We show that the proposed custom IMC architecture achieves 20%-80% improvement in overall communication latency and 5%-25% reduction in end-to-end inference latency with respect to state-of-the-art NoC based IMC architectures [183].

Figure 1.2: Experiments of different applications show that 40%-70% of the total simulation time is spent on the network.

Furthermore, we also proposed IMC-based communication-aware hardware accelerator for graph convolutional networks (GCNs). We perform rigorous experimental evaluation across popular graph datasets for GCN and comparison with respect to state-of-the-art GPUs and accelerator. The evaluation shows that our proposed GCN accelerator achieves up to  $105\times$  lower energy consumption with respect to state-of-the-art GCN accelerator.

Since the on-chip interconnect is a critical component of AI accelerators as well as multicore architectures, pre-silicon evaluation platforms contain cycle-accurate NoC simulators [6, 90]. NoC simulations take up a significant portion of the total simulation time, which is already limiting the scope of pre-silicon evaluation (e.g., simulating even a few seconds of applications can take days). For example, Figure 1.2 shows that 40%-70% of total simulation time is spent on the network itself when performing full-system simulation using gem5 [24]. Hence, accelerating NoC simulations without sacrificing accuracy can significantly improve both the quality and scope of pre-silicon evaluations.

Several performance analysis approaches have been proposed to enable faster NoC design space exploration [158, 210, 174]. Prior techniques

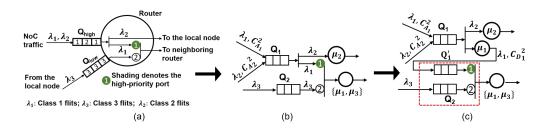

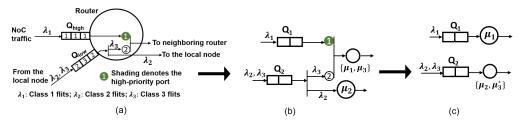

have assumed a round-robin arbitration policy in the routers since the majority of router architectures proposed to date have used round-robin for fairness. In doing so, they miss two critical aspects of the industrial priority-based NoCs [88, 178, 97]. First, routers give priority to the flits in the network to achieve predictable latency within the interconnect. flits to the local node in Figure 1.3 are already in the NoC, while flits from class-3 to the neighboring router must wait in the input buffer to be admitted. Consequently, flits in the NoC (class-1 and class-2) experience deterministic service time at the expense of increased waiting time for new flits. Second, flits from different priority classes can be stored in the same queue. For instance, new read/write requests from the core to tag directories use the same physical and virtual channels as the requests forwarded from the directories to the memory controllers. Moreover, only a fraction of the flits in either the high or low priority queue can compete with the flits in the other queue. For example, suppose the class-2 flits in

Figure 1.3: The high priority queue  $(Q_{high})$  stores two different traffic classes which are already in the NoC, while the low priority queue  $(Q_{low})$  stores the newly injected flits from the local node. As flits from class–2 are routed to the local node, low-priority flits compete with only class–1 flits in  $Q_{high}$ .

Figure 1.3 are delivered to the local node. Then, class-3 flits must compete with only class-1 flits in the high-priority queue. Analytical models that ignore this traffic split significantly overestimate the latency, as shown in Section 5.2. In contrast, analytical models that ignore priority would significantly underestimate the latency. Thus, prior approaches that do not model priority [158, 210, 174] and simple performance models for the priority queues [102, 91] are *inapplicable to priority-based industrial NoCs*.

We propose NoC performance analysis technique that considers traffic classes with different priorities. This problem is theoretically challenging due to the non-trivial interactions between classes and shared resources. For example, queues can be shared by flits with different priorities, as shown in Figure 1.3. Similarly, routers may merge different classes coming through separate ports, or act as switches that can disjoin flits coming from different physical channels. To address these challenges, we propose a two-step approach that consists of an analysis technique followed by an iterative algorithm. The first step establishes that priority-based NoCs can be decomposed into separate queues using traffic splits of two types. Since existing performance analysis techniques cannot model these structures with traffic splits, we develop analytical models for these canonical queuing structures. The second step involves a novel iterative algorithm that composes an end-to-end latency model for the queuing network of a given NoC topology and input traffic pattern. The proposed approach is evaluated thoroughly using both 2D mesh and ring architectures used in industrial NoCs. It achieves 97% accuracy with respect to cycle-accurate simulations for realistic architectures and applications.

In summary, this dissertation makes the following contributions:

- A comprehensive literature survey on energy-efficient communication architectures for general purpose processor as well as AI accelerator [137],

- Communication-aware hardware accelerator for DNN [111, 141],

- Fast and accurate performance analysis for NoCs with priority arbitration [136, 135, 139],

- Fast and accurate performance analysis technique for NoCs with weighted round robin arbitration [144].

The rest of the thesis is organized as follows. The thesis consists of communication-aware hardware accelerator for DNNs (Chapter 3) and GCNs (Chapter 4). It also spans performance analysis techniques for priority-aware NoCs (Chapter 5 – Chapter 7) as well as NoCs with weighted round robin arbitration under bursty traffic and deflection routing (Chapter 8). Finally, Chapter 9 concludes the thesis.

# 2.1 Energy-efficient Communication Architectures for General Purpose Processors

Diminishing instruction-level parallelism (ILP) and power wall led to the introduction of multicore NoC architectures more than a decade ago and fueled their growth to date [48, 87]. In turn, the growing number of cores has continuously increased the importance of efficient data movement between cores and memory. One can view the communication cost as a "necessary overhead" incurred to move data both within a chip or across multiple chips. Thus, we can evaluate the efficiency of communication architectures as a function of their performance, measured in terms of latency and throughput, versus their cost, measured by their contribution to power and energy consumption. Besides facilitating the design process through reuse and regularity, networks-on-chip architectures have proven their effectiveness with respect to this efficiency metric and become the mainstream communication fabric choice for multicore architectures [187, 168].

The transition from single core to multicore architectures played a pivotal role in satisfying the continuous demand for higher processing power. However, homogeneous multicore architectures have also reached their limits to exploit thread- and data-level parallelism. General-purpose cores facilitate programmability, but their flexibility comes at the expense of energy efficiency, which is orders of magnitude lower than special-purpose processors, such as video processors and hardware accelerators. Therefore, the heterogeneity of cores increases together with their number to drive the processing power and energy efficiency necessitating several

Figure 2.1: Percentage of the total power consumed by NoC over the past two decades.

power management techniques [55, 21, 73, 138, 109, 137, 143, 22]. In turn, the growing heterogeneity continues to increase the requirements on the communication architectures. On the one hand, communication latency should be in the same order as, or ideally lower than, the processing times of special-purpose processors, which could be in the order of nanoseconds. On the other hand, the power consumption overhead should scale down to match those of the special-purpose processors. Otherwise, the communication cost can undermine the benefits of heterogeneous architectures. Hence, the NoCs continue to play a pivotal role in developing processing systems with higher performance and energy efficiency.

NoC architectures are designed to meet the performance requirements, such as latency, throughput, and quality-of-service (QoS), while minimizing their area, power, and energy overhead. NoCs achieve a higher energy-efficiency than bus and point-to-point communication architec-

tures [121]. The exact contribution of the NoC architecture to the total power consumption is a function of many design parameters, such as the number and types of processing cores, communication bandwidth, and technology. While there is no public data for commercial designs, published academic work shows that NoC power consumption amounts to 18%–36% of the total chip power, as shown in Figure 2.1. Ghosh et. al [67], Huang et. al [83] and Li et. al [125] report absolute values, while Taylor et. al [194], Kim et. al [103], Mukherjee et. al [153], Hoskote et. al [79], Salihundam et. al [181], Fallin et. al [60], Sodani et. al [187] and Adhinaryanan et. al [5] report the percentage power consumption, which can be useful references for future work. While many other surveys discuss the energy-efficient design of and entire SoC [197, 166], in this chapter we discuss numerous prior work on NoC design.

#### **NoC Router Design**

Router design has a crucial impact on power consumption and performance since they are the fundamental building blocks of NoCs. On the one hand, fast and simple router architectures are preferred to achieve low latency (in terms of clock cycles) and small area overhead. On the other hand, deeper pipelines and more buffering space are needed for higher clock frequencies and throughput [49, 57]. Similarly, simpler crossbar and arbitration, such as round-robin, reduce the area-power overhead, but they can also severely limit the performance. As a result, the optimal router design must provide an intricate balance between power, performance, energy, and area.

Many techniques have been proposed to improve the router energy-efficiency since the introduction of NoCs [4, 148]. For example, Wang et al. explore the bottlenecks that contribute to power dissipation in interconnection networks [203]. The analysis prompts the authors to devise power-efficient microarchitecture techniques such as a cut-through cross-

bar, a segmented crossbar, and a write-through buffer. These techniques achieve an NoC power reduction of up to 44.9% and 37.9% with no performance overheads for both synthetic and real application traces, respectively. One of the early key design insights is exploiting application- or domain-specific information to customize the router architecture [81]. Hu et al. use this idea to allocate a given amount of buffer area non-uniformly across the NoC to maximize the performance [81]. Similarly, router architecture with shared buffers can improve both the area utilization and throughput in [177]. Decreasing the router pipeline delay has been an important design consideration. The basic idea is to bypass certain router pipeline stages or the whole router whenever possible, i.e., when there is no contention and packets already waiting in the queue [162, 108]. Towards achieving a single-cycle router latency, Kumar et al. [117] present a nonspeculative single-cycle NoC router pipeline targeting 3.6 GHz frequency. A customized mesh NoC that exploits application-specific behavior to introduce single-cycle links between a source and destination is introduced in [39]. These clockless repeater links traverse upto 8mm in a single cycle at a clock frequency of 2 GHz in a 45nm process node. The applicationspecific link configuration introduces complexities in reconfiguring the routers when applications are frequently preempted during execution by the system scheduler. A 2-dimensional mesh NoC coprocessor is designed for data movement in an Epiphany 64-core superscalar processor architecture [200]. Each router uses three communication channels for read requests, on-chip writes, and off-chip write transactions to improve the NoC throughput. Recently, Arm has introduced a scalable low-latency, one cycle per-hop, high-bandwidth network-on-chip architecture that supports coherency [168]. The NoC can scale from  $1\times 2$  mesh to  $8\times 8$  mesh to support edge devices and high-performance computing systems.

#### NoC Architecture and Packet Routing

The interconnection of the routers defines the NoC architecture. Most of the early work and industrial solutions employ a 2D mesh topology due to its regularity [151, 168, 187]. A regular layout simplifies the floorplan and wiring, while providing predictable delays between the routers. Consequently, regular NoC topologies facilitate energy-efficient design as well as simplified testing and validation [87, 148]. However, both the average and worst-case latency scale poorly with the network size. Since the NoC plays a crucial role in determining the latency, energy and power, numerous studies evaluate other topologies with smaller diameter, such as hypercube, folded-torus, and fat tree [4, 57]. For example, an extensive power-performance evaluation of mesh and torus topologies on power and performance is presented in [151]. NoC topology can be optimized for a given application domain by either synthesizing a custom topology [161, 170] or altering a regular topology, such as a 2D mesh [162]. Kilo-NoC, a heterogeneous NoC architecture in which only a select number of routers support QoS requirements is presented in [72]. The heterogeneity in router architecture enables 45% and 29% savings in area and power when compared to a homogeneous NoC that supports QoS in all routers.

Switching, or flow control, techniques determine how the packets are transmitted from their sources to destinations [49, 57, 87]. Due to the large buffer requirements of the packet and virtual cut-through switching techniques, wormhole routing has been a popular choice for NoCs [148]. Virtual-channels have commonly been added to address head-of-line blocking and handling multiple traffic classes while avoiding deadlocks. Circuit switching have also been employed to take advantage of high-volume data transfer over persistent connections [130]. While the early work focused on buffered NoCs, bufferless solutions are later employed to minimize the buffer requirements, hence the NoC area and static power [52, 150]. Bufferless NoCs do not store the packets in the intermediate routers. Routers try

to forward the packets towards their destinations and then deflect them if their preferred direction is not available [87]. Studies show that bufferless NoC can perform better at low traffic loads, but they suffer from traffic congestion as the traffic load increases [150]. The advantages of buffered and bufferless techniques are combined in [60] to achieve as much as 16% higher energy-efficiency than the state-of-the-art buffered routers. Intel Xeon-Phi processors [187] use priority-aware bufferless NoCs, which can provide predictable latency within the network [135]. The NoC uses fewer buffers, which in turn helps to reduce energy consumption.

Routing strategies play a crucial role in determining the area, performance, power and energy of an NoC [49, 57]. For a given NoC topology and switching technique, routing algorithms determine the path taken by each packet while traveling to their destination. The choice of the routing algorithm is important since the length of the path and traffic congestion have a significant impact on both power and performance, while their complexity impacts the area [148]. Specifically, routing techniques influence: (1) end-to-end latency, (2) selection of routing paths, (3) livelock and deadlock avoidance, (4) fault-tolerance and (5) starvation avoidance. Routing techniques are broadly classified into deterministic and adaptive routing techniques. Deterministic algorithms require fewer resources and are simpler than their adaptive counterpart. Therefore, dimension-ordered routing, such as XY routing, and other deterministic algorithms are used more commonly in industrial and academic designs [17, 187]. At the same time, run-time adaptation to the workload can provide significant benefits [80]. Since the traditional routing techniques are covered in detail in the literature, we refer the reader to existing surveys and books on this topic for a complete taxonomy and review [4, 49, 57, 163, 89].

#### **3D NoC Architectures**

As the number of transistors on a single chip increases, three-dimensional integrated circuits (3D ICs) provide more floorplanning flexibility than traditional planar designs [62]. 3D ICs also provide more packaging density since they are not limited to two dimensions [51]. Moreover, 3D ICs can reduce power consumption since they use shorter wire lengths than planar ICs [176]. Since they have emerged as a new technology paradigm due to these advantages, 3D NoCs are employed to interconnect the cores in 3D IC.

Feero et al. [62] present a detailed performance evaluation of 3D NoCs and compare them to traditional 2D NoCs. This work considers 3D mesh, 3D stacked mesh, ciliated 3D mesh, 3D butterfly tree (BFT), and 3D fat-tree topologies. The experimental evaluations show that 3D mesh, ciliated 3D mesh, and stacked mesh consume 42%, 47%, 33% less energy per packet than 2D mesh, respectively, Authors also show that both 3D fat-tree and 3D BFT consume 49% less energy per packet than their 2D counterpart. Similar to the dimension ordered routing techniques in 2D NoCs, an X– Y–Z static routing can be applied to 3D NoC. For example, Ahmed et al. [7] present a 3D NoC (OASIS-NoC) with wormhole switching and 3-stage router pipeline: routing calculation, switch allocation, and switch traversal. Evaluations using synthetic traffic show that a  $2\times2\times4$  3D OASIS-NoC reduces 22% delay on average compared to a  $4\times4$  2D OASIS-NOC. Since a fixed design may not be suitable for different applications, authors in [154] propose a synthesis approach to construct a power-efficient 3D NoC for a given application. Experiments on real applications show that the NoC topologies synthesized by the proposed methodology reduce power by 38% on average. Similarly, a floorplan-aware application-specific 3D NoC synthesis algorithm is proposed in [223]. The authors construct an irregular 3D NoC architecture that meets specific objectives for a given application in this work. The proposed algorithm's input is a directed

graph, where each node represents a core, and the edges represent the traffic flow between the cores. A multi-commodity flow (MCF) problem is formulated to optimize multiple objectives. The objectives include network power, average network latency and number of through silicon vias (TSV). Authors incorporate simulated allocation (SAL) to solve the MCF problem. The proposed methodology enables 22% power saving with respect to [154] for a set of synthetic benchmarks [214]. A summary of different 3D NoC technologies, their advantages, and drawbacks can be found in [176].

Several research teams have recently applied machine-learning techniques to design 3D NoCs [50, 95, 156]. For example, Das et al. [50] present a monolithic 3D-enabled energy-efficient NoC. Smaller dimensions of monolithic inter-tier vias provide the scope of high-density integration with reduced wire length compared to TSVs. Experimental evaluations show that the proposed methodology enables 32% lower energy-delay-product (EDP) than mesh-based interconnect and 28% lower EDP than TSV-based interconnect. TSV-based 3D NoCs are prone to failure. Therefore, a Near Field Inductive Coupling (NFIC)-based 3D NoC is proposed in [69]. In this work, convex optimization is used to co-optimize latency, power and area of the 3D NoC. Experimental evaluation on real benchmarks shows that the proposed NFIC-based 3D NoC is 34.5% more energy-efficient than TSV-based 3D NoC.

Joardar et al. [95] propose a 3D-NoC for heterogeneous many-core systems. The authors employ a machine learning-based multi-objective optimization (MOO) to construct 3D-NoC, which jointly optimizes latency, throughput, temperature, and energy. The proposed algorithm determines the optimal placement of the CPUs, GPUs, LLCs, and planar links. The authors show that the proposed technique enables 9.6% better EDP than a thermally-optimized 3D NoC design.

## 2.2 Communication-centric AI Accelerator Design

In-memory computing technique has a great potential to deliver energy-efficient AI accelerators. Most of the AI applications consist of layer-by-layer operation, i.e., the output to the k<sup>th</sup> layer is the input of the (k+1)<sup>th</sup> layer. In IMC-based accelerators, the data movement (i.e., communication) between the DNN layers are enabled by on-chip interconnects. Since the number of parameters of the neural networks has grown over past ten years as shown in [140], the on-chip communication volume also increases. Increasing communication volume, in turn, increases energy consumption due to communication which can mask the energy benefit of IMC technology itself. Therefore, an energy-efficient communication strategy is required for AI accelerator to compliment the energy benefits of IMC technology. Indeed, a single technique may not be suitable for all kinds of AI algorithms as discussed in [112].

There exist several NoC architectures for DNN accelerators. A recent study aims to maximize local data reuse and reduce data access from DRAM [43]. To this end, a row-stationary data flow is proposed, where filter weights and input feature maps (ifmap) are reused to minimize movement of ifmaps and filter weights. The architecture has later been extended to incorporate compact and sparse neural networkss in [44]. In the extended version [44], a hierarchical mesh NoC is incorporated in the architecture. It consists of 16 PE clusters and 16 global buffer clusters distributed in an  $8\times2$  array. Each PE cluster consists of 12 PEs arranged in a  $3\times4$  array. However, both architectures consider a system with off-chip memory where frequent data transfer from off-chip to on-chip is required. Therefore, the NoC optimizations incorporated in these architectures are not applicable for IMC-based accelerators. ISAAC is the one of the first IMC-based DNN accelerators proposed in the literature [183]. It uses

an NoC with concentrated mesh (c-mesh) topology. However, only one NoC router is connected to each IMC tile and no special interconnect optimization is considered in this architecture. Since larger DNNs (e.g., DenseNet with 100 layers) may contain 100s of IMC tiles, this architecture may require 100s of NoC routers, which may not be practical at all.

The growing number of NoC routers increase area as well as on-chip interconnect power consumption. To that end, we propose an optimization technique to determine number of NoC routers for a given DNN [111]. We first construct an objective function for communication energy, which considers the number of activations between two consecutive layers for each layer as input. Then the objective function is minimized to obtain the number of routers needed for all layers of the DNN. A scheduling technique is also proposed in this work to minimize the congestion in the on-chip network. The optimized number of routers along with the scheduling technique provides up to 78% improvement in energy-delay product with respect to another DNN accelerator [183]. Although this work minimizes congestion in the on-chip network with a scheduling technique, it does not guarantee minimum latency for a given DNN. We also propose an NoC architecture which guarantees minimum possible communication latency for a given DNN [141]. However, the proposed NoC architecture is customized for a single DNN. Therefore, a reconfigurable NoC is also proposed in [111], where a certain number of routers (determined with handful DNNs known at the design time) are allocated for each DNN layer. At runtime, if a new (not considered in the design time) DNN appears, then first the number of routers required for each DNN layer is computed first. If the number of routers required for a particular layer is more than the number of available routers on-chip, then the DNN layer will occupy the maximum number of routers available for that layer. The reconfigruable NoC shows 60%–80% improvement in communication latency over state-of-the-art 2D-mesh NoC.

The area of monolithic hardware accelerators increases with increasing number of parameters of AI algorithms. Higher silicon area of a single monolithic system reduces the yield, which in turn increases fabrication cost [114]. Chiplet-based system solves the issue of higher fabrication cost by integrating multiple small chips (known as chiplets) on a single die. Since the area of each chiplet in the system is considerably lower than a monolithic chip (for the same AI algorithm), the yield of the chiplet-based system increases which reduces the fabrication cost. The communication between chiplets are performed through network-on-package (NoP). There are several works in the literature which propose NoP for chiplet-based system considering different performance objectives (e.g., latency, energy) [20, 201, 184, 114].

Kite is a family of NoP proposed in [20] which is mainly targeted for general purpose processors. In this work, three topologies are proposed – Kite-Small, Kite-Medium and Kite-Large. First, an objective function is constructed with combination of the average delay between source and destination, diameter and bisection bandwidth of the NoP. Experimental evaluations on synthetic traffic show that the proposed Kite topologies reduce latency by 7% and improve the peak throughput by 17% with respect to other well-known interconnect topologies. A chiplet-based system with 96-core processor, INTACT, is proposed in [201]. The chiplets are connected through a generic chiplet-interposer interfaces (called as 3D-plugs in the paper). 3D-plugs consist of micro-bump arrays. However, both Kite and INTACT are not specific to AI workloads.

Shao et al. designed and fabricated a 36-chiplet system called SIMBA for deep learning inference [184]. The chiplets in the system are connected through a mesh NoP. Ground-referenced signalling (GRS) is used for intra-package communication. The NoP follows a hybrid wormhole/cut-through flow control. The NoP bandwidth is 100 GBps/chiplet and the latency for one hop is 20 ns. Extensive evaluation on the fabricated chip

shows up tp 16% speed up compared to baseline layer mapping for ResNet-50. A simulator for chiplet-based system, SIAM, is proposed in [114], targeting AI workloads. In this simulator, a mesh topology is considered for NoP. It is shown that up to 85% of the total system area is contributed by NoP. In this work, multiple studies were performed by varying NoP parameters. For example, it is shown that increasing NoP channel width increases energy-delay product of the NoP for ResNet-110. This phenomenon is demonstrated for systems with 25 and 36 chiplets. However, none of the prior works considered any workload-aware optimization for the NoP. Therefore, there is ample opportunity of future research which considers NoP optimization for AI accelerators.

With increasing complexity of AI algorithms, the computing resource needed to execute the algorithms also increases. Therefore, complex AI algorithms require a large number of processing elements on-chip. For example, DenseNet-110 with 28.1M parameters requires 2,184 ReRAM tiles on a single system [114]. Increasing the number of on-chip tiles results in long-range inter-tile communication. Too many long-range communications hurt energy-efficiency of the system. Therefore, monolithic 3D (M3D)-based AI accelerators have emerged to facilitate energy-efficient communication between multiple processing elements. In M3D-based accelerators, multiple processing elements are placed in each plane. The processors across different planes are connected using through silicon vias (TSV).

REGENT is such an approach which integrates ReRAM-based IMC tiles as well as GPU cores on a M3D IC [96]. The processors in the IC are connected through a 3D-NoC. REGENT is optimized to perform energy-efficient CNN training. Specifically, a bin-package based framework is adopted to map CNN layers on processing cores as well as physically place the cores in such a way that the overall system meets certain performance objectives. However, REGENT does not consider hardware implementa-

tion of normalization layers. To address this drawback, authors in [94] propose a 3D-NoC enabled IMC-based system considering normalization layers. Apart from considering hardware implementation of normalization layers, a performance-thermal aware mapping of CNN layers is also proposed in this work. The mapping helps to reduce thermal noise which can degrades the quality of CNN training. As a result, the proposed architecture is able to perform CNN training which achieves accuracy similar to GPU. The accelerator proposed in the aforementioned work is further extended in [93] by considering fewer normalization layers for CNNs. In this work, the authors show that considering few normalization layers actually improves CNN classification accuracy, since normalization helps to reduce bias occurring from a weight with high absolute value. Then Bayesian optimization is utilized to construct a M3D system. The communication between multiple processing elements is facilitated by a mesh-NoC with XYZ routing. The accelerator proposed in this work reduces the latency by 15× compared to conventional GPU-based system. However, all these work only consider CNN training on IMC-based M3D system.

Recently, several other work proposed IMC-based M3D systems which are capable of training graph analytics [37] and graph neural networks (GNN) [142, 10, 12, 11]. ReGraphX is a 3D-NoC enabled heterogeneous IMC-based system which performs energy-efficient GNN training [10]. In this system, there are two types of processing elements: V-PEs, which perform vertex computations and E-PEs, which perform edge computation pertaining to a GNN. V-PEs consist of 128×128 crossbar arrays whereas E-PEs consist of 8×8 crossbar arrays. Experimental evaluations show that ReGraphX reduces energy consumption by 11× with respect to conventional GPUs. Authors in [12] show performance and accuracy trade-offs in 3D-NoC enabled IMC-based GNN accelerator. In this work, a stochastic rounding technique is proposed to reduce the precision of

ReRAM crossbar arrays. The reduced precision helps to improve energy-efficiency of the accelerator. A DropLayer-aware M3D-based manycore ReRAM architecture for training GNNs, DARe, is proposed in [11]. The droplayer-based technique reduces on-chip communication volume in the system, which in turn, prevents communication hotspot. Reduced communication hotspot improves the energy-efficiency of the overall system. The proposed architecture demonstrates  $1.9\times$  reduction in execution time with respect to ReGraphX [10]. Thus M3D-based systems with 3D NoC provide energy-efficient platform for CNN as well GNN training. Apart from DNN and graph applications, IMC-based accelerators are also proposed for recurrent neural networks (RNN) inference [36, 35], sorting application [127], video summarization [34].

# 2.3 Analytical Performance Modeling of Networks-on-Chip

Performance analysis techniques are useful for exploring design space [165] and speeding up simulations [158, 102, 210]. Indeed, there is continuous interest in applying novel techniques such as machine learning [174] and network calculus [173] to NoC performance analysis. However, these studies do not consider multiple traffic classes with different priorities. Since state-of-the-art industrial NoC designs [56, 88] use *priority-based arbitration* with multi-class traffic, it is important to develop performance analysis for this type of architectures.

Kashif et al. have recently presented priority-aware router architectures [99]. However, this work presents analytical models only for worst-case latency. In practice, analyzing the average latency is important since using worst-case latency estimation in full-system would lead to inaccurate conclusions. A recent technique proposed an analytical latency model for priority-based NoC [102]. This technique, however, assumes that each

queue in the network contains a single class of flits. This assumption is not practical since most of the industrial NoCs share queues between multiple traffic classes. Analytical model for industrial NoCs, which estimates average end-to-end latency is proposed in [136]. However, these models assume that the input traffic follows geometric distribution, which is not applicable for workloads with bursty traffic.

Deflection routing was first introduced in the domain of optical NoC as hot-potato routing [29]. Later, it was adapted for the NoCs used in high-performance SoCs to minimize buffer requirements and increase energy efficiency [152, 59, 60]. This routing mechanism always assigns the packets to a free output port of a router, even if the assignment does not result in minimum latency. This way, the buffer size requirement in the routers is minimized. Authors in [132] perform a thorough study on the effectiveness of deflection routing for different NoC topology and routing algorithm. Deflection routing is also used in industrial priority-aware NoC [88]. Since arbitrary deflections can cause livelocks and unpredictable latency, industrial priority-aware NoCs deflect the packets only at the destination nodes when the ingress buffer is full. Furthermore, the deflected packets always remain within the same row or column, and they are guaranteed to be sunk after a fixed number of deflections.

An analytical bound on maximum delay in networks with deflection routing is presented in [31]. However, evaluating maximum delay is not useful since it leads to significant overestimation. Another analytical model for NoCs with deflection routing is proposed in [66]. The authors first compute the blocking probability at each port of a router using an M/G/1 queuing model. Then, they compute the contention matrix at each router port. The average waiting time of packets at each port is computed using the contention matrix. However, this analysis ignores different priority classes and applies to only continuous-time queuing systems.

Several techniques present performance analysis of priority-based

queuing networks outside the NoC domain [19, 28, 85]. Nevertheless, these techniques do not consider multiple traffic classes in the same queue. The work presented in [13] considers multiple traffic classes, but it assumes that high priority packets preempt the lower priority packets. However, this is not a valid assumption in the NoC context. A technique that can handle two traffic classes, Empty Buffer Approximation (EBA), has been proposed in [18] for a priority-based queuing system. This approach was later extended to multi-class systems [91]. However, EBA ignores the residual time caused by low priority flits on high priority traffic. Hence, it is impractical to use EBA for priority-aware industrial NoCs.

The aforementioned prior studies assume a continuous-time queuing network model, while the events in synchronous NoCs take place in discrete clock cycles. A discrete-time priority-based queuing system is analyzed in [202]. This technique forms a Markov chain for a given queuing system, then analyzes this model in z-domain through probability generating functions (PGF). PGFs deal with joint probability distributions where the number of random variables is equal to the number of traffic classes in the queuing system. This approach is not scalable for systems with large number of traffic classes because the corresponding analysis becomes intractable. For example, an industrial  $8\times 8$  NoC would have 64 sources and 64 destinations which will result in 4096 ( $64\times 64$ ) variables with PGF. Furthermore, our approach outperforms this technique, as demonstrated in Chapter 5.

In contrast to prior approaches, we propose a scalable and accurate closed form solution for a priority-based queuing network with deflection routing executing multi-class bursty traffic. The proposed technique constructs end-to-end latency models using two canonical structures identified for priority-based NoCs. Unlike prior approaches, our technique scales to any number of traffic classes. To the best of our knowledge, this is the first analytical model for priority-based NoCs that considers both (1)

shared queues among multiple priority classes and (2) traffic arbitration dependencies across the queues.

Multiple prior studies have proposed NoC performance analysis techniques with basic round-robin arbitration. [158, 63, 174]. Authors in [158] first construct a contention matrix between multiple flows in the NoC. Then, the average waiting time of the packets corresponding to each flow is computed. Support vector regression-based analytical model for NoCs is proposed in [174]. The analytical model proposed in [63] estimates the mean service time of the flows with RR arbitration. The estimated mean service time is used to find the average waiting time of the flows. However, none of these techniques are applicable in the presence of both bursty traffic and WRR arbitration.

Analytical modeling of round-robin arbitration has also been studied outside NoC domain [30, 71, 205]. The techniques presented in [30, 71] incorporate a polling model to approximate the effective service time of a queue in the presence of RR arbitration. However, none of these approaches are applicable when the input distribution to the queue is not geometric. A Markov chain-based analytical model is proposed in [205] to account for bursty input traffic. However, the technique is not scalable for a network of queues. Moreover, none of these techniques are applicable for discrete-time queuing systems. Since each transaction in NoC happens at discrete clock cycles, the analytical models need to incorporate discrete-time queuing systems. The major drawbacks of the prior approaches are summarized in Table 8.1.

The basic round-robin arbitration cannot provide fairness when requesters have widely varying data rate requirements and priorities. Therefore, weighted round-robin arbitration, i.e., WRR, has been used in on-chip communication architectures [172, 76]. Qian et al. compute delay bounds for different channels with different weights to assign appropriate weight to each input channel of the NoC [172]. They show that WRR delivers

Table 2.1: Comparison of prior research and our novel contribution.

| Research                     | Approach                   | WRR | Bursty<br>Traffic | Scalable | Discrete<br>Time |

|------------------------------|----------------------------|-----|-------------------|----------|------------------|

| Boxma et al. [30]            | Polling model              | No  | No                | Yes      | No               |

| Wim et al. [71]              | Extended polling model     | No  | No                | Yes      | No               |

| Wang et al. [205]            | Markov chain               | No  | Yes               | No       | No               |

| Fischer et al. [63]          | Heuristic                  | No  | No                | Yes      | No               |

| Vanlerbergee<br>et al. [199] | Moment generating function | No  | No                | No       | Yes              |

| This work                    | Queue decomposition        | Yes | Yes               | Yes      | Yes              |