# Energy-Efficient Data Processing Using Accelerators

By Amin Farmahini Farahani

A dissertation submitted in partial fulfillment of the requirements for the degree of

**Doctor of Philosophy**

(Electrical Engineering)

at the

UNIVERSITY OF WISCONSIN-MADISON

2015

Date of final oral examination: 12/22/2014

The dissertation is approved by the following members of the Final Oral Committee:

Nam Sung Kim, Associate Professor, Electrical and Computer Engineering

Katherine Morrow, Associate Professor, Electrical and Computer Engineering

Mark D. Hill, Gene M. Amdahl Professor and Department Chair, Computer Sciences

Mikko H. Lipasti, Philip Dunham Reed Professor, Electrical and Computer Engineering

Xinyu Zhang, Assistant Professor, Electrical and Computer Engineering

Dedicated to Zari, Mori, and Moien

## Acknowledgments

This dissertation would not have been possible without the help of my family, professors, and friends. I would like to thank those who helped me in the past few years.

I owe my gratitude to a long list of people. I would like to thank Dr. Michael Schulte, my former adviser, for his guidance throughout my graduate studies even to this date. I would also like to thank my current advisers, Dr. Katherine Morrow and Dr. Nam Sung Kim, for their instruction and guidance throughout my graduate school career. I cannot express how grateful I am. I would like to thank Dr. David Wood for many things I learned from him. I would also like to thank Dr. Mark Hill, Dr. Mikko Lipasti, and Dr. Xinyu Zhang for being a member of my dissertation committee. Dr. Hill and Dr. Lipasti made time to meet with me and provided valuable feedback on my research and career opportunities.

I would like to express my gratitude to Dr. Wesley Smith, Tom Gorski, and Robert Fobes at the Physics Department for their support and cooperation in the early years of my graduate career.

During my internship at Nvidia and Qualcomm, I was fortunate to work under direction of Greg Palmer, Lacky Shah, Jeff Shabel, and Simon Booth. My experience of working with them greatly helped me develop my research aptitude. I am grateful for their support during and after the internship.

My fellow graduate students have played an important role in assisting me in these years. I would like to express my thanks to Atif Hashmi, Andrew Nere, Syed Zohaib Gilani, Arslan Zulfiqar, David Palframan, Vignyan Reddy, Dibakar Gope, Tony Gregerson, Jie Liu, Vinod Reddy, Jacob Adriaens, Chris Jenkins, Kyle Rupnow, Daniel Chang, Daniel Seemuth, Hadi Asgharimoghaddam, Mohammad Alian, Somayeh Sardashti, Hamid Reza Ghasemi, Aishwarya Nagarajan, Mitch Hayenga, Sean Franey, Paula Aguilera, Hao Wang, Zhenhong Liu, Shreesha

Srinath, Tony Nowatzki, Yuefi Zhao, Srinivasan Narayanamoorthy, Philip Garcia, Felix Loh, Henry Duwe, Charles Tsen, and Jungseob Lee for their support and company.

If I want to thank only one of my friends, it would definitely be Shirzad Malekpour. He has always been here for me in good times and bad. I am also very grateful to Anaram Shahravan for her support. I express my gratitude to my friends Diba Izadyar, Sheida Malekpour, Arsham Shahlari, Arash Sangari, Hasti Mirkia, Omid Forouzan, Elham Ahmadi, Arman Pazouki, Mozhdeh Rajaei, Hasan Tabatabaie, Chiya Saeidi, and Solmaz Forutan. I also owe a debt of gratitude to Shirin Malekpour and Peiman Hematti for helping me when I needed the most.

Finally, I would like to express my deep gratitude to my mother, father, and brother for supporting me. Their encouragement and love were the great power for me to overcome all troubles I faced.

I would like to take this opportunity to raise concern about the place that I worked in for a few years. I believe that the Department of Electrical and Computer Engineering at the University of Wisconsin-Madison is going downhill in several aspects. I have been really proud of working in this department and I really hope that things change for the better. But I unfortunately do not see any good signs as of now. Returning back to the department in a couple of years, I long for a thriving department as it once used to be.

#### **Abstract**

Energy efficiency of computing systems has become crucial with the end of Dennardian scaling in which voltage scaling has stalled, thereby increasing power density with decreasing transistor size. One method to improve energy efficiency is to use accelerators specialized for a certain set of computing problems. Unlike traditional general-purpose processors, such an accelerator avoids the overhead of fetching and scheduling instructions. Supporting reconfigurability for accelerators can provide acceleration for a broader range of applications. This dissertation document investigates architectural techniques to enable energy-efficient data processing using reconfigurable accelerators and explores two aspects of this area: customizing L1 data caches for computing systems integrated with reconfigurable accelerators, and proposing a near-memory data processing architecture to decrease the energy consumption of data transfers between compute-engines and memory.

Data transfers between accelerators and memory are often a bottleneck for both performance and energy efficiency. This dissertation document demonstrates the potential of a configurable L1 data cache to exploit diversity in cache requirements across hybrid applications that use hardware accelerators. Configurable caches improve energy efficiency while maintaining high performance. One configurable feature is the cache topology; it can be reconfigured as a set of private L1 caches, or a single L1 cache shared by a processor and an accelerator. This dissertation also proposes a technique for L1 caches to provide a configurable tradeoff between the number of cache ports and its capacity.

To further reduce the overhead of transferring data between compute-engines and memory, this dissertation proposes NDA (Near-DRAM Acceleration), an architecture that stacks low-power, flexible reconfigurable accelerators atop off-chip commodity DRAM devices. The accelerators can thus access data directly near DRAM, without the need to bring data from off-

chip DRAM devices through the memory hierarchy of the host processor. To make this architecture attractive to industry and practical in the short run, we take commodity 2D DRAM devices and make minimal changes to DRAM devices to provide, in a practical way, highbandwidth connections between accelerators and DRAM devices for the purpose of near-memory processing. The proposed NDA architecture requires no change to the host processor design and minimal changes to the commodity DRAM device while maintaining the compatibility with the standard DRAM interface and DIMM architecture. This dissertation explores three NDA microarchitectures to stack accelerators atop DRAM devices and analyzes the impact of supporting such NDA microarchitectures on DRAM area, timing, and energy in detail. The first NDA microarchitecture connects accelerators and DRAM through global I/O lines (inter-bank datalines) that are shared between all DRAM banks. In the second NDA microarchitecture, global I/O lines are doubled to increase the internal bandwidth between accelerators and DRAM. The third microarchitecture connects accelerators and DRAM through global datalines that are private to each DRAM bank, substantially increasing DRAM internal bandwidth. This dissertation also identifies various software and hardware challenges in implementing the proposed NDA architecture (e.g., processor-accelerator and DRAM-accelerator communications due to sharing the main memory system with the host processor) and provides cost-effective solutions.

# Contents

| Ack  | now                         | ledgmei | ntsii                                                           |  |  |  |  |

|------|-----------------------------|---------|-----------------------------------------------------------------|--|--|--|--|

| Abs  | trac                        | t       | iv                                                              |  |  |  |  |

| Con  | tent                        | S       | vi                                                              |  |  |  |  |

| List | of T                        | ables   | ix                                                              |  |  |  |  |

| List | of F                        | igures  | X                                                               |  |  |  |  |

| 1    | Introduction                |         |                                                                 |  |  |  |  |

|      | 1.1                         | Motiv   | ation                                                           |  |  |  |  |

|      | 1.2                         | Recor   | figurable Cache Architectures for Processor-Accelerator Systems |  |  |  |  |

|      | 1.3                         | NDA:    | Near-DRAM Acceleration                                          |  |  |  |  |

|      | 1.4                         | Contri  | ibutions                                                        |  |  |  |  |

|      | 1.5                         | Disser  | rtation Organization                                            |  |  |  |  |

| 2    | Background and Related Work |         |                                                                 |  |  |  |  |

|      | 2.1                         | Recon   | figurable Accelerators                                          |  |  |  |  |

|      |                             | 2.1.1   | Coarse-grain Reconfigurable Accelerators (CGRAs)                |  |  |  |  |

|      |                             | 2.1.2   | Interfaces between Reconfigurable Accelerators and Processors   |  |  |  |  |

|      | 2.2                         | Caches  |                                                                 |  |  |  |  |

|      |                             | 2.2.1   | High-Bandwidth Caches                                           |  |  |  |  |

|      |                             | 2.2.2   | Configurable Cache Architectures                                |  |  |  |  |

|      | 2.3                         | Memo    | ory 22                                                          |  |  |  |  |

|     |       | 2.3.1                  | Dynamic Random-Access Memory (DRAM)                         | 22        |

|-----|-------|------------------------|-------------------------------------------------------------|-----------|

|     |       | 2.3.2                  | Processor-in-Memory (PIM) Systems                           | 23        |

| 3   | Exp   | oerimen                | ıtal Framework                                              | 28        |

|     | 3.1   | Perfo                  | rmance Simulation Infrastructure                            | 28        |

|     | 3.2   | Powe                   | r Modeling                                                  | 29        |

|     | 3.3   | Bencl                  | hmark Development                                           | 31        |

| 4   | Rec   | configur               | rable Cache Architectures for Processor-Accelerator Systems | 33        |

|     | 4.1   | Syste                  | m Overview and Experimental Methodology                     | 33        |

|     | 4.2   | Bencl                  | hmarks                                                      | 35        |

|     | 4.3   | Motiv                  | vation for Reconfigurable L1 Data Caches                    | 36        |

|     | 4.4   | Confi                  | gurable L1D Organization                                    | 41        |

|     |       | 4.4.1                  | Overhead                                                    | 42        |

|     |       | 4.4.2                  | Results                                                     | 44        |

|     | 4.5   | 4.5 Configurable Ports |                                                             | 48        |

|     |       | 4.5.1                  | Overhead                                                    | 49        |

|     |       | 4.5.2                  | Results                                                     | 51        |

|     | 4.6   | Sumn                   | nary                                                        | 57        |

| 5   | ND    | A: Neai                | r-DRAM Acceleration Architecture Leveraging Commodity DRAM  | A Devices |

| ano | d Sta | ndard N                | Memory Modules                                              | 59        |

|     | 5.1   | Back                   | ground                                                      | 59        |

|     |       | 5.1.1                  | DRAM Architecture                                           | 59        |

|     |       | 5.1.2                  | Accelerator Architecture                                    | 62        |

| 5.2 | NDA                                    | Hardware Architecture                                                                                                                                              | 63                                            |

|-----|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

|     | 5.2.1                                  | Connection between Accelerator and DRAM                                                                                                                            | 64                                            |

|     | 5.2.2                                  | Memory Access by Accelerators                                                                                                                                      | 71                                            |

|     | 5.2.3                                  | Processor-Accelerator Communication                                                                                                                                | 75                                            |

| 5.3 | Softw                                  | vare Considerations                                                                                                                                                | 76                                            |

|     | 5.3.1                                  | Target Applications                                                                                                                                                | 76                                            |

|     | 5.3.2                                  | Data Arrangement for Accelerators                                                                                                                                  | 76                                            |

|     | 5.3.3                                  | Programming for NDA                                                                                                                                                | 78                                            |

|     | 5.3.4                                  | Data Coherence and Memory Consistency                                                                                                                              | 80                                            |

| 5.4 | Evalu                                  | nation Methodology                                                                                                                                                 | 81                                            |

|     | 5.4.1                                  | Benchmarks                                                                                                                                                         | 81                                            |

|     | 5.4.2                                  | Architectural Components                                                                                                                                           | 82                                            |

|     | 5.4.3                                  | Evaluated Architectures                                                                                                                                            | 87                                            |

| 5.5 | Resul                                  | lts                                                                                                                                                                | 87                                            |

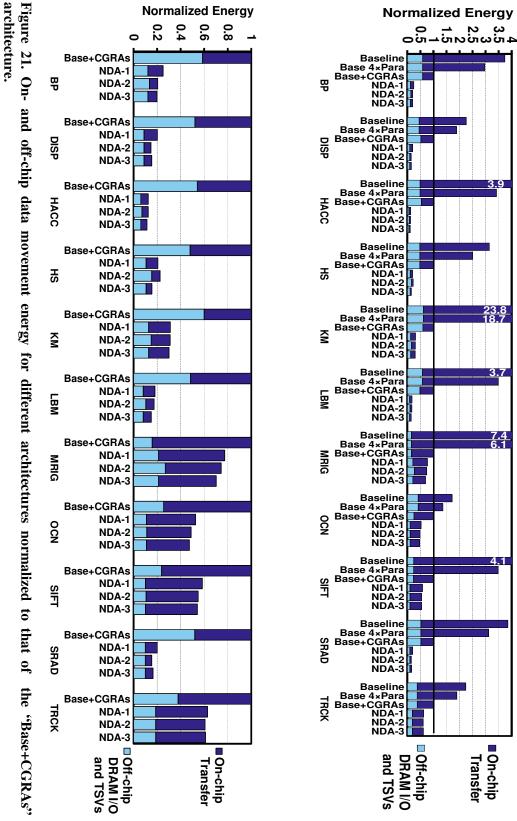

|     | 5.5.1                                  | Data Transfer (Movement) Energy                                                                                                                                    | 88                                            |

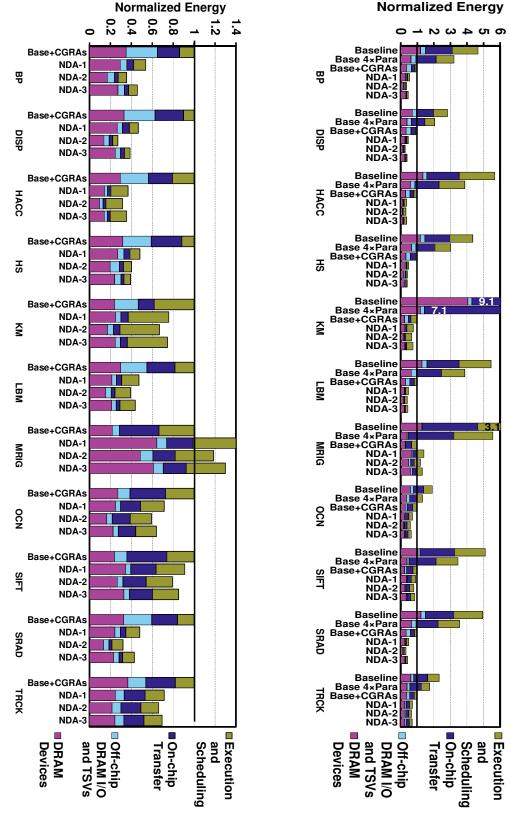

|     | 5.5.2                                  | Total Energy                                                                                                                                                       | 91                                            |

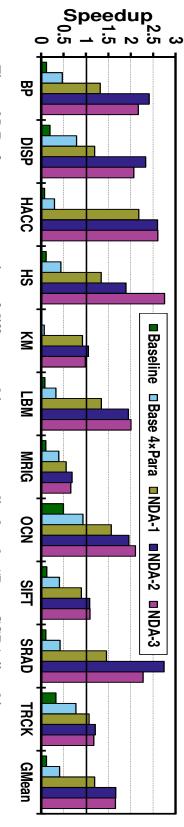

|     | 5.5.3                                  | Speedup Comparison                                                                                                                                                 | 92                                            |

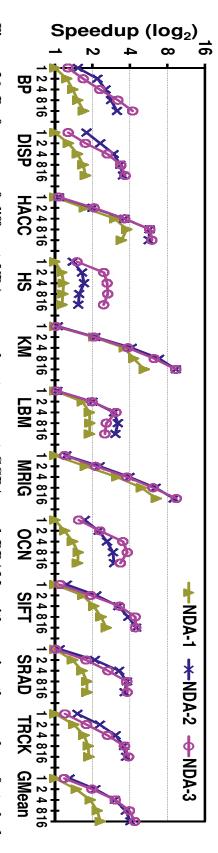

|     | 5.5.4                                  | Sensitivity to CGRA-DRAM Connection Type                                                                                                                           | 95                                            |

|     | 5.5.5                                  | Sensitivity to CGRA Computing Capability                                                                                                                           | 95                                            |

|     | 5.5.6                                  | NDA×8 versus ×16                                                                                                                                                   | 98                                            |

| 5.6 | Sumn                                   | mary                                                                                                                                                               | 98                                            |

| Coı | nclusion                               | 1                                                                                                                                                                  | 100                                           |

| 6.1 | Futur                                  | re Directions                                                                                                                                                      | 102                                           |

| Pul | olication                              | ns                                                                                                                                                                 | 106                                           |

| Ref | erences                                | S                                                                                                                                                                  | 108                                           |

|     | 5.3<br>5.4<br>5.5<br>Con<br>6.1<br>Pub | 5.2.1 5.2.2 5.2.3  5.3 Softw 5.3.1 5.3.2 5.3.3 5.3.4  5.4 Evalu 5.4.1 5.4.2 5.4.3  5.5 Resu 5.5.1 5.5.2 5.5.3 5.5.4 5.5.5 5.5.6  Conclusion 6.1 Futur  Publication | 5.2.1 Connection between Accelerator and DRAM |

# List of Tables

| Table 1. Key architecture parameters for processor                                                                                                                                                                                                           | . 35 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Table 2. Benchmarks used in the evaluation of reconfigurable caches                                                                                                                                                                                          | . 36 |

| Table 3. L1D cache design parameters ( <i>size:ports:associativity</i> ) with the lowest EDP for each benchmark/architecture combination, subject to the listed maximum slowdown relative                                                                    |      |

| to the baseline L1D cache (a 32KB, single-port 4-way set associative L1D). In each table                                                                                                                                                                     |      |

| cell, the percentage is the EDP savings of a cache with the listed design parameters over that of the baseline cache                                                                                                                                         | 39   |

| of the baseline cache                                                                                                                                                                                                                                        | . 57 |

| Table 4. Energy consumption of different types of dual-port caches implemented in 32 nm technology.                                                                                                                                                          | . 50 |

| Table 5. Area, timing, and energy parameters of an 8Gb DDR3-1600 ×8 DRAM device. ×8 = off-chip data I/O bit-width is 8                                                                                                                                       | . 70 |

| Table 6. Summary of bandwidth, area, timing, and energy of different microarchitectures to connect Accelerators and DRAM devices. Numbers are relative to DDR3-1600 ×8 parameters given in Table 5. S/A = Sense Amplifiers. Some data in this table has been |      |

| obtained by Prof. Ahn at Seoul National University                                                                                                                                                                                                           | . 70 |

| Table 7. Benchmarks used in our evaluation.                                                                                                                                                                                                                  | . 82 |

| Table 8. Design parameters of 32-bit CGRA with 64 and 32 FUs                                                                                                                                                                                                 | . 84 |

| Table 9. Key processor architecture parameters                                                                                                                                                                                                               | . 84 |

| Table 10. DRAM subsystem parameters                                                                                                                                                                                                                          | . 86 |

| Table 11 Summary of different architectures evaluated in this chapter                                                                                                                                                                                        | 88   |

# List of Figures

| Figure 1. Combined processor and DRAM energy consumption                                                                                    | 2            |

|---------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Figure 2. Energy scaling projections of DRAM access and communication, global wire                                                          |              |

| transition, floating point arithmetic operation, L1 cache access, and register file access. Data is extracted from [7], [98], [161], [162]. | 1            |

| is extracted from [7], [90], [101], [102]                                                                                                   | <del>1</del> |

| Figure 3. A CGRA with a grid of 2×2 functional units                                                                                        | . 15         |

| Figure 4. Interleaving schemes in dual-bank caches. (a) line interleaving (b) word interleaving.                                            | . 20         |

| Figure 5. Processor-accelerator architectures: (a) Processor and accelerator with a shared L1                                               |              |

| data cache, (b) Processor and accelerator with private L1 data caches                                                                       | . 34         |

| Figure 6. High-level structure of the proposed reconfigurable L1D cache organization                                                        | . 41         |

| Figure 7. Performance and energy consumption of a shared L1D organization with (16:2:2)                                                     |              |

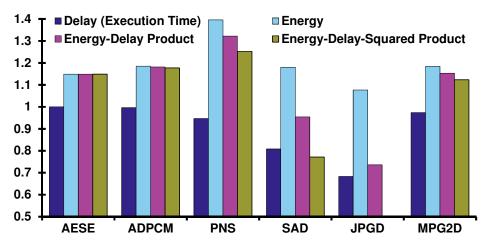

| design parameters over a private L1D organization with (8:1:2), (8:2:1) design parameters                                                   | . 44         |

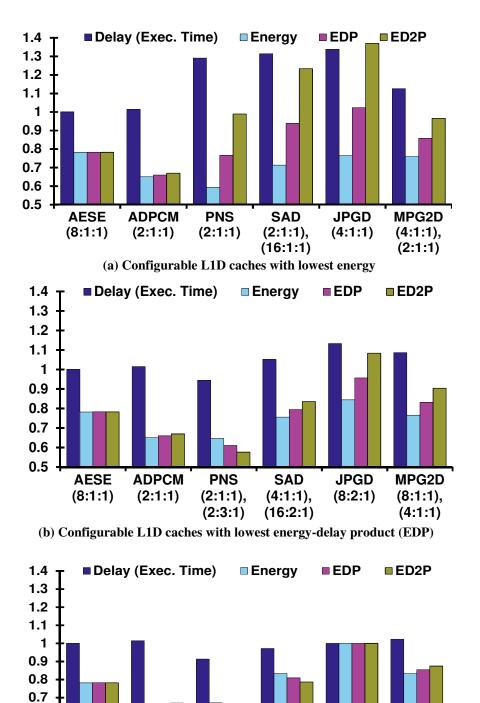

| Figure 8. Result summary of configurable L1D caches normalized to an L1D cache with (16:2:2) design parameters (Lower is better).           | . 47         |

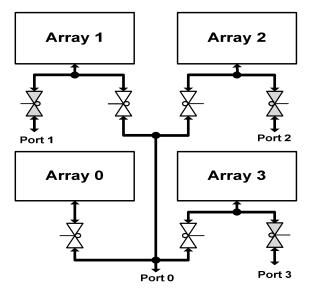

| Figure 9. High-level structure of a configurable-port cache that can be configured as a                                                     |              |

| single-, dual-, triple-, or quad-port cache. The added logics are indicated by shaded blocks                                                | . 49         |

| Figure 10. Results summary of configurable-port, true multi-port, and multi-bank caches                                                     |              |

| normalized to a single-port cache. Caches are 16KB, 2-way set associative . The notations                                                   |              |

| 'p', 'b', 'True', 'CP', 'LI', and 'WI' stand for ports, banks, true multi-porting, configurable                                             |              |

| multi-porting, line-interleave banking, and word-interleave banking, respectively                                                           | . 54         |

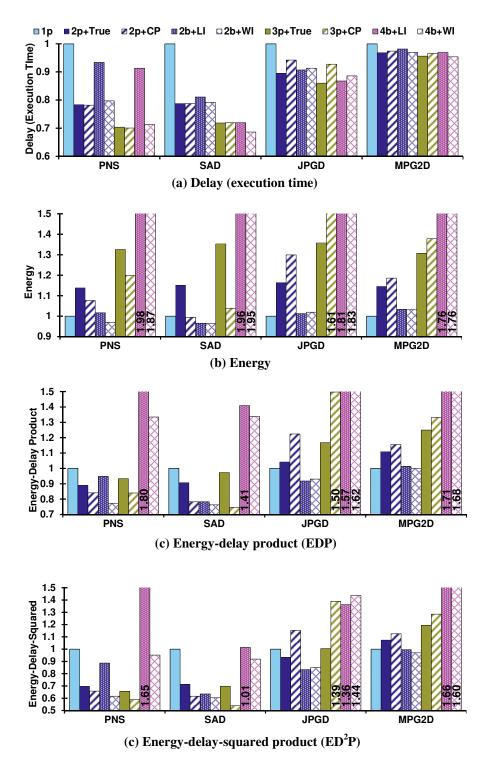

| Figure 11. Results summary of configurable dual-port L1D caches with different sizes                                                        |              |

| relative to a 2KB cache (Lower is better).                                                                                                  | . 57         |

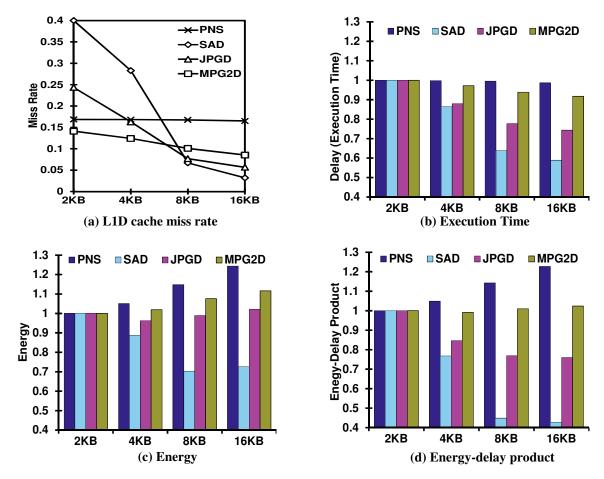

| Figure 12. Conventional DRAM organization. A DDR3 device with 8 banks of A to H and          |

|----------------------------------------------------------------------------------------------|

| ×8 I/O interface (center), internal architecture of a DRAM bank and a mat (left), and DRAM   |

| I/O datapath (right)                                                                         |

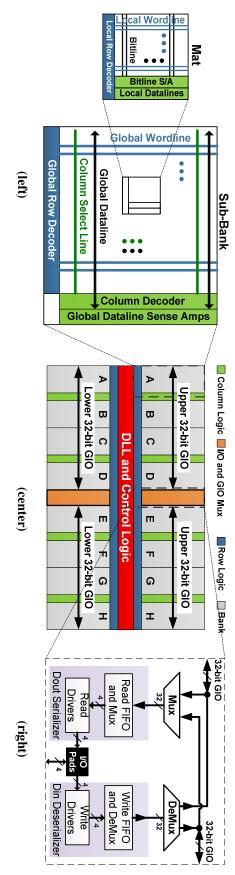

| Figure 13. NDA organization. 64                                                              |

| Figure 14. Accelerator-DRAM connection by connecting TSVs to existing GIO lines              |

| Figure 15. Accelerator-DRAM connection by connecting TSVs to doubled GIO lines 66            |

| Figure 16. Accelerator-DRAM connection by connecting TSVs to global datalines of banks 67    |

| Figure 17. Accelerator stacked on top of a DRAM device                                       |

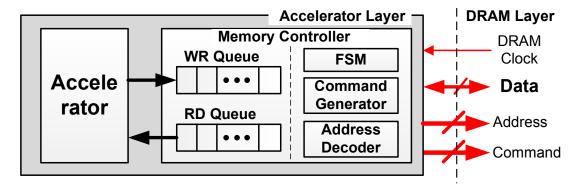

| Figure 18. Access to mode, status, and kernel registers                                      |

| Figure 19. Data arrangement across devices for a 4×4 array of 32-bit words (A – R). Original |

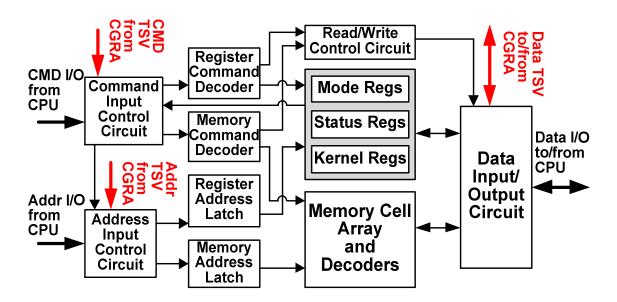

| data arrangement (top) and shuffled arrangement for NDA acceleration (bottom)                |

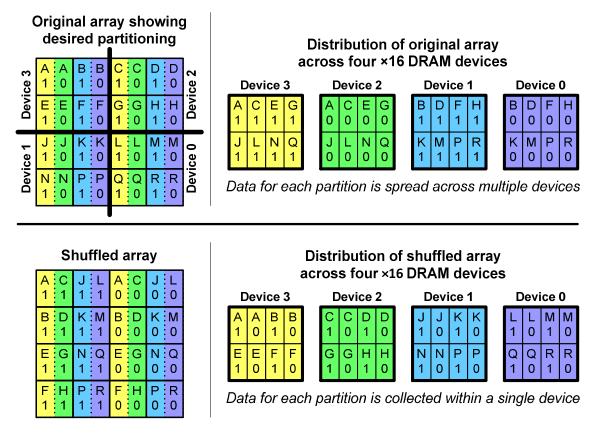

| Figure 20. NDA programming model                                                             |

| Figure 21. Execution flow of programs mapped to NDA                                          |

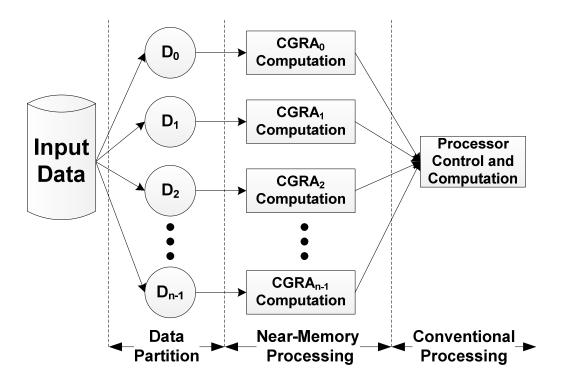

| Figure 22. On- and off-chip data movement energy for different architectures normalized to   |

| that of the "Base+CGRAs" architecture                                                        |

| Figure 23. Combined processor, DRAM, and CGRA energy consumption for different               |

| architectures normalized to that of the "Base+CGRAs" architecture. Figure 24. On- and off-   |

| chip data movement energy for different architectures normalized to that of the              |

| "Base+CGRAs" architecture                                                                    |

| Figure 25. Performance comparison of different architectures normalized to the               |

| "Base+CGRAs" architecture                                                                    |

| Figure 26. Performance of different NDA approaches to connect CGRAs and DRAMs with           |

| varying the number of stacked CGRAs (x axis) normalized to performance of NDA-1 with         |

| one CGRA stacked atop a DRAM. CGRAs have 64 FUs running at 800 MHz and are            |      |

|---------------------------------------------------------------------------------------|------|

| stacked atop ×8 DRAM devices                                                          | . 94 |

|                                                                                       |      |

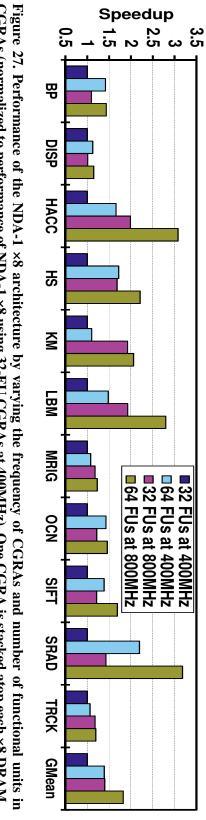

| Figure 27. Performance of the NDA-1 ×8 architecture by varying the frequency of CGRAs |      |

| and number of functional units in CGRAs (normalized to performance of NDA-1 ×8 using  |      |

| 32-FU CGRAs at 400MHz). One CGRA is stacked atop each ×8 DRAM                         | . 97 |

## 1 Introduction

As transistors continue to scale with each new process technology, power density of a chip increases since operating voltage remains roughly constant. This results in higher energy consumption with the continued increase in number of chip transistors. As a result, energy consumption has become a major target for computer architecture researchers to tackle. Specialization of computing structures for required operations allows reduction in energy consumption and performance improvement by more efficiently using silicon area. This chapter motivates using specialized hardware accelerators to increase energy efficiency. It also introduces techniques to improve energy efficiency of data communication in accelerated systems and presents an architecture that uses accelerators for data processing near memory.

#### 1.1 Motivation

Energy efficiency concerns have driven a shift from traditional computer architecture designs to heterogeneous design techniques, such as using specialized domain-specific or application-specific accelerators. Accelerators can reduce the energy penalty of instruction-based execution by implementing computations as circuits rather than programs stored in memory that must be retrieved instruction by instruction in order to be executed. The performance and energy efficiency benefits of specialized accelerators over general-purpose processors allow a designer to considerably improve system energy efficiency by trading the relatively cheap commodity of area for the expensive commodity of energy [1], [2].

Unlike ASIC cores that accelerate only a single specific computation (or a very small set of them), Reconfigurable accelerators are flexible structures can be specialized post-fabrication [3]

to accelerate a wide variety of computations by implementing different accelerator circuits at different times. Reconfigurable accelerators perform compute-intensive operations more quickly with less energy than traditional processors [4] by exploiting spatial parallelism in application *kernels* (compute-intensive portions of an application) to implement computations as parallel circuits.

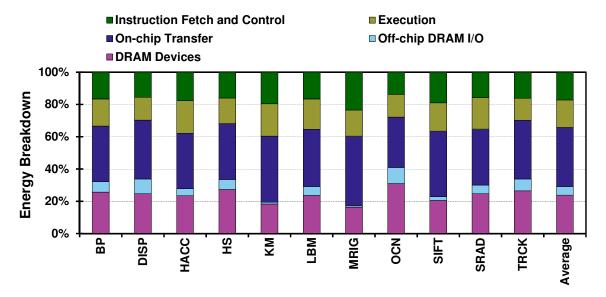

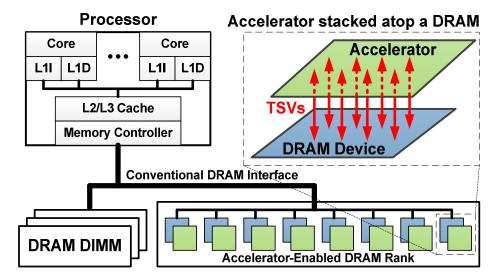

Figure 1 shows the energy dissipation breakdown of an out-of-order processor and DRAM devices over 11 different scientific and multimedia applications (refer to Chapter 3 and Section 5.4.1 for evaluation methodology and benchmark descriptions). We categorize the energy dissipation into five components. The "instruction fetch and control" component comprises energy dissipation of fetching and scheduling instructions in the processor. The "execution" component represents the energy dissipated in processor execution units. The "on-chip transfer" component includes energy dissipation of the register file, cache hierarchy, LSQ, and buses. The "off-chip DRAM I/O" represents energy dissipation of the memory I/O interface. Finally, the "DRAM devices" component represents energy dissipation of memory subsystem. In our tested applications, 17% of the total system energy is spent in the overheads of fetching and scheduling

Figure 1. Combined processor and DRAM energy consumption.

instructions. This indicates significant potential for reconfigurable accelerators to reduce energy by flexibly, but efficiently, performing computation tasks without instruction-based execution. In addition, accelerators speed up application execution, reducing system's leakage energy.

However, the performance and energy efficiency benefits of systems with accelerators greatly depend upon how they are integrated into the memory hierarchy [5]. If they use a shared-memory communication paradigm, the data cache architecture has a strong effect on the system's performance and energy efficiency. However, conventional processor cache architectures do not necessarily provide an efficient solution for reconfigurable accelerators because of differences in memory access patterns and bandwidth requirements. Therefore, we propose techniques for improving energy-efficiency of the cache hierarchy in processor-accelerator systems (Section 1.2).

Tailoring the cache design to the needs of systems with reconfigurable accelerators improves energy efficiency considerably, but it still leaves room for improvement. An important source of energy inefficiency in current computing systems originates from moving data between where it is stored and where it is processed. The processor usually must transfer data from off-chip dynamic random access memory (DRAM) devices to its on-chip cache hierarchy and then into its register file before processing it. Energy consumed by this data movement is much higher than that consumed by actual data computation. For example, reading a data word from an L1 cache consumes about an order of magnitude more energy than performing an arithmetic operation on a data word [6]. Figure 1 shows that on average data movement (both on-chip and off-chip) constitutes 42% of total energy. As a result, data movement is the major component of the total system energy.

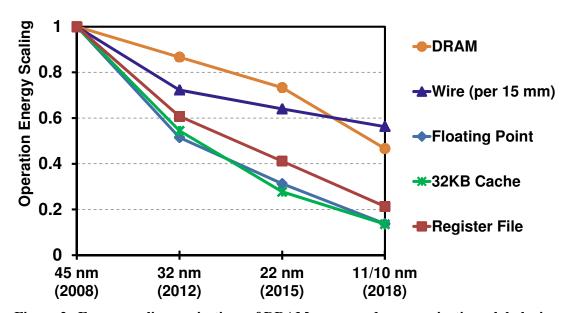

Furthermore, the contribution of data movement energy to the total system energy is projected to increase even further with technology scaling [7], [8]. Figure 2 compares the rate in

which data computation and data movement energy scales in future process technologies. Figure 2 shows that data computation energy (ALU operations) scales well in future processor technologies, but data movement energy on global wires does not decrease significantly because wire capacitance per distance unit (mm) does not scale as suitably as transistor switching capacitance [7]. Therefore, we expect that data movement energy dominates total system energy in future process technologies. To address challenges associated with ever-increasing data movement energy, we propose architectural innovations to enable local data processing using accelerators (Section 1.3).

This dissertation studies energy reduction and performance improvement opportunities through novel design techniques and heterogeneous architectures that exploit reconfigurable accelerators. To lay the foundation for this research, we begin by examining heterogeneous architectures that couple an embedded processor and a reconfigurable accelerator through a shared-memory cache hierarchy. We explore data cache requirements for these architectures and

Figure 2. Energy scaling projections of DRAM access and communication, global wire transition, floating point arithmetic operation, L1 cache access, and register file access. Data is extracted from [7], [98], [161], [162].

find cache design parameters that achieve high energy efficiency for different hybrid software/accelerated applications. Guided by this exploration, we investigate configurable cache design techniques that allow the designer to adapt the L1 data cache structure according to cache requirements across hybrid applications. To reduce data movement energy, We then propose a near-memory processing architecture that use reconfigurable accelerators stacked atop of commodity DRAM devices to process data close to where it is stored. We propose microarchitectures to increase the memory bandwidth between DRAM devices and reconfigurable accelerators in our near-memory processing architecture. Finally, we identify various software and hardware challenges in implementing our proposed architecture and provide novel cost-effective solutions.

# 1.2 Reconfigurable Cache Architectures for Processor-Accelerator Systems

Prior studies have primarily examined the performance of accelerator architectures or specific application implementations on reconfigurable computing platforms. Few efforts have examined the effects of cache design on energy efficiency of systems composed of embedded processors and reconfigurable accelerators implemented on a single chip using ASIC technology. In this dissertation, we revisit cache design decisions made for general-purpose multi-core processors based on the unique needs of a reconfigurable accelerator. Specifically, we study energy-efficient, high-bandwidth cache designs for embedded systems with reconfigurable accelerators.

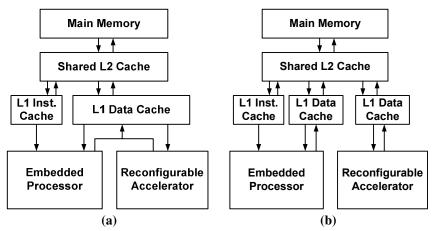

We first investigate the impact of cache design and organization on energy efficiency of heterogeneous architectures that couple an embedded processor with a reconfigurable accelerator through a shared-memory cache hierarchy on a single chip. We call these architectures *processor-accelerator* architectures. In these architectures, software codes are run on the processor, while

application kernels are implemented in the accelerator. This results in faster computation and/or less energy consumption due to the specialized computational structures in the accelerator.

Accelerators exhibit different memory access pattern and memory access rate when compared to processors. Therefore, cache design requirements of these architectures are different from those of processor-only architectures. First, memory access patterns differ between a processor executing primarily or entirely sequential software code and a reconfigurable accelerator that implements a highly-parallel circuit. Second, the memory access rate of a reconfigurable accelerator is quite different from that of a processor running a functionally-equivalent software application. An accelerator performs potentially many parallel computations, and thus generally accesses memory at a higher rate than a processor. Unlike processors, accelerators also often issue separate bursts of read and write requests which favor high-bandwidth data communication methods to accommodate higher memory access rate [9], [10].

Therefore, reconfigurable accelerator's caches should be carefully designed based on the characteristics of the applications expected to use them. We explore the design space of L1 data caches to find a set of cache parameters that improve energy efficiency of processor-accelerator architectures. Guided by this exploration, we propose modifications to the L1 data cache level in processor-accelerator architectures to maximize energy efficiency of data caches in embedded systems in which processors and accelerators communicate through the cache hierarchy..

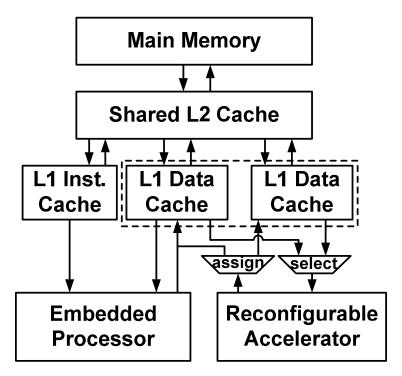

We propose a configurable data cache interface that allows the processor and accelerator to either share an L1 data cache or have their own private data caches. In fact, this interface allows having two different L1 data cache organizations in processor-accelerator architectures (acting as a single shared L1 data cache or two private L1 data caches). My goal is to provide an interface that enables a designer to select the organization with better energy efficiency based on the executing hybrid application.

Next, we propose a configurable cache port design that allows a designer to increase the number of cache ports by trading off cache capacity in processor-accelerator architectures. Some hybrid applications benefit from high-bandwidth caches due to reduction in execution time, while the performance of some other applications is not highly improved by multi-port caches. For these applications, using multi-port caches leads to unnecessary higher energy dissipation without noticeable performance improvement. Based on this observation, a configurable cache port design can improve the performance of hybrid applications that benefit from multi-port caches by configuring the cache as a multi-port cache, while it keeps the energy consumption low for other hybrid applications by configuring the cache as a single-port cache (Section 4.5). A configurable cache port design provides a tradeoff between L1 data port count and capacity to better support a variety of accelerated application kernels. To evaluate the configurable port cache design, we compare its performance and energy consumption with the various existing design techniques to implement multi-port caches.

#### 1.3 NDA: Near-DRAM Acceleration

In approach described in the previous section, the accelerator is located near the processor, and acts as a co-processor. Data must be transferred from off-chip memory to on-chip caches before it can be processed by the accelerator. This data movement constitutes a large portion of the total system power consumption. To reduce data transfer (movement) energy, we can decrease data transfer distance by processing data *near* or *in* memory where it is stored. This motivates us to re-examine the previous processors-in-memory (PIM) architectures [11]–[23] that aimed at improving performance by integrating processor logic and DRAM on the same die. Such PIM architectures, however, suffered from high manufacturing complexity (i.e., low yield), poor processor logic performance, high cost per DRAM bit [24], [25], and high design/verification cost

associated with custom DRAM architectures. Recently, 3D-stacking technology [26]–[30] has emerged as an alternative integration technology. It can solve some of the critical problems faced by the previous PIM architectures because it integrates logic and DRAM layers, each of which is manufactured with dedicated and separate process technology, with high-bandwidth and low-energy TSVs.

Leveraging 3D-stacking technology, researchers have proposed near-DRAM acceleration (NDA) architectures that integrate accelerator logic and *custom* DRAM devices to reap the performance and energy-efficiency benefits of both accelerators and near-memory processing and demonstrated promising results [31]–[34]. More specifically, they focus on either accelerator architecture where its memory system is separate from the host processor's main memory system (similar to a discrete GPU architecture) or the integration of and interaction between accelerators and DRAM using proprietary interfaces.

In this dissertation, we explore a near-memory processing architecture that we call NDA (Near-DRAM Acceleration). In NDA, contrary to prior work, accelerator logic is stacked atop *commodity* "2D" DRAM devices. The goal of NDA is to improve energy efficiency by exploiting local (near-memory) data processing. Commodity DRAM and logic are implemented on separate layers and connected using TSVs. In the NDA architecture, processing elements are physically close to memory devices, avoiding off-chip data communication. Thus, instead of moving data between compute-units and far memory in conventional systems, in this architecture data can be processed near DRAM devices, minimizing the distance of (and therefore energy consumed by) data transfers.

Although, the NDA architecture is not dependent on any specific compute-engines, we use coarse-grain reconfigurable accelerators as compute-engines near memory since they have better performance and energy consumption than SIMD and GPU engines for most parallel workloads

[35]. Low energy is important since near-memory architectures have more stringent power/thermal constraints. In the NDA architecture, reconfigurable accelerators can take advantage of spatial parallelism in applications to speed up a wide range of applications. Furthermore, reconfigurable accelerators can process data much more energy-efficiently compared to processors since they are specialized units.

The NDA architecture does not require major changes to the underlying architecture of commodity DRAM devices apart from additional TSVs. Since even small design changes could affect DRAM's cost-per-bit, DRAM manufactures are not usually amenable to changing the internal architecture of DRAM devices. This is also particularly attractive to DRAM manufacturers looking to provide added value to their products without significant rework or requiring cooperation from large microprocessor companies.

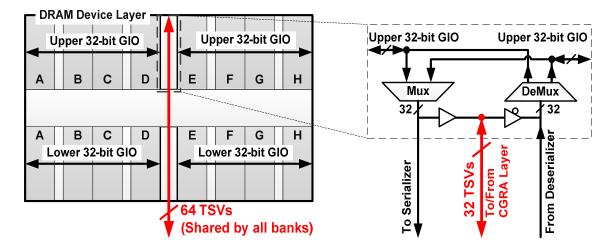

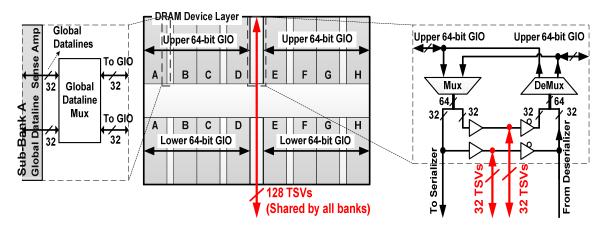

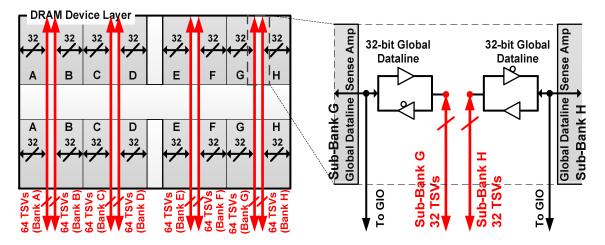

In this dissertation, we discuss hardware challenges to interface reconfigurable accelerators with commodity DRAM devices using TSVs. We propose three microarchitectures to connect reconfigurable accelerators and DRAM devices in the NDA architecture. In the first microarchitecture, TSVs are connected to existing global I/O lines of DRAM. In this microarchitecture, the internal bandwidth between accelerators and DRAM devices is the same as DRAM external (off-chip) data bus. However, the internal DRAM bandwidth can be significantly higher than the off-chip DRAM bandwidth. This higher internal bandwidth can be exploited by a processor-near-memory architecture. Our next two proposed microarchitectures present the opportunity to exploit this higher bandwidth. Higher internal memory bandwidth between accelerators and DRAM devices can improve performance of data-intensive applications mapped to the NDA architecture. In the second microarchitecture, we double global I/O lines and connect TSVs to global I/O lines. In the third microarchitecture, we provide a separate data connection for each DRAM bank and connect TSVs to global datalines. Global datalines, contrary to global I/O

lines, are private to each DRAM bank. We then carefully analyze the impacts of our three microarchitectures on DRAM area, access energy, and timing parameters. For example, we analyze the impact of higher number of TSVs (required to enable higher internal bandwidth) on DRAM area.

We also present software changes required in the applications mapped to NDA to maintain compatibility with the existing DIMM architecture. We analyze performance and energy consumption of our proposed NDA architecture using simulation methods and compare it with conventional computing architectures. Our results show that the NDA architecture improves system performance significantly while also decreasing overall energy consumption.

#### 1.4 Contributions

This dissertation aims to address the growing energy concerns of computing systems by investigating and proposing novel heterogeneous architectures that use reconfigurable accelerators for data processing. Although reconfigurable accelerators traditionally suffered from high area overhead and long reconfiguration time, transistor scaling and scheduling techniques have paved the way for their use in future computing systems. To enable energy-efficient data processing using accelerators, the research presented in this dissertation makes the following contributions:

#### Processor-accelerator architectures

Exploring the design space of L1 data caches for processor-accelerator architectures. We evaluated the impact of cache design parameters such as capacity, number of ports, associativity, and private vs. shared organization on performance and energy consumption of different embedded applications. This investigation provides insights into the cache design requirements of the tested applications.

- Proposing a configurable cache interface that allows the accelerator to either share the processor's L1 data cache or to use its own private L1 data cache. The system can thus switch between two different organizations of the cache hierarchy based on the characteristics of the executing application to provide the best performance and/or energy efficiency.

- Proposing an L1 data cache design with a configurable tradeoff between capacity and port count to tune cache bandwidth based on the currently-running application.

We examined the impact of this cache design on the performance and energy efficiency of embedded applications and compared it with existing design techniques such as true multi-port and multi-bank caches.

#### Processing-near-memory architectures

- Proposing a near-memory processing architecture that we call NDA. This architecture exploits 3D-stacking technology to enable energy-efficient local data processing by coupling reconfigurable accelerators on a logic layer and DRAM devices on a separate memory layer. The NDA architecture that requires no change to the host processor design and minimal changes to the commodity DRAM device's I/O circuitry while maintaining the compatibility with the standard DRAM interface and DIMM architecture.

- Proposing three NDA microarchitectures that can provide diverse DRAM-accelerator bandwidth. We analyze the impact of supporting such microarchitectures on DRAM area, timing, and energy in detail.

- ▶ Identifying software and hardware challenges and proposing solutions. We study different challenges in implementing our NDA architecture (e.g., processor-accelerator

and DRAM-accelerator communications due to sharing the main memory system with the host processor) and provide novel cost-effective solutions.

#### 1.5 Dissertation Organization

This dissertation is organized as follows: Chapter 2 provides a detailed overview of background and related work on configurable caches and processing-in-memory architectures. Chapter 3 discusses the experimental framework, including the simulation infrastructure and benchmarks development methodology. Chapter 4 introduces our configurable cache designs for the L1 cache in the processor-accelerator systems. Our contributions presented in this chapter have been published in the proceedings of IEEE International Symposium on Performance Analysis of Systems and Software (ISPASS) in 2014. Chapter 5 introduces our new near-memory processing architecture and evaluates its performance and energy consumption. Our contributions presented in this chapter have been published in the IEEE Computer Architecture Letters (CAL) in 2014 and the proceedings of IEEE Symposium on High Performance Computer Architecture in 2015. Finally, Chapter 6 concludes the dissertation and summarizes key observations.

# 2 Background and Related Work

This chapter explores related work and background material that is central to this dissertation. Section 2.1 introduces reconfigurable accelerators and summarizes methods to integrate these accelerators into computing systems. Section 2.2 surveys previous work on high-bandwidth and configurable caches. Section 2.3 provides an overview of DRAM devices and covers previous architectures to enable in-memory computing.

#### 2.1 Reconfigurable Accelerators

This section describes the architecture of coarse-grain reconfigurable accelerators and methods employed for transferring data between these accelerators and a system's memory hierarchy.

#### 2.1.1 Coarse-grain Reconfigurable Accelerators (CGRAs)

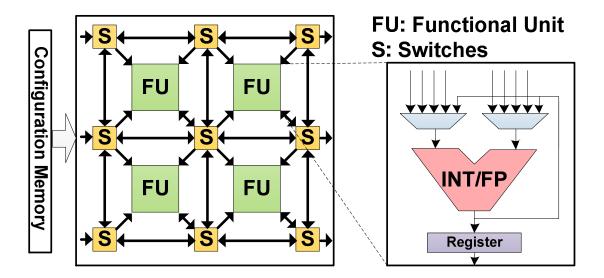

A large body of work has investigated reconfigurable hardware for exploiting spatial parallelism in applications [36]. Some systems employ coarse-grained functional units designed to implement dataflow graphs [35], [37]–[41], while others use finer-grained units or FPGA-like hardware [42]–[45]. Coarse-grain reconfigurable accelerators (CGRAs) are composed of a grid of function units (FUs), which are also called processing elements (PEs). FUs operate on word-sized data, and can perform arithmetic and logic operations. A reconfigurable interconnect provides the capability for inter-FU communication as well as communication into and out of the accelerator. A dataflow graph of a compute-intensive application kernel, containing nodes (operations) and edges (data communication), is mapped to the CGRA's FUs and interconnect either manually or using automated techniques [46].

CGRAs, such as those used in DySER [40] and SGMF [47], considerably improve performance and energy consumption compared to conventional processors by exploiting spatial data parallelism in application kernels and efficiently processing kernel's dataflow graphs [40], [43], [47]–[49]. In particular, CGRAs can practically eliminate the large energy overheads of fetching and scheduling instructions in conventional out-of-order processors. With recent advances in their compilers and architectures [50]–[54], CGRAs are gaining momentum in various applications and are integrated in several architectures [35], [37]–[41]. CGRAs improve the performance and energy-efficiency of many applications with high degrees of parallelism such as multimedia, signal processing, cryptography, scientific data analysis, face detection, voice recognition, and pattern matching [36], [55].

Compared to fine-grain reconfigurable accelerators (e.g., FPGAs), CGRAs are less flexible because of performing word-level operations (instead of working at a bit-level granularity). However, for the same reasons, CGRAs result in higher performance, lower energy consumption, and much smaller configuration data (which allows for a shorter configuration time) [49], [56]–[59].

Because this dissertation is not focused on the detailed low-level accelerator architecture, but rather its interaction with the rest of the system and the memory hierarchy in particular, we use an existing reconfigurable accelerator design rather than create a new one. We model a coarse-grained accelerator similar to the DySER architecture [40] with a heterogeneous grid of 32-bit functional units connected by a configurable routing fabric (Figure 3). Most functional units in this architecture can perform addition, subtraction, and a few logical operations, while a few functional units can perform complex operations such as multiplication. Like most CGRAs, the architecture also includes small local storage structures to keep intermediate data near the functional units that use them. This prevents CGRAs from polluting the cache (or memory) with data exhibiting low temporal locality that is only accessed once, and helps decrease energy consumption, particularly in streaming applications [4]. The processor triggers CGRA reconfiguration at runtime to implement different kernels at different times, overwriting configuration memory with the new dataflow graph's configuration data. This allows the CGRA to act as "virtual hardware" [3]. Configuration data for the various dataflow graphs can be retained in main memory until it is needed, and is often cached in configuration memory local to

Figure 3. A CGRA with a grid of 2×2 functional units.

the CGRA. At configuration time, The CGRA reads the configuration data from the configuration memory (or main memory) to reprogram its functional units and switches. Although the experiments presented in this work assume the accelerators are CGRAs, the proposed techniques would also apply to other highly-parallel accelerator structures.

#### 2.1.2 Interfaces between Reconfigurable Accelerators and Processors

This section briefly discusses different major architectural methods used to transfer data between a reconfigurable accelerator and the memory hierarchy in a heterogeneous system.

Local Buffer: In some cases, an accelerator is not integrated into the system's memory hierarchy; instead, a local buffer provides storage space for accelerator inputs and outputs, which are filled/fetched by the processor. The accelerator has no independent access to the processor data cache and main memory. The processor loads a batch of data into the accelerator's local buffer for the accelerator to consume. Once the accelerator finishes computation and writes its results back into the buffer, the processor copies those results to the memory hierarchy. The programmer must explicitly perform these data transfers. Many reconfigurable systems use this mechanism due to its architectural simplicity [60], [61].

**Shared-Memory Cache Hierarchy:** Instead of communicating through a separate local buffer, an accelerator may instead be integrated into a shared memory hierarchy [62], [63]. Direct access to the cache hierarchy helps accelerators load their required data on demand without any help from the processors.

There are several ways to organize the cache hierarchy for these architectures. The accelerator and processor may have private data caches, with shared input data loaded into each, increasing data duplication. The FARM prototype [64] coherently connects an FPGA board with private caches to two AMD boards through HyperTransport links. In the Many-cache memory

architecture [65], an FPGA-based accelerator uses multiple, multi-bank private caches; each cache targets a specific type of data or memory region.

Alternatively, one or more cache levels may be shared between the processor and accelerator. Sharing a data cache can greatly reduce communication traffic. For instance, a shared L2 cache was shown to provide higher performance and more energy-efficiency than a private L2 cache for applications with a great deal of interleaved software and hardware execution [5], [62]. Sharing the L1 could, however, improve performance of both accelerated and software-only execution if they share a working set that fits in the shared L1 cache.

In the Garp architecture [44], [45], an accelerator and a single processor share an L1 data cache. While the accelerator is active, it controls the memory hierarchy buses to load or store data from/to memory and has access to the same memory system as the processor. In the Tartan architecture [43], a special bus allows direct communication between a processor's register file and an accelerator, and they also share an L1 data cache. Choi *et al.* [66] investigates performance and area of multi-port caches in a system where a soft processor shares an L1 cache with several accelerators on an FPGA.

In this dissertation, we however investigate performance and energy efficiency of the cache hierarchy in a system where the whole system including the processor, caches, and coarse-grained accelerator is implemented using ASIC technology, thus having different requirements and characteristics.

#### 2.2 Caches

Accelerators process data at a higher rate and therefore issue more requests to memory per time unit compared to processors. Therefore, cache bandwidth is critical for the performance of accelerators that communicate through a system's cache hierarchy. This section briefly presents existing techniques to implement high-bandwidth caches and configurable caches that allow the cache design to be customized to application needs at runtime.

#### 2.2.1 High-Bandwidth Caches

High cache bandwidth is necessary in systems where accelerators are connected to the cache hierarchy, in order to supply accelerators with data at the increased rate required by their increased computation capabilities. There are several types of multi-port cache designs that increase cache bandwidth [67]–[69]:

- True (ideal) multi-porting: all N cache ports operate independently, and N different addresses can be accessed simultaneously each cycle. Because true multi-porting incurs high area/power/delay costs, this approach is not feasible for large caches. Each extra port adds transistors to the SRAM cells and enlarges auxiliary circuits such as decoders and input/output circuits. Hence, it increases cache area, energy per access, leakage power, and hit time. Yet, if high bandwidth is needed, the increase in dynamic and leakage power may be offset by shorter execution time and reduced overall energy.

- *Time division multiplexing (virtual multi-porting or multi-pumping)*: the cache runs *N* times faster than the processor, providing the appearance of *N* ports. This technique does not scale to large port counts because of clock speed limits.

- *Cache replication*: a single-port cache is replicated *N* times, providing *N* read ports, but one write port is broadcast to the replicated caches to maintain coherence. Thus, cache area increases linearly with the number of read ports. Stores are costly in terms of energy consumption due to the broadcast.

- Cache interleaving (multi-bank caches): the cache contents are split across N independently-addressed banks, allowing up to N simultaneous requests (at most one per bank). Requests to the same bank suffer from bank conflicts. Increasing the number of banks improves cache

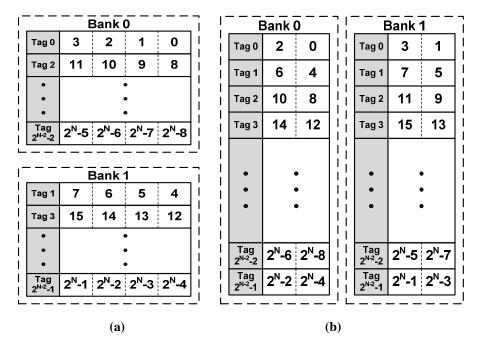

access parallelism and cache access time (smaller banks), but increases area and wire delay of the arbitration and bank interconnection circuitry. This increases cache area and delay, limiting the feasible number of banks. In banked multi-ported caches, data can be split across the banks in multiple ways. Among them are *line interleaving* and *word interleaving*. Line-interleaving partitions the address space across multiple banks using a cache line granularity (Figure 4a). In word-interleaved multi-bank caches, the words within a cache line are distributed across multiple banks (Figure 4b). Requests to sequential words in word-interleave banked caches are served by different banks, reducing bank conflicts (and thus increasing performance) for sequential accesses as compared to line-interleave caches. However, word-interleave caches require multi-port tags or replicated tags to serve parallel requests to the same cache line [68]. The line tag must be replicated as many times as the number of banks, or the tag array must have as many ports as the number of banks. For example, in Figure 4b, tags for Banks 0 and 1 are duplicates. Note that there could be more than two words per cache line depending on the number of words per cache line and the number of banks.

Figure 4. Interleaving schemes in dual-bank caches. (a) line interleaving (b) word interleaving.

#### **2.2.2** Configurable Cache Architectures

Configurable caches provide the opportunity to tune cache parameters based on the requirements of the executing application. Much research work has studied configurable caches. This section mainly focuses on studies that are fundamental to this research.

Selective-ways [70] is a reconfigurable method that provides the ability to vary the number of cache ways in a set associative cache. The key goal is to reduce the dynamic energy of the data array in a set associative L1 cache by reducing the number of active ways. This method provides a flexible tradeoff between performance and energy. When performance degradation is small or tolerable, a subset of ways can be disabled. When high performance is required for cache-intensive applications, more cache ways can be enabled. Frequent change to the number active ways may incur high performance and energy overheads. Therefore, the number of active ways changes only prior to application's execution at context switch time (i.e., process granularity). There are three approaches to handle data in a disabled way. That data can be (1) flushed, (2) only

accessible for coherence request, or (3) transferred to an enabled way. Frequent data flushing of disabled ways may impose substantial performance and energy overhead. The other approach is to make tag and data arrays of all ways accessible for coherence requests. Finally, data in a disabled way can be transferred to an enabled way when there is a hit to the disabled way by adding some logic to the cache datapath.

The *way-concatenation* method [71] provides the ability to vary the associativity of cache while still having the full cache capacity. By modifying the address decode logic, the method enables trading off fewer ways for more sets. The goal is to reduce the cache access energy by lowering associativity. The *V-way* method [72] provides the ability to vary the associativity of an L2 cache on a per-set basis. The method is based on the observation that applications do not have a uniform distribution of memory accesses across cache sets. This method reduces the miss rate by independently varying the associativity of sets based on the running application.

Selective-sets [73] provides the ability to vary the number of cache sets by enabling/disabling a subset of cache arrays. The goal is to reduce the energy consumption by resizing cache and power gating the disabled arrays [74]. Since resizing changes the cache look-up function (*i.e.*, set-mapping for cache lines), this method requires to store all the tags bits for the smallest possible cache size which impose area overheads. Moreover, dirty cache lines of disabled arrays should be written back to the lower level cache and all lines (clean or dirty) in cache arrays in which their set-mappings change after enabling the cache arrays should be flushed.

The hybrid *selective-sets-and-ways* method [75] combines both selective-ways and selective-sets to provide higher energy efficiency by allowing a wider range of possible cache sizes. Both selective-ways and selective-sets exploit the cache subarray technique in which a cache is divided into multiple subarrays to reduce both cache access latency and operation energy. This hybrid

method uses the subarray techniques to better match the required number of sets and ways to the application requirements for energy efficiency.

Ranganathan *et al.* [76] propose a reconfigurable cache technique to use unnecessary cache sub-arrays for different processor activities. The motivation is that some workloads do not use large caches and therefore parts of a cache (unnecessary cache sub-arrays) can be devoted to other activities such as lookup tables and prefetched data storage.

Some studies such as *MorphCache* [77] and *configurable cache hierarchy* [78] attempt to reconfigure a multi-level cache topology in a multiprocessor system. The motivation is that a fixed cache topology does not provide an optimal performance for all workload combinations running on multiple cores. Some other studies such as *Amoeba-Cache* [79] and *configurable line size* [80] vary the cache line size to improve performance and energy efficiency based on the application requirements.

### 2.3 Memory

This section provides of an overview of commodity memory systems and discusses previous processor-in-memory proposals.

## 2.3.1 Dynamic Random-Access Memory (DRAM)

DRAM devices are generally used as main memory in many different systems from smartphones to servers. Each bit of data is stored in a memory cell that contains only a capacitor and a transistor, allowing DRAM devices to have much higher densities than SRAM, which usually use six transistors per bit. Due to the gradual electrical charge leakage, DRAM cells are periodically refreshed with a constant time interval (usually 64ms) to guarantee data integrity.

The main memory system is comprised of one or multiple memory channels that work independently. Each memory channel has one or multiple Dual Inline Memory Modules

(DIMMs), which are circuit boards that hold a number of DRAM devices. DRAM devices in a DIMM can be grouped into ranks. All DRAM devices in a given rank work together in lockstep to provide data; thus all devices in a rank collectively service the same memory request. Each DRAM device is made up of multiple banks (each composed of arrays of memory cells, a row buffer, and row and column decoders) that can be accessed independently. DRAM devices allow concurrent bank operations to improve bandwidth. The most recently accessed row of each bank is stored in its associated row buffer. Only a subset of a row (called a column) is accessed in each memory transaction. Address bits determine the appropriate channel and rank in the main memory, the bank within the rank, and row and column in the bank. Command bits indicate the operation the device should perform. The Activate command brings an entire row of data from a particular bank in the DRAM arrays into the bank row buffer and activate (open) the row buffer. The Read command reads a column of data from the row buffer and places the data in the data I/O bus. Likewise, The Write command writes a column of data from the data I/O bus into the row buffer. The *Precharge* command restores data from the row buffer into DRAM cells and deactivates (close) the row buffer. The Refresh command activates and restores (precharges) a specific row in all banks [81].

## 2.3.2 Processor-in-Memory (PIM) Systems

Processor-in-memory (PIM) technology merges logic devices and memory cells onto the same silicon die to process data in memory. This improves performance by exploiting higher memory bandwidth and increases energy efficiency by exploiting local data processing. The PIM systems address the "memory wall" problem through faster processor-memory accesses and can benefit from lower memory access latency and significantly higher memory bandwidth compared to conventional systems, thereby enabling high-performance data processing. Moreover, in a conventional system, data is often moved from off-chip memory through on-chip devices (buses,

levels of cache, and register file) before it is processed. A PIM-based system eliminates much of this data movement by operating on data within the PIM chip, thereby localizing computations. This reduces the distance between where data is stored and where it is processed, leading to substantial energy saving.

Since conventional processors are not particularly designed to take advantage of high-memory bandwidth, processing units in PIM systems are usually specialized units such as vector processors or simple reconfigurable units. Also, generally several or many of these processing units operate in parallel to access memory concurrently (therefore increasing aggregate memory bandwidth). Integrating processing units with memory components can provide a way for high-performance and energy-efficient processing of data-intensive applications. This large and growing class of applications (such as biomedical applications) processes huge amounts of data and can often be implemented using a data-parallel approach well-suited to PIM systems.

There have been several efforts to unify processor logic and DRAM onto a single chip, including proposals for architectures, prototypes, and programming models as well as application case studies [11]–[22]. We briefly provide a summary of PIM architectures. The *Computational RAM* architecture [13], [14] unifies memory and logic by connecting SIMD processing elements to DRAM sense amplifiers through a wide bus. Similarly, the *Intelligent RAM* architecture [21] combines a vector processor and DRAM memory on a chip to enable fast data-parallel operations through wide memory interface [18]. The *FlexRAM* memory chip [16], which replaces a conventional memory chip, comprises a processor and a large number of simple compute engines that are interleaved with DRAM blocks. FlexRAM chip are connected for inter-chip communication. The processor runs the serial code and controls the execution flow, while simple compute engines process bulk of data in their local memory blocks [82]. The *Smart Memories* architecture [19], [83] is a tiled architecture composed of many processing units, caches, and

DRAM blocks in a same chip. The processing units, memory units, and interconnection units are reconfigurable to some degree. Thus, the programmer can program all these units to better support applications with different data structures and programming models. In *Data IntensiVe Architecture (DIVA)* [12], [15], processor-in-memory chips are composed of one or multiple tiles which each contains a processor and DRAM cells. The processor-in-memory chips are connected through a separate interconnect for inter-chip data communication. The *Active Pages* model [20] integrates many small pages of data and their associated functional units in a single chip. Data pages and functional units are implemented on DRAM and fine-grained reconfigurable fabric, respectively. Functional units operate only on data stored in their local data page. Inter-page communication is performed through the host processor. The recent *TCAM* [84] and *AC-DIMM* [85] proposals enable in-memory associative computing using PCM and STT-MRAM technologies.

Memory and logic technologies in PIM systems have different characteristics. Logic is optimized for performance, while memory (DRAM process) is optimized for capacity with fewer layers of metal to decrease manufacturing cost and improve yield. PIM systems overhaul the DRAM architecture to efficiently integrate processing units in memory devices, making their designs and verification challenging and time-consuming. Moreover, PIM systems suffer from high manufacturing costs and low yield because of integrating two different technologies (e.g., having additional metal layers compared to memory devices) [24], [25].

There are some proposals for processing data in the memory controller. These proposals reduce data movement through the cache hierarchy by adding specialized hardware to the memory controller. Yoo *et al.* [86] propose a near-memory processing architecture for a many-core system composed of 36 processor and memory tiles. To reduce the latency of memory operations, memory tiles are tightly coupled with special-purpose processors called *active*

memory processors (AMPs). This architecture enables offloading data-intensive operations to AMPs such that AMPs replace memory transactions over the on-chip network and computations on processor tiles. Some researchers have proposed adding specialized hardware to the memory controller for data processing. Ahn et al. [87] dedicate hardware to enable parallel execution of a specific class of atomic operations in the memory controller for data-parallel architectures. Wei et al. [88] propose augmenting the memory controller with a co-processor for vector, streaming, and bit manipulation operations. Fang et al. [89] propose an active memory controller (AMC) in which scalar and stream operations are performed in the memory controller. The goal is to reduce the latency of operation on data with low temporal locality and minimize memory traffic in a distributed shared-memory system. The AMC contains a hardware unit to perform pre-defined scalar and stream operations which are issued by the processor. In general, memory controllers augmented with processing hardware engines still suffer from high off-chip data energy and limited applicability due to supporting a limited class of applications.

Recently, there have been proposals to bond DRAM layers with application-specific accelerators [32] and GPGPU execution units [31]. The Hybrid Memory Cube (HMC) [90] and 3D-stacking memory and processors [91], [92] promise high memory bandwidth and new opportunities for local data processing. The HMC integrates 4 or 8 3D-stacked memory dies and a logic die on a package. The logic layer implements a memory controller and has a new interface to interface to the processor. The HMC packetizes memory accesses and exploits high-speed serial links. Even if our proposal can be exercised in an HMC-like structure or 3D-stacked memory by embodying the processing units in the logic layer, we take a different approach by processing data *near conventional and commodity DRAM devices* to make impact in the near future. Our approach is completely achievable using the present-day 3D-stacking technology and

does not require significant modifications to memory device design or their interface to the processor, making it compatible with commodity DRAM devices.

# 3 Experimental Framework

In this dissertation, we propose techniques to improve energy-efficiency of processor-accelerator architectures where the accelerators communicate through the cache hierarchy. We also propose a near-memory processing architecture that uses commodity DRAM devices and reconfigurable accelerators. To evaluate our proposed architectures, we use a combination of cycle-accurate simulation and power modeling over different benchmarks. In this chapter, we present the performance simulation infrastructure and power modeling tools that we have used in this research. We also describe our methodology to develop workloads for performance evaluation of our proposed architectures.

#### 3.1 Performance Simulation Infrastructure