#### **OPTIMIZING LOW-POWER SETTINGS IN COMPUTER SYSTEMS**

by

#### Yanpei Liu

A dissertation submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

(Electrical and Computer Engineering)

at the

UNIVERSITY OF WISCONSIN-MADISON

2016

Date of final oral examination: 10/10/16

The dissertation is approved by the following members of the Final Oral Committee:

Professor Yu-Hen Hu, University of Wisconsin Madison, Chair

Professor Ricardo Bianchini, Microsoft Research & Rutgers University

Professor Mikko Lipasti, University of Wisconsin Madison

Professor Parameswaran Ramanathan, University of Wisconsin Madison

Professor Jin-Yi Cai, University of Wisconsin Madison

© Copyright by Yanpei Liu 2016 All Rights Reserved To my grandfather

Zhuangqing Hu

who brought me to the door of engineering

### Acknowledgments

In the past a few years as a PhD student, I had the great fortune to work with some amazing people across several research institutions. On top of the list is Professor Stark Draper, my adviser who first brought me into UW-Madison's graduate program. As a student I learned a lot from his technical wisdom. As a working professional his incredible mentorship have had a long-lasting impact on my career.

I would like to thank Professor Ricardo Bianchini from Rutgers University who advised and helped me during the last a few tough PhD years. I vividly remember all the discussions we had, all the joys and frustrations we shared and all the hard work we put in together. I never forget those late night discussions in the DARK Lab (as well as the 2-hour drive back to Middle Village, NY). Countless times I emailed him about our work falling short, frustrated with the results, but almost always left motivated after reading the replies.

This thesis would not even start without Daniel Myers and Emina Soljanin. Daniel, who was then the instructor of CS 547, inspired my curiosity in queuing theory and laid down the necessary foundation for my research. The work with Emina on fork-join queue shaped my research direction even further and eventually led to the participation in the Special Focus on Energy and Algorithms at DIMACS.

My thanks go to my collaborators, Guilherme Cox and Qingyuan Deng for their tremendous contribution towards FastCap and FastEnergy, Gauri Joshi for working on fork-join queues together, Professor Nam Sung Kim for guiding me towards my first paper in ISCA, Jing Yang for demonstrating the backpressure algorithm and Professor Akbar Sayeed for co-advising my first ever academic publication.

This thesis would not end without my thesis committee members, Professor Yu-Hen Hu, Mikko Lipasti, Parameswaran Ramanathan and Jin-Yi Cai. I would like to thank especially Professor Yu-Hen Hu for the generous help in guiding me towards final defense since late 2014.

Finally, I would like to thank my all family and friends, for their undivided support on my determination to chase the dreams.

# **Contents**

| Co | onten   | ts      |                                | iv   |

|----|---------|---------|--------------------------------|------|

| Li | st of   | Tables  |                                | vii  |

| Li | st of l | Figures |                                | viii |

| Al | bstrac  | et      |                                | xi   |

| 1  | Intr    | oductic | on                             | 1    |

|    | 1.1     | Contr   | ribution                       | 4    |

|    |         | 1.1.1   | Problem statement and overview | 4    |

|    |         | 1.1.2   | SleepScale                     | 6    |

|    |         | 1.1.3   | FastCap                        | 7    |

|    |         | 1.1.4   | FastEnergy                     | 8    |

|    | 1.2     | Thesis  | s structure                    | 9    |

| 2  | Bacl    | kgroun  | ad                             | 10   |

|    | 2.1     | Serve   | r power consumption            | 10   |

|    | 2.2     | Low-p   | power settings                 | 11   |

|    |         | 2.2.1   | CPU                            | 11   |

|    |         | 2.2.2   | Memory                         |      |

|    | 2.3     | Perfor  | rmance metrics                 | 14   |

| 3  | Slee    | pScale  |                                | 16   |

|    |         | _       | Auction                        | 16   |

|   | 3.2  | Systen | n model                          | 18 |

|---|------|--------|----------------------------------|----|

|   | 3.3  | Workl  | oad-dependent Optimal Policy     | 22 |

|   |      | 3.3.1  | Methodology                      | 22 |

|   |      | 3.3.2  | Engineering lessons              | 23 |

|   |      | 3.3.3  | Analytic results                 | 30 |

|   | 3.4  | SleepS | Scale design                     | 31 |

|   |      | 3.4.1  | Policy manager                   | 31 |

|   |      | 3.4.2  | Runtime predictor                | 37 |

|   | 3.5  | Result | ts                               | 42 |

|   |      | 3.5.1  | Under real-world utilization     | 43 |

|   |      | 3.5.2  | Distribution of low-power states | 47 |

|   | 3.6  | Concl  | usion                            | 48 |

| 4 | Fast | Cap    |                                  | 49 |

|   | 4.1  | Introd | luction                          | 49 |

|   | 4.2  | FastCa | ap Design                        | 52 |

|   |      | 4.2.1  | System model                     | 52 |

|   |      | 4.2.2  | Optimization and algorithm       | 58 |

|   |      | 4.2.3  | Implementation                   | 61 |

|   |      | 4.2.4  | Hardware and software costs      | 63 |

|   | 4.3  | Evalua | ation                            | 64 |

|   |      | 4.3.1  | Methodology                      | 64 |

|   |      | 4.3.2  | Results                          | 68 |

|   | 4.4  | Concl  | usion                            | 80 |

| 5 | Fast | Energy |                                  | 82 |

|   | 5.1  | Introd | luction                          | 82 |

|   | 5.2  | FastEr | nergy Design                     | 84 |

|   |      | 5.2.1  | Optimization and algorithm       | 84 |

|   |      | 5.2.2  | Implementation                   | 86 |

|   | 5.3  | Evalua | ation                            | 90 |

|     | 5.4 Conclusions                                                                | 98         |

|-----|--------------------------------------------------------------------------------|------------|

| 6   | Related work                                                                   | 100        |

| 7   | Conclusion and Future Work 7.1 Future Work                                     | 105<br>107 |

| A   | Derivation of closed-form $\mathbb{E}[R]$ and $\mathbb{E}[P]$ in Section 3.3.3 | 109        |

| В   | Proof of Theorem 4.1                                                           | 111        |

| C   | Proof of Theorem 5.1 and Theorem 5.2                                           | 112        |

| Bil | oliography                                                                     | 115        |

# **List of Tables**

| 3.1 | CPU low-power settings [1]                                      | 17 |

|-----|-----------------------------------------------------------------|----|

| 3.2 | Platform low-power settings [2]                                 | 17 |

| 3.3 | Power consumption for different components in a computer system | 18 |

| 3.4 | Wake-up latencies for different states [3, 4]                   | 20 |

| 3.5 | Different workload types from [5] (partial list)                | 34 |

| 4.1 | Workload descriptions                                           | 64 |

| 4.2 | Main system settings                                            | 66 |

# **List of Figures**

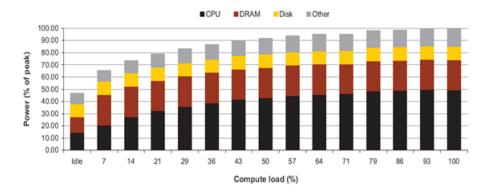

| 2.1 | Server power breakdown. Figure drawn from [6]                                      | 11 |

|-----|------------------------------------------------------------------------------------|----|

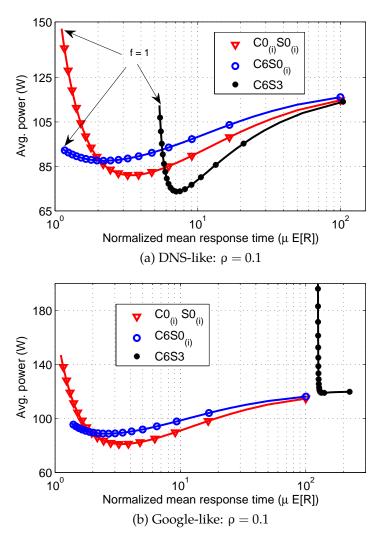

| 3.1 | Mean response time $\mathbb{E}[R]$ and average power $\mathbb{E}[P]$ trade-off     | 24 |

| 3.2 | Optimal low-power states for Google and DNS-like workload under                    |    |

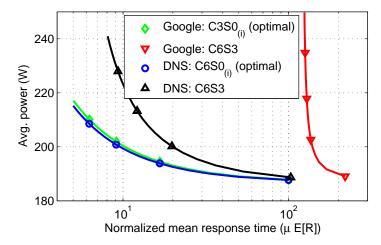

|     | high utilization                                                                   | 27 |

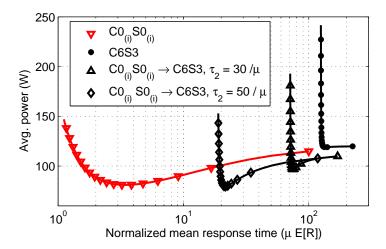

| 3.3 | Entering the second low-power state after delays for Google-like workload.         | 29 |

| 3.4 | Comparison between different CPU usages for DNS-like workload                      | 30 |

| 3.5 | Average power/performance trade-off for Google-like workload                       | 33 |

| 3.6 | Policy selection for DNS and Google-like workloads. Each curve plots the           |    |

|     | optimal pairing of frequency setting and low-power states as a function            |    |

|     | of utilization $\rho$ , and parameterized by QoS constraint $\rho_p$ . The differ- |    |

|     | ent markers (see legend) indicate which low-power state is optimal at              |    |

|     | each utilization. The solid lines represent what an idealized model com-           |    |

|     | putes and dashed lines represent the results using real-world workload             |    |

|     | statistics                                                                         | 34 |

| 3.7 | Utilization traces plotted across 3 days for different services. Both start        |    |

|     | at 12 AM of a day. Email store is the host for student, faculty and staff          |    |

|     | email storage. File server is the host for student files [7, 8]                    | 40 |

| 3.8 | Average response time under different predictors and policy update                 |    |

|     | intervals. No over-provisioning is used (i.e., $\alpha = 0$ )                      | 43 |

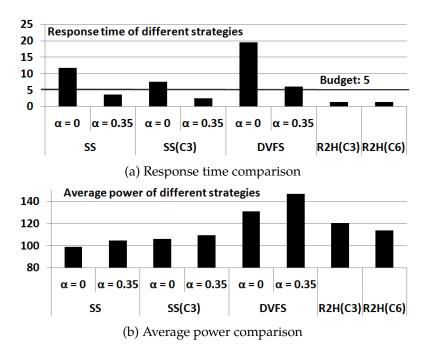

| 3.9 | Comparing SleepScale with other power control strategies. All strategies           |    |

|     | are running with LMS+CUSUM predictor with $p = 10$ and are updated                 |    |

|     | every $T = 5$ minutes                                                              | 46 |

|     | •                                                                                  |    |

| 3.10 | Distribution of optimal low-power states selected by SleepScale. LMS+CUSI predictor is used with history length $p=10$ , update interval $T=5$ and | UM |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | over-provisioning $\alpha = 0.35$                                                                                                                  | 47 |

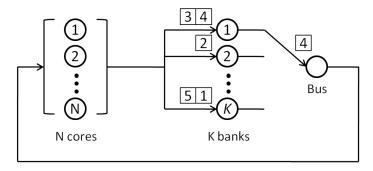

| 4.1  | FastCap's queuing model and the "transfer blocking" property. Memory bank 1 receives requests from cores 4 and 3. The requested data for core      |    |

|      | 4 has been fetched and is being transferred on the memory bus. At the                                                                              |    |

|      | same time, bank 1 is blocked from processing the request from core 3                                                                               |    |

| 4.0  | until the last request is successfully transferred to core 4                                                                                       | 53 |

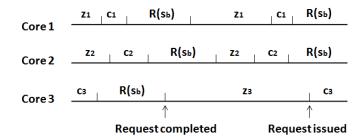

| 4.2  | An example workload dynamics with $N=3$ cores. Variables $z_i$ and $c_i$ are the                                                                   |    |

|      | think time and cache time for core i, respectively. $R(s_b)$ is the response time of                                                               |    |

|      | the memory. $z_i$ , $c_i$ and $R(s_b)$ are all average values. The sum $R(s_b) + c_i + z_i$ is                                                     | E  |

| 4.2  | the total time for one memory access of core i                                                                                                     | 55 |

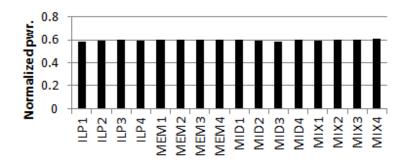

| 4.3  | FastCap average power consumption normalized to the peak power.                                                                                    | 68 |

| 4.4  | Power budget is 60% of the peak                                                                                                                    | OC |

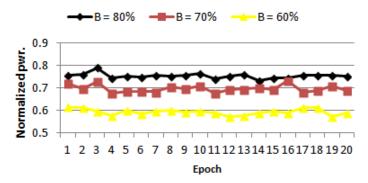

| 4.4  | Normalized average power draw when running MEM3, as a function of time                                                                             | 69 |

| 4.5  | and power budget.                                                                                                                                  | 09 |

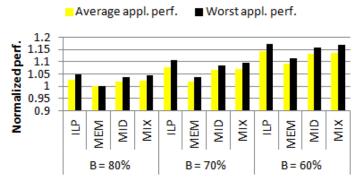

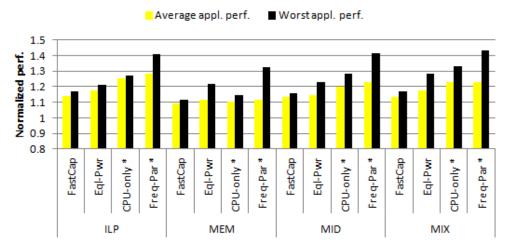

| 4.3  | Average and worst application performance for each workload class and three power budgets                                                          | 69 |

| 4.6  | •                                                                                                                                                  | 05 |

| 4.0  | FastCap compared with CPU-only*, Freq-Par* and Eql-Pwr in normalized average/worst application performance. "*" indicates fixed memory frequency.  |    |

|      | Power budget = 60%                                                                                                                                 | 72 |

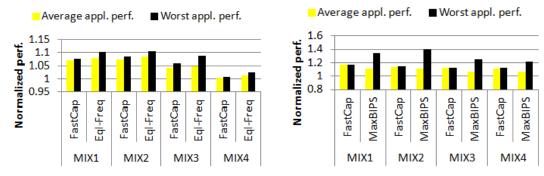

| 4.7  | FastCap compared with EqlFreq and maxBIPS.                                                                                                         | 75 |

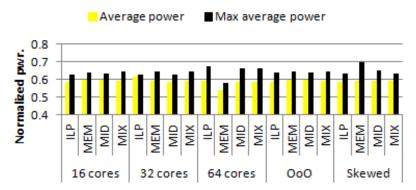

| 4.8  | Normalized FastCap average power and maximum average power in many                                                                                 | 70 |

| 1.0  | configurations. Power budget = 60%                                                                                                                 | 77 |

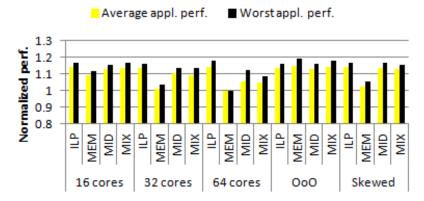

| 4 9  | Normalized FastCap average and worst application performance in many con-                                                                          | ,, |

| 1.7  | figurations. Power budget = 60%                                                                                                                    | 77 |

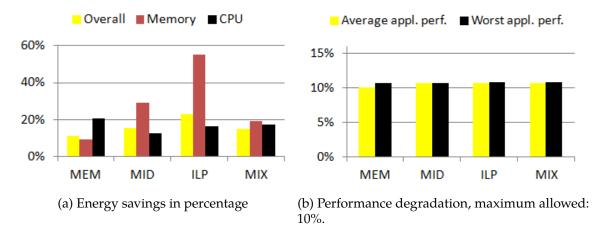

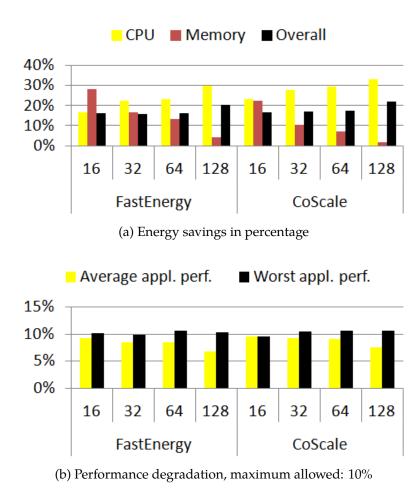

| 5.1  | FastEnergy energy and performance on $N = 16$ cores                                                                                                | 90 |

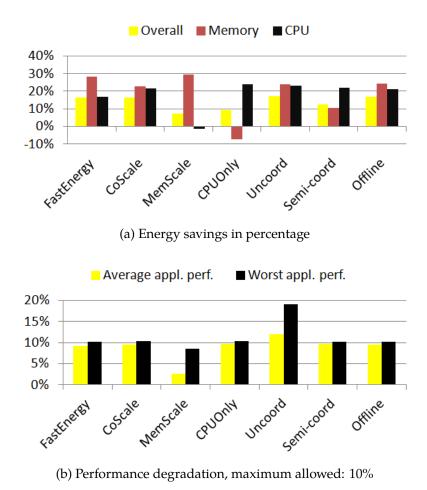

| 5.2  | FastEnergy compared with other methods, $N = 16$                                                                                                   | 93 |

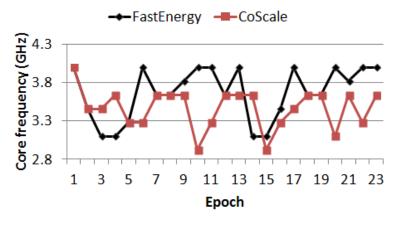

| 5.3  | Frequencies selected while running MIX2. The core frequency plots the                                                                              |    |

|      | core that runs application applu.                                                                                                                  | 94 |

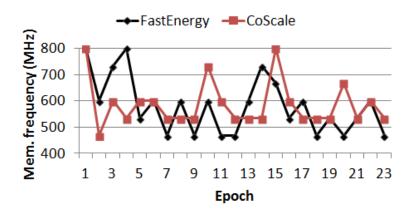

| 5.4 | FastEnergy and CoScale with $N = 16, 32, 64$ and $128$ | 95 |

|-----|--------------------------------------------------------|----|

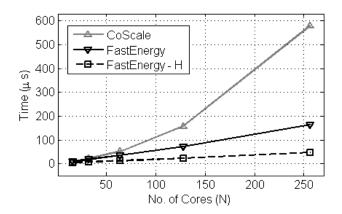

| 5.5 | Algorithm overhead, as a function of core counts N     | 97 |

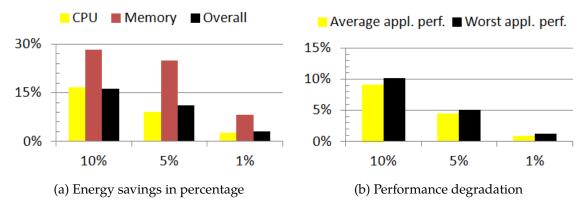

| 5.6 | FastEnergy for different performance bounds, $N = 16$  | 98 |

#### **Abstract**

Power and energy efficiency in computer systems has received growing attention in recent years. Striving for the balance between performance and efficiency, low-power settings in CPU, memory and other components are continuously adjusted under changing workload. It is important to adjust these settings in a coordinated manner as a lack of coordination hampers a system's ability to optimize for performance and efficiency. However over the years the number of low-power settings in a typical computer system has increased dramatically. This creates a combinatorial search space, and thus a challenging task, for optimizing the low-power settings at runtime.

In this thesis, via queuing models and performance analyses, we present three optimization techniques for managing low-power settings in modern computer systems. The first technique, SleepScale, jointly operates the active low-power modes and idle low-power states in modern CPU. The second technique, FastCap, maximizes the performance of applications under a full-system power cap while promoting fairness across applications. The third technique, FastEnergy, maximizes the full-system energy savings under pre-defined application performance loss bounds. All three techniques are developed based on novel queuing models for managing abundant low-power settings in many-core systems.

## Chapter 1

#### Introduction

As the workloads allocated to data center servers increase so does the economic and environmental footprint of these servers. By the end of 2013, U.S. data centers electricity usage has exceeded 90 billion killowatt-hours (or 9 billion U.S. dollars) and is expected to increase by 47% in 2020. Further, the carbon dioxide emission due to the electricity consumed by data centers has exceeded 90 million metric tons in 2013 [9]. These numbers give material economic, societal, and environmental reasons for improving the computation efficiency.

Much power/energy consumed by servers does not go toward computation. While configured to meet service demand, servers regularly operate at lighter load levels. Even in idle a server continues to draw roughly 60% of the maximum power when running full speed [1, 10]. Although some data centers (e.g. in Google) recently report low power usage effective (PUE), benefiting from the cooling using cold water directly from rivers or seas, around 40% of costs are still associated with power consumption in other commercial and governmental data centers [11].

To maximize power/energy efficiency, servers have incorporated an increasing number of idle low-power states (such as CPU sleep states) and active low-power modes (such as CPU dynamic voltage and frequency scaling, or DVFS). While active low-power modes offer flexibility in balancing performance and efficiency during normal execution, idle low-power states allow systems to conserve power during idle period. These low-power settings are also integrated in other system components such as main memory [12, 13], disk drives [14, 15] and interconnects [16].

Both active low-power modes and idle low-power states are well-studied in recent literature [17, 18, 19, 3, 20, 21]. George and Harrison [22] studied how to define the service rates that minimize a general cost function (combining waiting and service costs) in a single-server queuing system. Bansal *et al.* [23] studied minimizing energy via speed scaling without violating task deadlines. Past work [24, 25, 26] has shown that memory active low-power modes are particularly useful for workloads when the memory bus is underutilized for long periods. On idle low-power states, in [3] the authors proposed a method for eliminating idle power in servers by quickly transitioning between a high-performance active mode and a single idle low-power state. In [8] the authors warned of potential problems of using these low-power states and suggest "guarded" mechanisms to avoid negative power savings. The use of different idle low-power states for memory has also been extensively studied in [20, 21]. In Chapter 6 we provide a complete literature survey related to this thesis.

However, as these low-power settings grow in numbers, it is important to man-

age them in a coordinated manner as operating in separation can hamper a system's ability to optimize for performance and efficiency. To see an example of such behavior, consider a scenario in which our goal is to maximize the full-system energy savings within a pre-selected bound on the acceptable application performance loss. Further, suppose that the CPU cores are stalled waiting for the memory a significant fraction of the time. In this situation, the CPU power manager might predict that lowering voltage/frequency will improve energy efficiency while still keeping performance within the bound and effect the change. The lower core frequency would reduce traffic to the memory subsystem, which in turn could cause its (independent) power manager to lower the memory frequency. After this latter frequency change, the performance of the server as a whole may dip below the CPU power manager's projections, potentially violating the target performance bound. So, at its next opportunity, the CPU manager might start increasing the core frequency, inducing a similar response from the memory subsystem manager. Such interactions between CPU and memory frequencies cause performance oscillations. These unintended behaviors suggest that it is essential to coordinate power-performance management techniques across system components to ensure that the system is balanced to yield maximal energy savings.

The need for coordinated management creates a combinatorial search space for all low-power setting configurations. In a typical 16-core server with 10 active low-power modes for each core, the total number of possible low-power mode combinations is  $10^{16}$  – traversing this large space in search for the optimal configuration is difficult. Existing works often rely on some simplified exhaustive search [27] or

sub-optimal heuristics [28, 13] which may not perform well for future many-core servers.

We now summarize the challenges in effectively optimizing low-power settings. First, it is important to understand the complex interaction between different low-power settings in system components. Adjusting them in isolation may cause unpredictable performance and/or efficiency losses. Second, since the number of low-power setting combinations can be large, selecting the best low-power settings should be done with low overhead while still achieving optimal or near optimal solution. Third, the best low-power setting should adapt to workload at runtime. This challenge is especially acute for servers that run many applications in parallel (each with a potentially different behavior), since it is unlikely that the power mode selected for a core running one application can be used for a core running another one.

In the next section we summarize how our work address these challenges.

### 1.1 Contribution

#### 1.1.1 Problem statement and overview

In this dissertation, we tackle the problem of optimizing low-power settings in computer systems for power/energy efficiency and application performance. We abstract system operations using queuing models. The queuing models allow us to quantitatively characterize the workload behavior under different low-power settings. For a given set of workloads, the goal is to develop effective algorithms

which adjust the low-power settings at runtime to achieve the best power/energy efficiency under performance constraints (or vice versa). In particular, we focus on three specific problems:

- a) Management of active low-power modes and idle low-power states in processors to maximize efficiency under performance constraints.

- b) Management of active low-power modes in both processors and memory to maximize performance under a given power cap.

- c) Management of active low-power modes in both processors and memory to maximize energy efficiency under performance constraints.

We present three methods, namely SleepScale, FastCap and FastEnergy to tackle these three problems. For problem a), we develop a novel queuing simulator in SleepScale to select the best low-power settings at runtime. The queuing simulator allows us to identify the optimal pair of active low-power mode and idle low-power state for the best efficiency/performance. For problem b), we develop a novel many-core queuing model and formulate a convex optimization problem. We deduce the FastCap algorithm – the fastest algorithm among the state-of-the-arts which produces the best application performance under a given power budget. For problem c), we further extend the many-core queuing model and formulate a non-convex optimization problem. We deduce the FastEnergy algorithm which, when compared with the state-of-the-arts, produces the same level of energy efficiency and application performance at lowest algorithmic complexity.

The models used in SleepScale, FastCap and FastEnergy are different. FastCap and FastEnergy consider active low-power modes in both processors and memory. The queuing models developed capture workload characteristics at a fine-grained micro-architectural level. SleepScale consider active low-power modes and idle low-power states in processors. The queuing model developed captures workload characteristics at a system/server level. In Chapter 7.1 we further discuss how the models can be extended for other use cases.

We now discuss the aforementioned contributions in details.

#### 1.1.2 SleepScale

Our first contribution, SleepScale, solves the problem of optimizing active low-power modes and idle low-power states in processors. SleepScale challenges the conventional wisdom that active low-power modes and idle low-power states can be operated independently. It also challenges the idea of always using fixed active and idle low-power settings as suggested by many prior literature. SleepScale suggests that the optimal choice of the active low-power modes and idle low-power states depends on workload and hardware characteristics, and should be adjusted at runtime in response to workload changes.

To understand the interaction between active low-power modes and idle low-power states, we first build a queuing simulator to model job executions in different DVFS and sleep state settings. Through extensive simulation, we verify that different DVFS choices should be used together with different sleep states. We show that the conventional "race-to-halt" method [3], which runs the CPU at the maximum

speed when busy and uses a fixed sleep state when idle is a suboptimal choice. To construct low overhead algorithms and operate at runtime, SleepScale uses a workload predictor to predict the workload statistics online. Then the policy manager uses the predicted statistics to determine the best DVFS and sleep state setting by running the aforementioned light-weight queuing simulator. We design SleepScale to run in epochs and our results show that SleepScale offers significant power savings over some conventional methods while respecting the same QoS constraints.

#### 1.1.3 FastCap

Our second contribution, FastCap, solves the problem of optimizing active low-power modes in processors and memory under a given power budget. FastCap challenges the current solutions which operate low-power settings in processors and memory independently. By optimizing jointly for processors and memory, FastCap significantly advances the state-of-the-arts in both algorithm complexity and application performance.

To understand the interaction in low-power settings between processors and memory, we first develop a queuing model that effectively captures the workload dynamics in a many-core system. Based on the queuing model, we formulate a convex optimization framework for maximizing application performance under a given power budget. To construct low overhead algorithm, we make a key observation that core frequencies can be determined optimally in linear time for a given memory frequency. We develop the FastCap algorithm and implement it to

operate at runtime. The operating system runs the algorithm periodically (once per time quantum, by default), and feeds a few performance counters as inputs to it. Our results show that FastCap maintains overall system power under budget and produces the best application performance among the state-of-the-art methods.

#### 1.1.4 FastEnergy

Our third contribution, FastEnergy, solves the problem of optimizing active low-power modes in cores and memory for energy conservation. FastEnergy adopts the same queuing model developed in FastCap. Based on the queuing model, the FastEnergy algorithm has the lowest complexity among the state-of-the-arts while achieving the same level of energy efficiency. The work of FastEnergy further demonstrates the applicability of the queuing models for managing abundant active low-power modes in many-core systems.

To understand the interaction in low-power settings between processors and memory, we formulate a non-convex optimization framework for minimizing the full-system energy under application performance constraints. As in FastCap, we observe that core frequencies can be determined optimally in linear time for a given memory frequency. This observation allows us to develop a low overhead algorithm to operate at runtime. Our results show that FastEnergy produces significant energy savings across a range of core counts, especially when users are willing to accept greater performance degradation. In addition, our results show that FastEnergy consistently scales to larger core counts than the state-of-the-art design.

# 1.2 Thesis structure

The rest of the thesis is organized as follows. In Chapter 2 we provide an overview of system low-power settings and introduce key performance metrics. In Chapter 3, Chapter 4 and Chapter 5 we introduce SleepScale, FastCap and FastEnergy respectively. The discussion of related work is in Chapter 6 and we conclude the thesis in Chapter 7.

# **Chapter 2**

# **Background**

### 2.1 Server power consumption

Data centers spend a large amount of capital on power usage and other associated infrastructures. Around 40% of total operation cost is related to power distribution, cooling and electricity bills [11]. In data centers, most power is consumed by servers themselves – the server power consumption is around 47% of total power distributed to data centers [29].

Within each server, power is further distributed to system components such as CPU, memory and disks. Figure 2.1, excerpted from [6], shows the power breakdown in different components in Google's  $\times 86$  production servers running at different utilization levels. As shown in Figure 2.1, power spent in CPU and memory account for more than 60% of total power draw.

We now describe different power saving techniques (i.e., low-power settings) commonly implemented in modern computer systems.

Figure 2.1: Server power breakdown. Figure drawn from [6].

### 2.2 Low-power settings

In this thesis, we focus on two types of low-power settings: active low-power modes and idle low-power states. Active low-power modes are power saving methods used when a device is in normal operating state. Idle low-power states are the ones used when a device is in idle.

#### 2.2.1 CPU

Active low-power modes. In modern processors, active low-power modes are provided via the dynamic voltage and frequency scaling (DVFS) during normal processor operation. DVFS adjusts the frequency and voltage on-the-fly to conserve power and prevent processors from overheating. In DVFS, voltage is typically adjusted together with the frequency to provide desired trade-off between performance and power. In advanced configuration and power interface (ACPI) specifications, DVFS settings are also referred to as P-states. Different P-states correspond to different DVFS levels and all P-states are referred to as the C0 operating state [2]. Some

industrial implementations include Intel's SpeedStep [30] and AMD's Cool'n'Quite [31]. When frequency is changed, the speed at which the processor executes instructions is also changed accordingly. Maximum frequency provides fastest instruction execution at the cost of highest power consumption. While for workload that is not as CPU intensive, setting the frequency low can be beneficial for power savings.

In active low-power modes, the total power of the CPU is the sum of the dynamic and static power. The dynamic power depends on the frequency and voltage of the CPU. Approximately, it can be expressed as CV²f [32], where V and f are the operating voltage and frequency of the CPU. The parameter C is some scaling factor which relates to the capacitance. In DVFS, the voltage V is changed together with the frequency thus the CPU dynamic power scales cubically with the frequency. The static power consists of all power components that do not depend on either voltage and frequency. It is mainly due to various leakage currents. It is also possible to adjust the frequency only while the voltage is held constant (thus DFS) or to adjust the voltage only with constant frequency (thus DVS). However they are not used as widely as DVFS due to their subpar efficiency for achieving the same level of performance.

**Idle low-power states.** Besides the C0 operating mode, ACPI also specifies a series of idle low-power states such as C1/C1E, C2, C3 and C6 states. These states are applied when the processor is not executing instructions. In C1/C1E state, the frequency/voltage are reduced to the minimum and it is often used when the processor just stops executing instructions. Transition to C0 state from C1/C1E can happen almost instantaneously with little wake-up latency. Under longer idle

period, the processor can enter C2 or C3 state with more power savings but at the cost of higher wake-up latencies. In C2 state, the clock is stopped and in C3 state, the private cache is also flushed. Some processors even have very deep idle low-power states such as C6 state [30]. In such state, the architectural information is saved to RAM and voltage is set to zero. The power consumption in C6 state is very low but the wake-up latency is often quite high. The number of idle low-power states has been growing as new modern processors are manufactured; the recent Intel's Haswell platform has up to C10 state [33].

The power consumption in idle low-power states vary from state to state. Generally speaking the power is less dependent on the voltage and frequency thus can often be treated as a constant. In Chapter 3 we discuss in details about the power consumed in idle low-power states.

#### 2.2.2 Memory

For modern memory architecture, memory power consists of memory background power, register/phase-lock loop (PLL) power, memory controller (MC) power and power associated with other activities such as activation/precharge, read/write, etc. Typically the background, register/PLL and MC account for 70 - 95% of the total memory power depending on the workloads [34].

Active low-power modes. Recently, researchers have proposed using DVFS to adjust the frequency of the memory [25, 12]. This involves adjusting the frequency of the memory bus, dual in-line memory modules (DIMMs), and dynamic random-access memory (DRAM) chips. Changing the frequency of the memory affects

the power and performance. Lowering the frequency increases the response time of the memory as it makes data burst longer on the memory bus. It also makes the MC slower thus results in large delay due to queuing effects. Lowering the frequency also leads to the linear reduction in the background and register/PLL power. Together with the frequency, it is also possible to reduce the voltage of the MC thus MC power can be reduced cubically. A detailed discussion on memory power and frequency relationship can be found in [34].

**Idle low-power states.** When a rank of DRAM chips is idle, all chips within that rank can be transitioned into idle low-power states. Different idle low-power states have different wake-up latencies. For example, the fast-exit precharge powerdown offers short wake-up latency but limited power savings while slow-exit precharge powerdown provides more power savings at longer wake-up cost.

Unlike in CPU, idle low-power states in memory are not often used as powering down an entire rank can be very costly [34]. To justify the powerdown, sufficiently long idleness for the entire rank should be observed, which rarely occurs in modern multi-core systems. As the result we do not consider idle low-power modes in memory in this thesis.

### 2.3 Performance metrics

Whenever low-power settings are changed, it is useful to quantitatively understand what aspect of the performance is affected and by how much. In this thesis, we mainly focus on two performance metrics: *response time* and *throughput*.

**Response time.** Response time is a random variable which measures the time a job spent in the system from its arrival to its departure. It consists of delays due to queuing and the service time of the job itself. The response time averaged across jobs is often called mean response time in queuing theory. The mean response time of the system indicates how much delay a job experiences on average.

However, mean response time only reflects the average behavior in the system. It is very likely for a system to have small mean response time yet with many jobs experiencing significant delay. Thus the probability of the response time exceeding a given threshold is also important; it gives quantitative measure on the performance of those outlier jobs. In Chapter 3, we demonstrate how response time is used to measure the performance of a server system.

**Throughput.** The throughput is the rate at which the system can finish its jobs. It measures the capacity of the system, i.e., how much work can be done within a given time interval. In Chapter 4 and Chapter 5, we demonstrate how we use throughput as the performance metric for multi-core systems.

## Chapter 3

### SleepScale

#### 3.1 Introduction

In this chapter, we introduce *SleepScale*, a low-power setting manager that jointly operates active low-power modes and idle low-power states for CPU. For active low-power modes, we consider a series of CPU DVFS settings. For idle low-power states, we consider various sleep states. Following the ACPI specification [2], we use  $C0_{(a)}$  to denote the processor operating mode. In this mode, DVFS settings can be adjusted. For sleep states, we consider  $C0_{(i)}$ , C1, C3 and C6 states. Different processor low-power settings are supported under different platform low-power settings (e.g.,  $S0_{(a)}$ ,  $S0_{(i)}$  and S3). In Table 3.1 and Table 3.2 we show the processor low-power settings and associated platform settings based on the Intel Xeon/Atom family of processors.

SleepScale uses a set of power management policies (i.e., the choice of DVFS setting and sleep states) for given workload under target quality-of-service (QoS) constraints. To develop effective policies we consider a system model that takes

| Setting           | Operation & Characteristics                                 |  |  |

|-------------------|-------------------------------------------------------------|--|--|

| C0 <sub>(a)</sub> | Operating active mode: there is work to do, voltage &       |  |  |

|                   | frequency setting adjusted dynamically by DVFS              |  |  |

| $C0_{(i)}$        | Operating idle state: there is no work to do, voltage &     |  |  |

|                   | frequency held constant at last DVFS setting                |  |  |

| C1                | Halt state: clock stops                                     |  |  |

| C3                | Sleep state: cache flushed, architectural state maintained, |  |  |

|                   | clock stopped                                               |  |  |

| C6                | Deep sleep state: architectural state saved to RAM,         |  |  |

|                   | voltage set to zero                                         |  |  |

Table 3.1: CPU low-power settings [1].

| Setting           | Operation & supported CPU state(s)           |

|-------------------|----------------------------------------------|

| S0 <sub>(α)</sub> | Active mode: associated with $C0_{(a)}$ only |

| ${\rm SO_{(i)}}$  | Idle state: associated with other CPU states |

| S3                | Sleep: RAM powered, associated with C6 only  |

Table 3.2: Platform low-power settings [2].

into account important QoS constraints and processor, platform, and workload characteristics (Section 3.2). Then, to develop engineering insight, we study the effectiveness of various policies for the aforementioned system model under idealized setting (Section 3.3). In contrast to some previous studies, we demonstrate that there is not a single optimal policy; the optimum policy heavily depends on QoS constraints, as well as on the characteristics of processor, platform, and workload. Through intensive simulation and analytic study, we observe that (1) there exists an optimal joint choice of frequency setting and sleep state; (2) the best sleep state depends on the performance constraint at low utilization; (3) the best sleep state also depends on the job size; (4) the delay to enter a sleep state should be jointly

| Components     | Operating               | Idle                                      | Sleep                          | Deep sleep                            | Deeper Sleep |

|----------------|-------------------------|-------------------------------------------|--------------------------------|---------------------------------------|--------------|

| CPU×1 [1]      | $130V^2 f W (C0_{(a)})$ | $75V^2 f W (C0_{(i)})$                    | 47V <sup>2</sup> W (C1)        | 22 W (C3)                             | 15 W (C6)    |

| Chipset×1 [1]  | 7.8 W                   | 7.8 W                                     | 7.8 W                          | 7.8 W                                 | 7.8 W        |

| RAM×6 [1]      | 23.1 W                  | 10.4 W                                    | 10.4 W                         | 10.4 W                                | 3.0 W        |

| HDD×1 [36]     | 6.2 W                   | 4.6 W                                     | 4.6 W                          | 4.6 W                                 | 0.8 W        |

| NIC×1 [37]     | 2.9 W                   | 1.7 W                                     | 1.7 W                          | 1.7 W                                 | 0.5 W        |

| Fan×1 [3]      | 10 W                    | 1 W                                       | 1 W                            | 1 W                                   | 0 W          |

| PSU×1 [3]      | 70 W                    | 35 W                                      | 35 W                           | 35 W                                  | 1 W          |

| Platform total | $120 W (S0_{(\alpha)})$ | $60.5  W  (\mathrm{SO}_{(\mathfrak{i})})$ | $60.5~W~(S0_{(\mathfrak{i})})$ | $60.5W(\mathrm{SO}_{(\mathfrak{i})})$ | 13.1 W (S3)  |

Table 3.3: Power consumption for different components in a computer system.

determined with frequency and (5) service time dependency on CPU frequency matters.

SleepScale selects the best combination of frequency and sleep states at runtime. It predicts the characteristics of given workload and determines the optimal power management policy with low overhead. While we note that accurately predicting the workload characteristics of a computing system (i.e., the utilization, service time and inter-arrival time distributions) is the key to effective runtime power management, we also demonstrate that simple prediction techniques can offer sufficient accuracy for real-world utilization traces.

# 3.2 System model

We now present a system model that accounts for both DVFS and sleep states. We later use the model to study performance and power consumption under various workloads.

#### Power model

We discuss how we model (i) the power consumed by the processor, (ii) the power consumed by peripheral (non-CPU) components such as DRAM, hard disk drive (HDD), network interface card (NIC), and (iii) the latencies involved in transitioning between power states.

First, consider processor power. A CPU in the active  $C0_{(\alpha)}$  mode (and also in the idling  $C0_{(i)}$  state) consumes dynamic power. Power consumption will be proportional to  $V^2f$ , where V is the supply voltage and  $f \in [0,1]$  is the DVFS clock frequency scaling factor. In our study, we choose a linear DVFS scenario, where both voltage and frequency are scaled linearly. This assumption falls within the scope of some existing processors (see the datasheet in [38]). Dynamic power consumption in  $C0_{(\alpha)}$  and  $C0_{(i)}$  will therefore scale cubically with frequency. In the sequel we consider only the frequency parameter f and assume V to be proportional to f. In sleep state C1 the clock signal is gated. Thus, only leakage power is consumed. Platform components also have low-power settings and each supports a subset of the CPU low-power settings. Table 3.2 lists the platform low-power settings and the CPU setting (or settings) that each supports.

The power consumption of the entire system is the sum of CPU power and platform power. In the following we use the term "state" or "low-power state" to encompass both CPU and platform modes and denote the combined states by concatenating their notations, e.g.,  $C0_{(i)}S0_{(i)}$ . Table 3.3 tabulates power consumption numbers for the Xeon family of CPUs and associated platform components. As an example, the power consumption in low-power state  $C0_{(i)}S0_{(i)}$  is  $75V^2f + 52.7$  W.

|            | C0 <sub>(a)</sub> | $\mathrm{CO}_{(\mathfrak{i})}$ | C1           | СЗ             | C6          |

|------------|-------------------|--------------------------------|--------------|----------------|-------------|

| $SO_{(a)}$ | 0 s               | _                              | _            | _              | _           |

| $SO_{(i)}$ | _                 | 0 s                            | $1-10~\mu s$ | $10-100~\mu s$ | 0.1 - 1  ms |

| S3         | _                 | _                              | _            | _              | 1 - 10 s    |

Table 3.4: Wake-up latencies for different states [3, 4].

Table 3.4 summarizes the delay incurred by the various possible states in returning to active operation. We note that while it is possible to consider a platform shut-down in which the entire system is turned off, the wake-up latency incurred will be enormous, and thus should be considered at a coarser time granularity than is the focus of this work.

#### Operation model

We assume jobs arrive at the system according to some random process with rate  $\lambda$  and are served based on the first-come-first-serve (FCFS) order. The server is equipped with a DVFS mechanism, which affect the service time. In active operation the clock frequency can be scaled by a factor  $f\in[0,1]$  and the time it takes to process each job is scaled correspondingly. For CPU-bound jobs, the resulting (scaled) service times are modeled as a random variable with mean  $\frac{1}{\mu f}$  where  $\mu$  is the max service rate. Setting the frequency to the maximum f=1 yields maximum processing speed  $\frac{1}{\mu}$  and setting f=0 stops the server from processing jobs, i.e., the server is in a clock-gated mode. For memory-bound jobs, the service time is modeled as independent of frequency, thus with mean  $\frac{1}{\mu}$ . Finally, we note that the "utilization" factor  $\rho=\frac{\lambda}{\mu}$  is the expected fraction of time the server has jobs to

process.

As discussed earlier, in active state  $C0_{(\alpha)}S0_{(\alpha)}$  power varies cubically in f; hence the power is  $P_0f^3$  for some maximum power  $P_0$ . The system also has n low-power states indexed by i,  $1 \le i \le n$ . Each time the server becomes idle it enters a sequence of low-power states, staying in each for a pre-set amount of time. The server enters state i some  $\tau_i$  seconds after its queue empties. Naturally,  $\tau_1 < \tau_2 < \ldots < \tau_n$ . Formally, the ith low-power state is characterized by the three-tuple  $(P_i, \tau_i, w_i)$  where:

- P<sub>i</sub> is the power consumed in state i,

- $\tau_i$  is the time at which the server enters state i, measured from the time the queue empties, and

- $w_i$  is the average wake-up latency that the system incurs to return to the active state  $C0_{(\alpha)}S0_{(\alpha)}$  from state i.

A job arrival interrupts the low-power state and wakes up the system from its current low-power state. We assume a job arrival immediately triggers the wake-up process, during which no job can be served. Deeper sleep states consume less power but take longer to wake up from so  $P_1 > P_2 > \dots P_n$  but  $w_1 < w_2 < \dots < w_n$ . For simplicity and conservative evaluation we assume the power consumption during the wake-up is the same as the power consumed in active operation.

The low-power states that we study include  $C0_{(i)}S0_{(i)}$ ,  $C1S0_{(i)}$ ,  $C3S0_{(i)}$ ,  $C6S0_{(i)}$  and C6S3. We also analyze sequences of pairs of low-power states such as entering

$C0_{(i)}S0_{(i)}$  first then C6S3, and also sequences many more low-power states, e.g., entering  $C0_{(i)}S0_{(i)}$ ,  $C1S0_{(i)}$ ,  $C3S0_{(i)}$ ,  $C6S0_{(i)}$  and C6S3 in sequence.

### 3.3 Workload-dependent Optimal Policy

In this section we study the model of Section 3.2 under the idealized assumptions of Poisson arrivals and exponentially distributed service times. We present our methodology for evaluating various policy choices and discuss engineering lessons.

### 3.3.1 Methodology

To evaluate a candidate policy we generate N=10,000 jobs and evaluate the policy at each possible frequency setting based on our model presented in Section 3.2. The simulated maximum frequency is f=1 and the minimum is the one that the system is barely stable, i.e.,  $f=\rho+0.01$  with step size of 0.01. (We take such a fine step size only to generate smooth plots, in a real system there would be about 10 distinct frequencies.) For policies that consist of a sequence of low-power states, when the processor queue empties the processor enters the low-power states one after another. The arrival of the next job wakes up the processor, incurring some latency. From our simulations we gather results on mean response time  $\mathbb{E}[R]$  and average power  $\mathbb{E}[P]$ . An example of our simulator is provided in Algorithm 1 for single low-power state with  $\tau_1=0$ . Simulating one policy, i.e., one frequency and low-power state combination takes on average 6.3 ms on an Intel i5 2.6 GHz machine using Matlab. This can take even less time when an optimized code is

### **Algorithm 1** Simulation under $\rho = \frac{\lambda}{\mu}$ and frequency f

```

1: Generate jobs with job size and inter-arrival time sampled from probability

distributions with mean \frac{1}{\mu f} and \frac{1}{\lambda} respectively (assuming CPU-bound).

2: for job j in 1 to N do

if job j arrives before j - 1 departs then

4:

Active += service time of j.

Delay of j = departure time of j - arrival time of j.

5:

6:

else

7:

Active += service time of j + wake-up latency.

Idle += arrival time of j - departure time of j-1.

8:

9:

Delay of j = service time of j + wake-up latency.

```

- 10: **end if**

- 11: end for

- 12: Compute delay by taking average of all j jobs.

- 13: Compute power by the ratio of active and idle periods.

dedicated to run Algorithm 1.

#### 3.3.2 Engineering lessons

We first consider  $\tau_1=0$ , i.e., whenever the server completes all jobs in its queue the server immediately enters a low-power state from the active state  $CO_{(\alpha)}SO_{(\alpha)}$ . Second, to investigate how job size effect the choice of policy, we consider two different sizes: "Google-like"  $(\frac{1}{\mu}=4.2~\text{ms})$  and "DNS-like"  $(\frac{1}{\mu}=194~\text{ms})$ . In Section 3.4.1, when we use traces from data centers for our analysis, the former is roughly the size of a Google web search job and the latter of a DNS look-up job (cf. Table 3.5). Unless otherwise specified, jobs are assumed to be CPU-bound (and thus service time scales linearly in frequency).

The average wake-up latencies for the system to return to the active  $C0_{(a)}S0_{(a)}$  state from various low-power states are set as follows. To wake-up from  $C1S0_{(i)}$  we

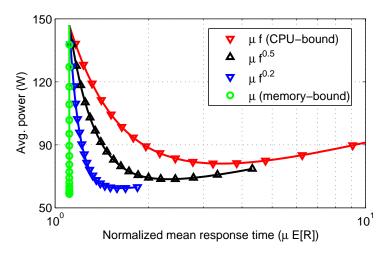

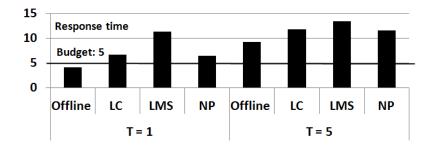

Figure 3.1: Mean response time  $\mathbb{E}[R]$  and average power  $\mathbb{E}[P]$  trade-off.

set the average latency to  $10~\mu s$ , from  $C3S0_{(i)}$  we set it to  $100~\mu s$ , from  $C6S0_{(i)}$  we set it to 1~m s, and from C6S3 we set it to 1~s. These values fall in the ranges specified in Table 3.4. We observe that other choices from the range specified do not greatly change the following engineering lessons.

We begin our engineering lesson by introducing Figure 3.1. In each sub-figure we plot average power consumption  $\mathbb{E}[P]$  as a function of two parameters. The first parameter is the mean response time  $\mathbb{E}[R]$  normalized by the average service time  $\frac{1}{\mu}$ . We normalize the mean response time in order to compare different workloads (with different average job sizes) directly. The second parameter is the DVFS frequency setting f. Selected choices of f are indicated by the hash marks on each curve. As f is changed the effective service rate  $\mu f$  varies proportionally. The left end of each curve is f=1, corresponding to the fastest processing, and hence smallest response time but most power. The right end of the curve is set by the smallest frequency under which the system is stable, roughly  $f=\rho$ , where  $\rho$  is the utilization. The hash marks are spaced uniformly in increments of 0.05.

We also evaluate systems based on Atom processors with the power numbers from [4]. While simulation results will not be shown, we will discuss our observations.

1) There exists an optimal joint choice of frequency setting and low-power state. Figure 3.1 plots the DNS-like and Google-like workloads results for  $\rho=0.1$ . We observe that there is an optimal joint choice of frequency setting and low-power state that yields the minimum power consumption. Without a constraint on the mean response time, the optimal choice corresponds to the bottom of the lowest

bowl. For example, in Figure 3.1-(a) the globally optimum policy uses C6S3 and f = 0.42 and runs at an average power of 70 W. Setting f too high leads to worsening efficiency since power increases cubically in frequency. But, setting it too small means that each job takes longer to complete, thereby reducing the possibility of entering a low-power state. The optimal choice – the policy at the bottom of the bowl – strikes a balance between these two effects. Policies such as "race-to-halt" [3] wherein the server runs at maximum frequency f = 1 until the queue empties and then immediately enters a single low-power state can consume 50% more power. Such a policy corresponds to the leftmost tip of each curve.

Due to small processor power and relatively large platform power, for Atom processors running DNS-like jobs at low utilizations, it is better to run fast and enter low-power state immediately after the job queue empties.

2) At low utilization, the best low-power state depends on the mean response time budget. In Figures 3.1 the left-hand side of the plots corresponds to a tight requirement on normalized mean response time. As the constraint is loosened different choices of policies and operating frequency settings become optimal. For example, in Figure 3.1-(a) under the tightest constraint (when the normalized mean response time  $\mu\mathbb{E}[R]$  is required to be in the range [1,2]) policies using  $C6S0_{(i)}$  are optimal; under a mid-range constraint policies using  $C0_{(i)}S0_{(i)}$  are the best; and under the loosest constraint policies using C6S3 prove to be the best. The intuition is as follows.

Consider the range of normalized mean response time for which  $C6S0_{(i)}$  is the best in Figure 3.1-(a). This is the best choice for the tightest response time

Figure 3.2: Optimal low-power states for Google and DNS-like workload under high utilization.

requirements because setting the frequency high results in faster job completion, thereby increasing the opportunities to enter a more aggressive power saving mode such as C6. On the other hand, under a looser constraint on response time the frequency can be lowered yielding the cubic decrease in power consumption. In this situation the expected duration of an empty queue is small and thus it becomes too costly to enter states like C6 that have high wake-up latencies. Thus  $C0_{(i)}S0_{(i)}$  outperforms  $C6S0_{(i)}$  in this situation. This observation is also valid for systems of Atom processors running Google-like workload.

3) The best power state depends on the job size. Figure 3.2 shows the optimal low-power states among other possible ones (not all shown) for servers under high utilization. When heavily utilized the server rarely exits the active operating state  $CO_{(\alpha)}SO_{(\alpha)}$ . This reduces opportunities to realize power savings by transitioning to a sleep state, thus most power savings must come from DVFS.

However the job size also plays a crucial rule in the optimal low-power state. For the DNS-like workload, policies using  $C6S0_{(i)}$  dominate since the wake-up latency of  $C6S0_{(i)}$  is negligible compared to average job size (194 ms). But, for Google-like workload the relatively small job size is sensitive to large wake-up latencies, thus policies using  $C3S0_{(i)}$  becomes optimal. For the same reason, very aggressive sleep states such as C6S3 should not be used for small size jobs or should be used only during extremely long idle period, "guarded" by workload prediction techniques [8]. Similar observations can also be made in Atom-based systems.

4) The delay  $\tau_i$  to enter a low-power state should be jointly determined with frequency. When a server becomes idle, it may wait some amount of time before entering a low-power state to avoid unnecessary wake-up costs [39]. Of course, for some low-power states with very small wake-up latencies, there is no need to delay the entrance as the wake-up incurs negligible penalty. However, for other low-power states with heavy wake-up penalties, it is not immediately clear how long the system should wait.

Figures 3.3 considers this situation and show what happens if we delay the entrance to state C6S3 by various amounts. In " $C0_{(i)}S0_{(i)} \rightarrow C6S3$ ", the server first enters  $C0_{(i)}S0_{(i)}$  immediately ( $\tau_1=0$ ) whenever the job queue empties and will enter C6S3 if it idles for some  $\tau_2$  seconds (recall the definition of  $\tau_i$  in Section 3.2). We compare policies using delayed C6S3 with ones using immediate C6S3 and immediate  $C0_{(i)}S0_{(i)}$ . We observe that the delay parameter  $\tau_2$  interpolates between the immediate C6S3 and  $C0_{(i)}S0_{(i)}$  curves: setting  $\tau_2=0$  reduces to immediate C6S3 and setting  $\tau_2=\infty$  reduces to immediate  $C0_{(i)}S0_{(i)}$ . From the plots we

Figure 3.3: Entering the second low-power state after delays for Google-like workload.

observe that by delaying C6S3, more power savings can be made at mild mean response time budget (e.g. consider  $\mu\mathbb{E}[R]=20$ ). Essentially, what we observe is that there is an optimal combination between frequency and entrance delay that minimizes the power under a certain mean response time constraint.

5) Sequential power throttle-back is conservative. It is tempting to concatenate all low-power states i.e., building a system with large number of low-power states and then letting the system enter those states in sequence to derive the most benefit from each. However from our intensive simulation on entering  $C0_{(i)}S0_{(i)}$ ,  $C1S0_{(i)}$ ,  $C3S0_{(i)}$ ,  $C6S0_{(i)}$  and C6S3 in sequence, we discover that such policies are not often efficient. The reason is that at high utilization the system rarely enters the last state. At low utilization it is a waste of power not to go to the optimal state immediately. Nevertheless, such sequential power reducing policies can be useful when the arrival statistics are unknown.

Figure 3.4: Comparison between different CPU usages for DNS-like workload.

6) Service time dependency on CPU frequency matters. Now we discuss what happens when the workload is *not* CPU-bound. Recall that for CPU-bound jobs the service rate  $\mu$  scales linearly with frequency f. For less CPU-bound jobs, the service rate scales sub-linearly and in the extreme case (memory-bound) service rate is insensitive to frequency (as job completion time is dominated by memory access time rather than processing time). In Figure 3.4 we plot a DNS-like workload at low utilization for service rate varying as different functions of clock frequency. It can be observed that the optimal choice of frequency depends on the scaling. For memory-bound jobs, the optimal speed is the lowest speed.

## 3.3.3 Analytic results

In fact, under the Poisson job arrival process and exponential service time distribution we can derive in closed-form the average power  $\mathbb{E}[P]$  and mean response time  $\mathbb{E}[R]$  for the system model described in Section 3.2. The results obtained from the

closed-form expressions match those presented in Figure 3.1. Note that constructing Figure 3.1 using closed-form expression does not involve simulations described in Section 3.3.1. The closed-form solution can also be derived when the service time follows general distributions, i.e., not limited to exponential distribution [35]. However for both general arrival process and service time distribution (which SleepScale assumes, as will be discussed next), no closed-form solution exists to the best of our knowledge. We include these theoretical results in the Appendix A for reference.

## 3.4 SleepScale design

In this section we present SleepScale, a runtime power management algorithm. It consists of a policy manager and a runtime predictor. First, in Section 3.4.1 we detail the policy manager that selects the optimum policy as a function of workload statistics. Second, in Section 3.4.2 we describe our runtime predictor of the statistical characteristics of the workload such as utilization, and arrival rate and service time distributions. This allows SleepScale to select the best policy in an online manner.

### 3.4.1 Policy manager

In this section we describe the policy manager. The manager takes a statistical description of the current workload as input and determines the best policy.

#### Policy characterization and selection.

The policy manager bases its determination of the best policy on the empirically observed distributions of recent arrivals and service times, collected from the server at runtime. The observed recent arrivals and service times can be arbitrary statistics, not limited to Poisson process and exponential distributions. Given the collected statistics it characterizes the power-performance trade-off of each low-power state at a range of frequency settings. It does this by simulating the queuing process as described in Algorithm 1. The optimal policy is the policy that minimizes power consumption while meeting a target QoS constraint. As noted in Section 3.3.1, simulating a single policy takes only 6 ms. Considering the finite number of frequencies and low-power states, the overhead of simulating all policies is thus negligible compared to the policy updating period (which will be measured in minutes, as discussed later).

Our QoS constraint is determined by a baseline system. Our baseline is motivated by the fact that data centers are often provisioned to meet a QoS target for some peak demand, often specified in an SLA. To meet SLA commitments during periods of peak demand, the data center should be running full out, i.e., at maximum frequency f = 1 without using a low-power state. In contrast, at lower loads there is slack in meeting the QoS which can be exploited to reduce operating costs (e.g., power) as much as possible.

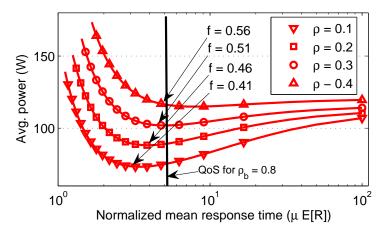

We parameterize the target peak demand through a peak design utilization  $\rho_b$ . To understand the baseline QoS, consider Figure 3.5. This figure plots the power-delay trade-off for the Google-like workload running with low-power state

Figure 3.5: Average power/performance trade-off for Google-like workload.

$C0_{(i)}S0_{(i)}$  at different frequency settings and under different utilizations  $\rho < \rho_b$ . In the plot the baseline QoS throughput constraint is indicated by the vertical bar. This vertical bar indicates that the allowable normalized response time is 5 when  $\rho_b = 0.8$ , calculated (under the idealized model) as  $\mu\mathbb{E}[R] = \frac{1}{(1-\rho_b)} = \frac{1}{1-0.8} = 5$ . In general as the utilization  $\rho$  is increased from  $\rho = 0$  to  $\rho = \rho_b$  the curves shift up, meaning that a higher frequency setting is required to maintain the QoS throughput constraint. For instance, for  $\rho = 0.4$ , which is strictly less than  $\rho_b = 0.8$ , to minimize average power one must set f = 0.56 and the system will operate exactly at the requisite QoS. However, for even lower utilizations, e.g,  $\rho = 0.1$ , one operates at the lowest average power by setting f = 0.41. This is the global minimum for this utilization and the normalized mean response time achieved is about 3, which exceeds the QoS requirement. Thus, one can sometimes exceed the baseline QoS while minimizing power consumption.

| Workload | Inter-arrival | Inter-arrival | Service | Service   |

|----------|---------------|---------------|---------|-----------|

|          | Mean          | $C_{v}$       | Mean    | $C_{\nu}$ |

| DNS      | 1.1 s         | 1.1           | 194 ms  | 1.0       |

| Mail     | 206 ms        | 1.9           | 92 ms   | 3.6       |

| Google   | 319 μs        | 1.2           | 4.2 ms  | 1.1       |

Table 3.5: Different workload types from [5] (partial list).

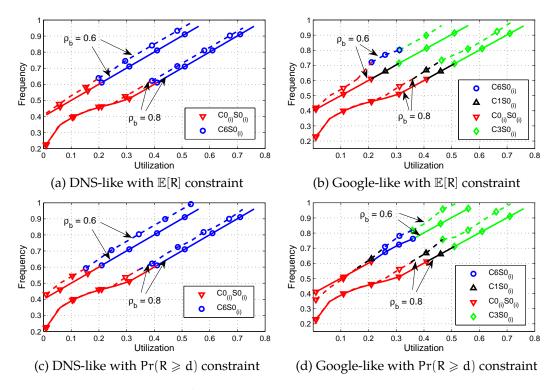

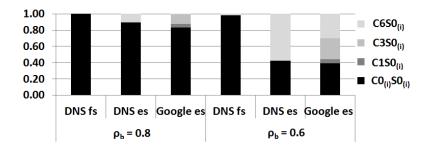

Figure 3.6: Policy selection for DNS and Google-like workloads. Each curve plots the optimal pairing of frequency setting and low-power states as a function of utilization  $\rho$ , and parameterized by QoS constraint  $\rho_p$ . The different markers (see legend) indicate which low-power state is optimal at each utilization. The solid lines represent what an idealized model computes and dashed lines represent the results using real-world workload statistics.

#### Results and observations.

We now present the results of our policy characterization according to the workload statistics used by the BigHouse [5] simulator. The BigHouse simulator stores statistics of inter-arrival and service times accumulated from long-term observation of live traffic traces for various real-world workloads. Table 3.5 lists summary statistics (inter-arrival and service time mean and coefficient of variation  $(C_{\nu})$ ) of three workloads in the BigHouse simulator.

Figure 3.6 shows the optimum policy as a function of workload, utilization, and QoS constraint ( $\rho_b$ ). As an example, Figure 3.6-(a) plots the optimum policy for the DNS-like workload. Operating frequency is indicated on the vertical axis, utilization on the horizontal axis, and the optimum choice of low-power state by the hash marks is indicated in the legend. Depending on the utilization two different policies become optimal. At low utilization  $C0_{(i)}S0_{(i)}$  is optimal and at high utilization  $C6S0_{(i)}$  is optimal. Two pairs of curves are plotted. The upper two curves are plotted for a baseline QoS constraint set by  $\rho_b = 0.6$ , the bottom two for  $\rho_b = 0.8$ . Note that the constraint under  $\rho_b = 0.6$  is *tighter* than the one under 0.8. In each pair of curves one is dashed, meaning it is the policy choice based on the statistics of the BigHouse simulator for that particular workload. The other curve is solid, meaning that it is the optimum policy choice computed by the model considered in Section 3.3 (i.e., Poisson job arrivals and exponential service times) with the same mean inter-arrival and service time as its paired BigHouse curve.

The plots in the second row of Figure 3.6 are defined analogously except that the QoS is measured in terms of the 95th percentile response time, rather than in terms

of normalized mean response time. Each sub-plot in the second row shares the same workload as the plot directly above. We summarize key observations below.

- 1) There is no "one-size-fits-all" policy. Different workloads and different utilizations require different policies. Almost all low-power states are useful for some set of operating conditions. Thus, relying on a single low-power state when designing power-efficient architectures can be a poor choice.

- 2) The idealized model is sometimes good, but often one needs to use more realistic models. Recall that the model of Section 3.3 is limited to idealized Poisson job arrivals and exponential service times. These are analytically tractable distributions and when they closely match the actual workload statistics policies based on those results can perform almost as well as the policies based on actual statistics.

We also note that the discrepancy between the policy results based on the idealized model and the BigHouse model is different for two performance constraints; cf. Figures 3.6-(c) and -(d). This is due to the fact that while the mean response time is only concerned with the mean, the 95th percentile response time constraint is concerned with the tail behavior of the response time distribution, which depends critically on the variation in job size and inter-arrival time.

3) Often the idealized model computes the best choice of low-power state, but not the frequency setting. Often for a given utilization the computed optimal low-power state is the same but the frequency setting computed by the idealized model is lower than the one computed by BigHouse. If there is a way to adjust the frequency in runtime, one can rely simply on the idealized model without simulation to compute the optimal policy. We leave this as a part of our future

work.

4) The bump in low utilization region indicates that the policy is exceeding its QoS constraint. At low utilization, the optimal frequency curve for  $CO_{(i)}SO_{(i)}$  often has a concave shape. The consistency of this shape can be explained by referring back to Figure 3.5. As was observed earlier, at low utilizations the QoS constraint can be exceeded while reaching the global minimum power (optimized across all frequencies). In terms of Figure 3.5 this means that the systems is operating strictly to the left of the vertical bar. Since the same model underlies the policy optimization based on the idealized and BigHouse models, the global power minimum will be the same for both. For this reason the BigHouse and idealized curves can overlap at low enough utilizations.

As the utilization increases, the optimal frequency setting also increases to keep the power at the global minimum. However beyond some utilization level (roughly  $\rho=0.3$  in Figure 3.5) the lowest power will no longer continue to meet the target performance constraint. At that level the frequency needs to increase more quickly to continue to meet the constraint. Above that utilization levels the  $C0_{(i)}S0_{(i)}$  curves in Figure 3.6 transition into their respective linear regimes. Since the  $\rho_b=0.6$  constraint is *tighter* than the  $\rho_b=0.8$  constraint and so in curves with arrow " $\rho_b=0.6$ " in Figure 3.6 we see no evidence of the bump.

## 3.4.2 Runtime predictor

The runtime predictor works epoch by epoch, predicting for the current epoch two important aspects of the workload based on its history: 1) inter-arrival time and

#### Algorithm 2 Pseudo-code for utilization predictor

```

1: Initialize history depth hist.

2: Initialize a weight vector of size p = hist: \mathbf{v} = \{v(1), \dots v(p)\}. Set each of the p

entries to 1/\mathfrak{p}.

3: while prediction for \rho(t) do

\{// \text{ Predict the utilization at time t, } \rho'(t) \text{ using LMS:} \}

Predict \rho'(t) = \min[\sum_{i=1}^{p} \nu(i)\rho(t-i), 1] from the past p utilization values.

5:

Compute error = |\rho(t) - \rho'(t)|.

6:

Update weight v based on error and \rho(t-1:t-p).

7:

if error is larger than some adaptive threshold then

8:

9:

{// CUSUM test:}

Reset p = 1 and set v(1) = \text{sum}(\mathbf{v}).

10:

else

11:

```

Grow p, p = min(p = p + 1, hist) and set  $v(i) = \text{sum}(\mathbf{v})/p$  for all  $1 \le i \le p$ .

service time statistics and 2) utilization. Each epoch is a T minutes long (T  $\geqslant$  1) time period. The prediction is fed into the policy manager. The policy is updated at the beginning of each epoch and is held constant throughout the epoch.

#### Distribution prediction.

12:

13:

14:

end if

15: end while

t = t + 1

The inter-arrival time and service time distributions are predicted based upon jobs events logged in previous epochs. The logs we collect detail the arrival and service times of each jobs. These logged statistics are scaled by the predicted utilization (to be discussed later) and fed into the policy manager. Using Algorithm 1 the policy manager then computes the predicted power consumption and QoS of each candidate policy and then selects the policy to use. Note that since we have already obtained the workload log, generating jobs by sampling the distribution (step 1 in

Algorithm 1) is not needed. Logging all job events is not necessary either: average behavior from the past several epochs will suffice.

Implicitly the predictor predicts the inter-arrival time and service time distributions based on the past epochs. The motivation for working with the logged arrival and service times is that constructing, maintaining and updating a fine-grained distribution histogram and simulation via sampling is expensive in both time and space. Thus we find it is effective to use logs from previous epochs without explicitly building a distribution. As shown in Section 3.3.1, it takes only 6.3 ms for evaluating one single policy. The policy manager only needs to determine the best policy *once* every epoch. Since, e.g., in the results of Section 3.5 epochs will be in minutes-length and the determination of the best policy takes less than 1 s to compute, the computational overhead is negligible.

#### Utilization prediction.

The distribution predictor predicts the statistics based on the recent epochs. We further enhance such prediction by a fine-grained, minute-by-minute utilization prediction. The workload log gathered in Section 3.4.2 used to simulate the policies is adjusted based on the predicted utilization of the upcoming epoch (the first minute of the epoch, by default): the empirical inter-arrival times between jobs are scaled to match the upcoming predicted utilization.

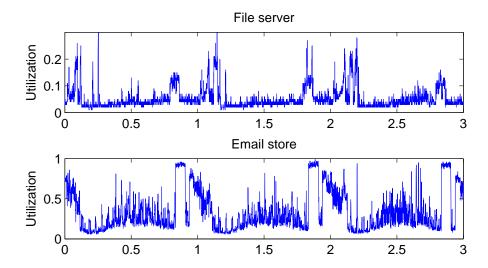

There is a large body of literature on utilization prediction; much is based on pattern matching [40] across days. As an illustration, in Figure 3.7 we plot several days worth of minute-granularity utilization traces from academic departmental servers.

Figure 3.7: Utilization traces plotted across 3 days for different services. Both start at 12 AM of a day. Email store is the host for student, faculty and staff email storage. File server is the host for student files [7, 8].

We observe a periodic daily pattern to the utilization. The abrupt surges observed towards the end of each day in the email store workload, are due to maintenance and back-up services. In contrast to the earlier work based on pattern matching, we study fine-grained minute-by-minute fluctuations in workload behavior. Our approach lets the policy manager react at the processor level to real-time fluctuations in the workload. Our examination will reveal some fundamental aspects of what constitutes good prediction and how the predictor should interact with the selected policy.

In SleepScale we implement three different utilization predictors: a naive-previous predictor, a least-mean-square adaptive filter (LMS) [41], and an LMS filter in conjunction with a cumulative sum change point detection (LMS+CUSUM) [42].

The naive-previous predictor simply uses the utilization in the last minute of

the past T-minute epoch as the prediction for the current epoch. This predictor is best suited to track sudden changes in utilization, however it does not effectively predict the stationary behavior of the workload.

The LMS adaptive filter predicts the utilization based on a weighted combination of the utilizations observed over the past p minutes. The weights are updated every minute based on the prediction error. The LMS adaptive filter outperforms the moving average predictor (which would take the average utilization over the past p minutes) because the weight for each of the past p minutes is chosen adaptively, rather than being fixed to a constant 1/p. However, like the moving average predictor the LMS filter smoothes the data, it does not track abrupt changes well.

As an intermediary between naive-previous predictor and LMS filter, LMS+CUSUM does both tracking and stationary behavior prediction. The pseudo-code of this LMS+CUSUM is given in the Algorithm 2 box. When the CUSUM algorithm detects an abrupt change, the look-back period p in the LMS is reset to 1 (cf. line 10). This resetting drops the smoothing effect of LMS and allows the filter to track the change better. As long as no further abrupt change is detected, p grows until some maximum value is reached (cf. line 12).

#### Dynamic frequency over-provisioning.

The utilization predicted for the first minute of the upcoming T-minute epoch is used to scale the workload log for the entire epoch. The larger T is, the less likely the prediction will be a good one for the entire T-minute epoch. If the predictor overestimates the utilization realized in the epoch, jobs will be processed faster and

the queue will tend to empty. However, if the predictor underestimates the realized utilization, the queue will back up, and large delays may result, delays that can propagate into subsequent planning epochs. To control for this in SleepScale we implement the following over-provisioning mechanism.